Document Number: 002-00497 Rev. *E Page 17 of 90

S25FL116K, S25FL132K, S25FL164K

3.3.3 Interface Standby

When CS# is high the SPI interface is in standby state. Inputs are ignored. The interface waits for the beginning of a new command.

The next interface state is Instruction Cycle when CS# goes low to begin a new command.

While in interface standby state the memory device draws standby current (I

SB

) if no embedded algorithm is in progress. If an

embedded algorithm is in progress, the related current is drawn until the end of the algorithm when the entire device returns to

standby current draw.

3.3.4 Instruction Cycle

When the host drives the MSB of an instruction and CS# goes low, on the next rising edge of SCK the device captures the MSB of

the instruction that begins the new command. On each following rising edge of SCK the device captures the next lower significance

bit of the 8-bit instruction. The host keeps CS# low, HOLD# high, and drives Write Protect (WP#) signal as needed for the

instruction. However, WP# is only relevant during instruction cycles of a Write Status Registers command and is otherwise ignored.

Each instruction selects the address space that is operated on and the transfer format used during the remainder of the command.

The transfer format may be Single, Dual output, Quad output, Dual I/O, or Quad I/O. The expected next interface state depends on

the instruction received.

Some commands are stand alone, needing no address or data transfer to or from the memory. The host returns CS# high after the

rising edge of SCK for the eighth bit of the instruction in such commands. The next interface state in this case is Interface Standby.

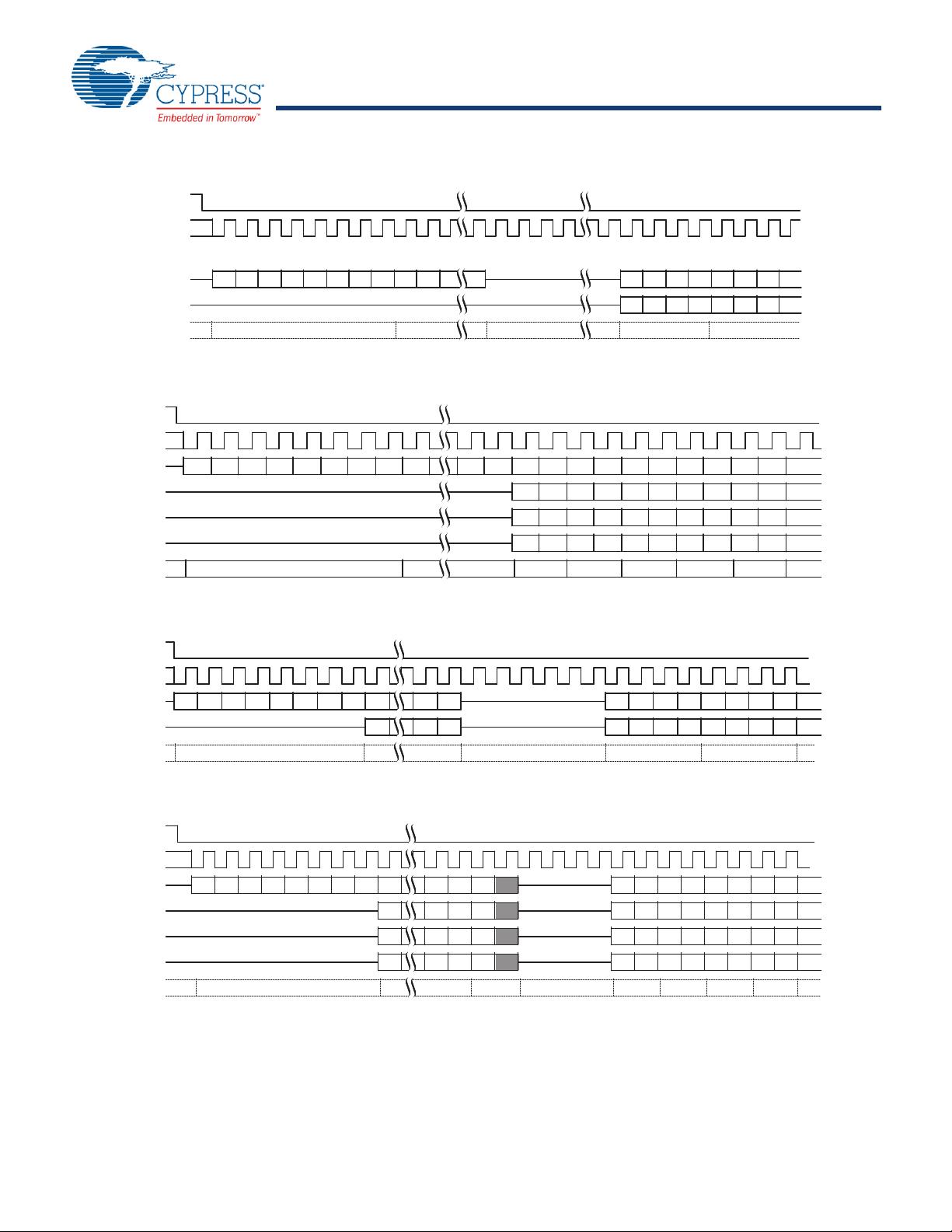

3.3.5 Hold

When Quad mode is not enabled (SR2[1]=0) the HOLD# / IO3 signal is used as the HOLD# input. The host keeps HOLD# low, SCK

may be at a valid level or continue toggling, and CS# is low. When HOLD# is low a command is paused, as though SCK were held

low. SI / IO0 and SO / IO1 ignore the input level when acting as inputs and are high impedance when acting as outputs during hold

state. Whether these signals are input or output depends on the command and the point in the command sequence when HOLD# is

asserted low.

When HOLD# returns high the next state is the same state the interface was in just before HOLD# was asserted low.

3.3.6 Single Input Cycle — Host to Memory Transfer

Several commands transfer information after the instruction on the single serial input (SI) signal from host to the memory device. The

dual output, and quad output commands send address to the memory using only SI but return read data using the I/O signals. The

host keeps CS# low, HOLD# high, and drives SI as needed for the command. The memory does not drive the Serial Output (SO)

signal.

The expected next interface state depends on the instruction. Some instructions continue sending address or data to the memory

using additional Single Input Cycles. Others may transition to Single Latency, or directly to Single, Dual, or Quad Output.

3.3.7 Single Latency (Dummy) Cycle

Read commands may have zero to several latency cycles during which read data is read from the main flash memory array before

transfer to the host. The number of latency cycles are determined by the instruction. During the latency cycles, the host keeps CS#

low, and HOLD# high. The Write Protect (WP#) signal is ignored. The host may drive the SI signal during these cycles or the host

may leave SI floating. The memory does not use any data driven on SI / I/O0 or other I/O signals during the latency cycles. In dual or

quad read commands, the host must stop driving the I/O signals on the falling edge at the end of the last latency cycle. It is

recommended that the host stop driving I/O signals during latency cycles so that there is sufficient time for the host drivers to turn off

before the memory begins to drive at the end of the latency cycles. This prevents driver conflict between host and memory when the

signal direction changes. The memory does not drive the Serial Output (SO) or I/O signals during the latency cycles.

The next interface state depends on the command structure i.e. the number of latency cycles, and whether the read is single, dual,

or quad width.