Verilog非阻塞赋值深入解析:仿真与综合

需积分: 10 46 浏览量

更新于2024-08-01

收藏 163KB DOC 举报

"本文主要探讨了Verilog编程中非阻塞性赋值(non-blocking assignments, NBA)的应用和理解,特别是在仿真和综合过程中的问题。文章由Clifford E. Cummings撰写,旨在帮助工程师们更好地掌握何时使用非阻塞赋值,并提供了编码指导原则以确保代码能够被正确综合,同时避免仿真中的竞争条件。"

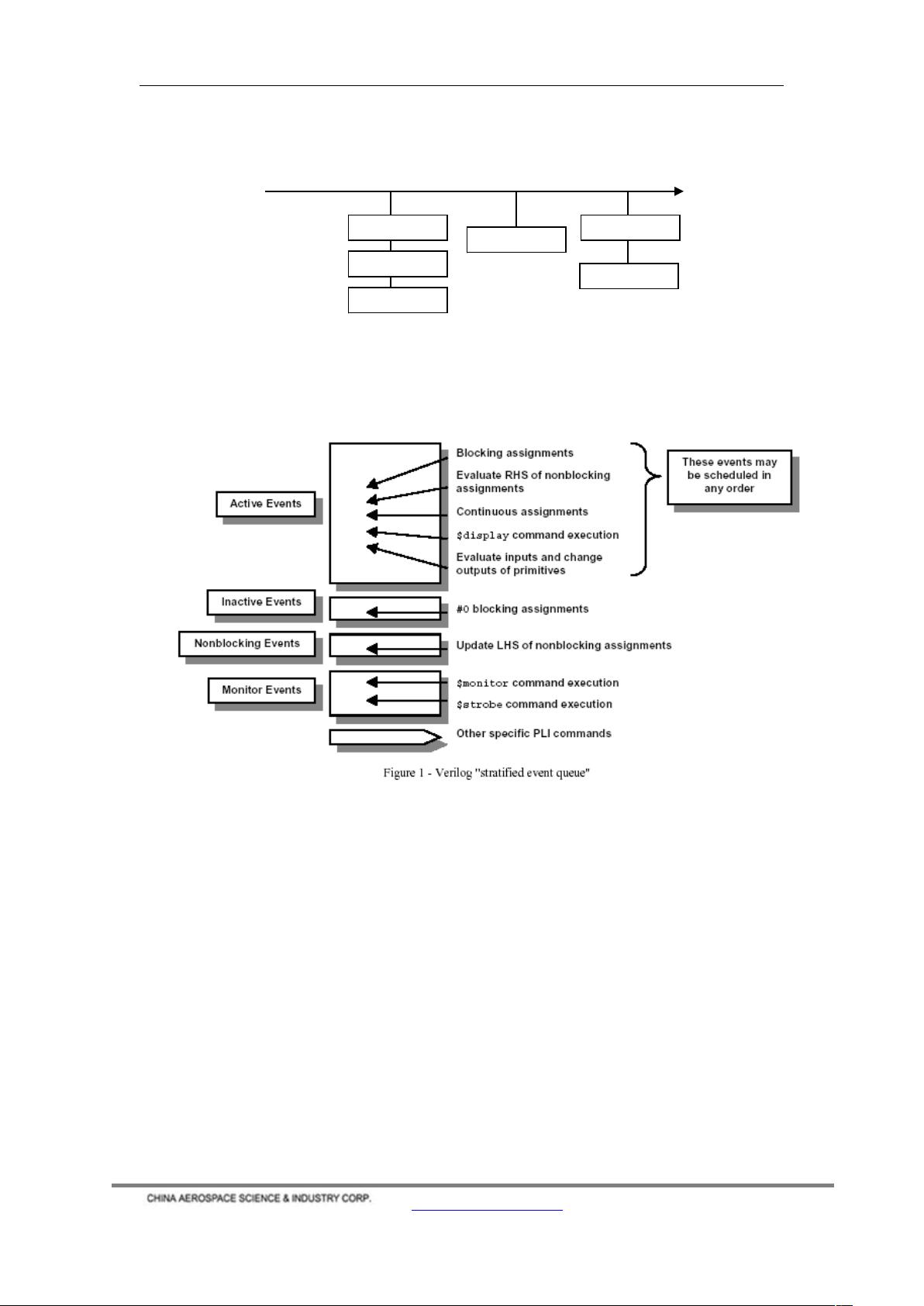

在Verilog中,非阻塞赋值(<=)和阻塞赋值(=)是两种关键的赋值操作,它们在逻辑建模中扮演着不同的角色。传统的指导原则建议,在always块中,使用阻塞赋值来创建组合逻辑,而使用非阻塞赋值来构建时序逻辑。阻塞赋值在执行时会立即更新变量的值,而非阻塞赋值则会在当前时钟事件的末尾更新,这使得它更适合于描述触发器和其他存储元件的行为。

非阻塞赋值在仿真中的行为与实际硬件更接近,因为它们反映了数据的延迟特性。当多个非阻塞赋值在同一个时钟边缘作用于同一个变量时,Verilog仿真器会按照它们在代码中的顺序来处理这些赋值,这种现象被称为"左到右"(left-to-right)的赋值顺序。然而,这种顺序在实际电路中并不总是保持不变,因此可能导致仿真和综合结果之间的差异。

文章深入讨论了Verilog仿真中的竞争条件,这是由于多个赋值在同一时间作用于同一变量导致的不确定性。IEEE Verilog标准定义了“保证性的赋值描述”和“非保证性的赋值描述”,并规定了如何处理这些情况。避免竞争条件的一个关键方法是在编写代码时遵循良好的编码风格,例如,避免在敏感列表相同的always块中混合使用阻塞和非阻塞赋值。

为了正确地综合Verilog代码,设计师应遵循以下几点建议:

1. 在组合逻辑中,使用阻塞赋值以确保正确的逻辑顺序。

2. 对于寄存器和触发器,使用非阻塞赋值,以反映硬件中的延迟特性。

3. 避免在同一always块中混合使用阻塞和非阻塞赋值,除非你清楚地理解其行为。

4. 了解非阻塞赋值在不同类型的always块(如 @(posedge clk) 和 always_comb)中的行为差异。

5. 在设计中使用清晰的逻辑层次,以减少潜在的竞争条件。

通过理解和遵循这些原则,工程师可以编写出更易于综合且行为预测准确的Verilog代码,从而减少设计错误和后期修改的需求。对于那些想要深入理解Verilog语言的人来说,理解和熟练应用非阻塞赋值是至关重要的一步。

2010-04-29 上传

2008-12-18 上传

2008-10-24 上传

2008-03-15 上传

2009-02-12 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

laocheng826

- 粉丝: 0

- 资源: 3

最新资源

- 单片机串口通信仿真与代码实现详解

- LVGL GUI-Guider工具:设计并仿真LVGL界面

- Unity3D魔幻风格游戏UI界面与按钮图标素材详解

- MFC VC++实现串口温度数据显示源代码分析

- JEE培训项目:jee-todolist深度解析

- 74LS138译码器在单片机应用中的实现方法

- Android平台的动物象棋游戏应用开发

- C++系统测试项目:毕业设计与课程实践指南

- WZYAVPlayer:一个适用于iOS的视频播放控件

- ASP实现校园学生信息在线管理系统设计与实践

- 使用node-webkit和AngularJS打造跨平台桌面应用

- C#实现递归绘制圆形的探索

- C++语言项目开发:烟花效果动画实现

- 高效子网掩码计算器:网络工具中的必备应用

- 用Django构建个人博客网站的学习之旅

- SpringBoot微服务搭建与Spring Cloud实践