4 1 Embedded Systems Design

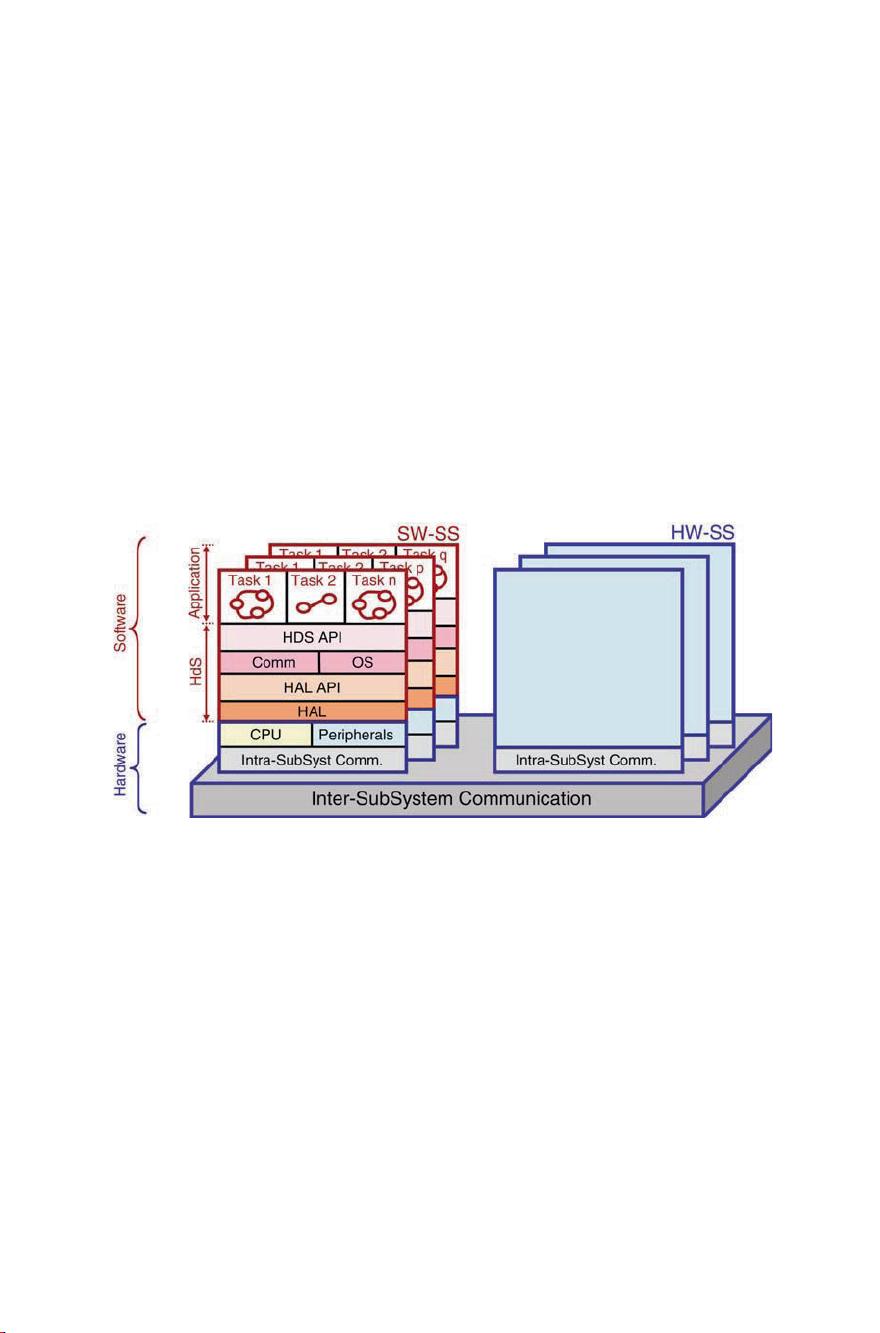

(Comm), and the hardware abstraction layer (HAL). These different components

are based on well-defined primitives or application programming interfaces (APIs)

in order to pass from one software layer to another.

A hardware subsystem represents specific hardware component that implements

specific functionalities of the application or a global memory subsystem accessible

by the processing units.

The shift from the single processor to an increasingly processor- and multi-

processor-centric design style poses many challenges for system architects, software

and hardware designers, verification specialists, and system integrators. The main

design challenges for MPSoC are as follows: programming models that are required

to map application software into effective implementations, the synchronization

and control of multiple concurrent tasks on multiple processor cores, debugging

across multiple models of computation of MPSoC and the interaction between the

system, applications, and the software views, and the processor configuration and

extension [96].

Current ASIC design approaches are hard to scale to a highly parallel multi-

processor SoC [88]. Designing these new systems by means of classical methods

gives unacceptable realization costs and delays. This is mainly because different

teams contributing to SoC design used to work separately. Traditional ASIC design-

ers have a hardware-centric view of the system design problem. Similarly, software

designers have a software-centric view. System-on-chip designs require the creation

and use of radical new design methodologies because some of the key problems in

SoC design lie at the boundary between hardware and software. Current SoC design

process uses in most cases two separate teams working in a serial methodology to

achieve hardware and software designs, while some SoC designers already adopted

a process involving mixed hardware–software teams, and others try to move slowly

in this direction.

The use of heterogeneous ASIPs makes heterogeneous MPSoC architectures fun-

damentally different from classic general-purpose multi-processor architectures. For

the design of classic computers, the parallel programming concept (e.g., MPI) is

used as an application programming interface (API) to abstract hardware/software

interfaces during high-level specification of software applications. The application

software can be simulated using an execution platform of the API (e.g., MPICH) or

executed on existing multi-processor architectures that include a low-level software

layer to implement the programming model. In this case, the overall performances

obtained after hardware/software integration cannot be guaranteed and will depend

on the match between the application and the platform.

Unlike classic computers, the design of MPSoC requires a better matching

between hardware and software in order to meet performance requirements. In this

case, the hardware/software interfaces implementation is not standard; it needs to be

customized for a specific application in order to get the required performances. This

includes customizing the CPUs and all the peripherals required to accelerate com-

munication and computation. In most cases, even the lower software layers need to

be customized to reach the required cost and performance constraints. Applying

the classical design schemes for those architectures leads to inefficient designs.