高速系统设计中的串扰分析及其影响

需积分: 10 40 浏览量

更新于2024-09-12

收藏 707KB PDF 举报

高速电路中的串扰分析是信号完整性领域的重要课题,特别是在现代高速数字系统设计中,随着时钟频率的提升,信号完整性问题愈发显著。串扰现象不仅存在于芯片内部的布线,还可能出现在印刷电路板(PCB)、接插件和通信电缆等各个层次,对系统性能的稳定性产生重大影响。

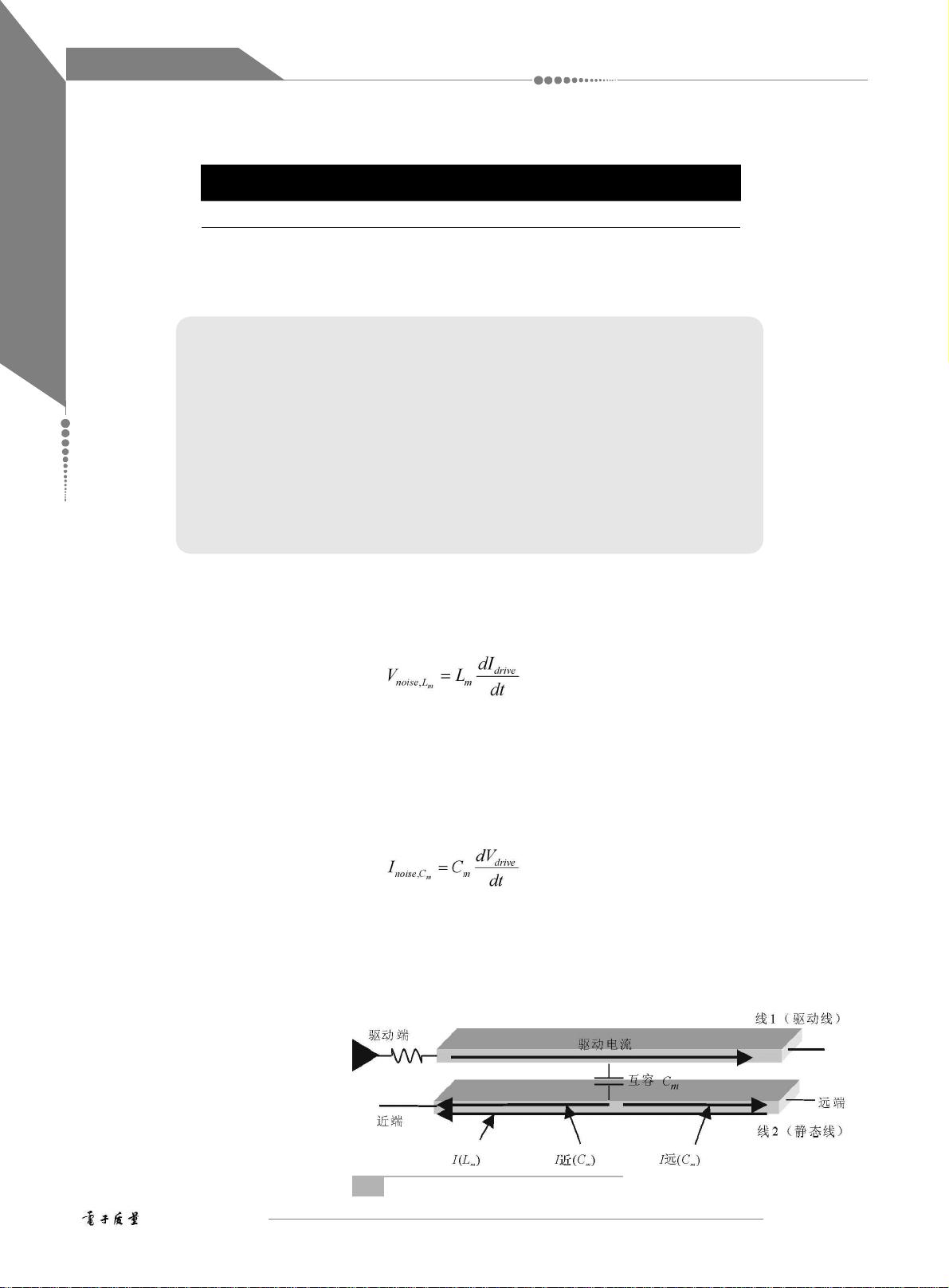

串扰的产生主要源于两种机制:互感和互容。互感(Lm)是指驱动线上的磁场在静止线路上激发电流,当静态线路接近驱动线时,会产生与驱动线电流变化率成正比的电压噪声。互容(Cm)则表现为两个导体间的电场耦合,导致静态线上出现与驱动线电压变化率成正比的电流噪声。这些噪声在高速系统中不容忽视,因为它们可能导致信号失真,甚至数据传输错误。

在串扰的分类上,可分为近端串扰(Backplane Crosstalk)和远端串扰(Front-end Crosstalk)。近端串扰发生在静态线靠近驱动端的一端,也称为后向串扰;远端串扰则来自远离驱动端的一端,被称为前向串扰。互感造成的电流方向与原电流相反,而互容则使得电流在静态线两端分流。通过这些表达式(3)和(4),我们可以量化不同端点的串扰电流及其带来的噪声。

理解串扰的机理并采取有效的设计策略至关重要。这包括合理布局电路、优化信号路径、使用屏蔽技术、选择低串扰的组件材料,以及采用时序设计技巧来降低串扰影响。此外,仿真工具在串扰分析中扮演着核心角色,通过电磁场模拟和信号完整性分析软件,设计师可以预测和优化系统的性能,确保高速数字系统在实际应用中具有良好的信号质量。

高速电路中的串扰分析是提升系统效能的关键环节,它要求设计师具备深入理解互感和互容原理的能力,并能够采取适当的措施来控制和减少串扰带来的负面影响。随着技术的发展,这一领域的研究将不断进步,以适应越来越高的数据传输速度和更严苛的信号完整性标准。

257 浏览量

119 浏览量

125 浏览量

2020-10-18 上传

199 浏览量

365 浏览量

199 浏览量

157 浏览量

269 浏览量

huang06680755

- 粉丝: 0

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程