微处理器的硬件结构:流水线与超标量详解

需积分: 13 41 浏览量

更新于2024-07-29

收藏 1.02MB PDF 举报

微处理器的硬件结构是现代计算机系统的核心组成部分,它决定了计算机的性能和效率。在本课程中,由陆俊林和王箫音教授在2012年春季学期的第九讲中,深入探讨了北京大学信息科学技术学院和北京大学微处理器研发中心的研究内容,涵盖了微处理器的多方面细节。

首先,课程从微处理器的总体结构开始,这是理解所有高级功能的基础,包括处理器内核、逻辑电路、接口和电源管理等元素的布局和连接。这部分内容通常基于《微型计算机基本原理与应用(第二版)》的第7章,该章节详述了处理器如何执行指令、处理数据以及与其他部件协同工作。

接着,课程重点讨论了高速缓存的设计,这是为了提高处理器与内存之间的数据交换速度,通过减少访问延迟来提升整体性能。高速缓存的工作原理,包括L1、L2和L3等不同层次,以及它们在流水线和超标量设计中的作用被深入剖析。

流水线是微处理器的核心概念,它通过分解指令执行步骤,使多个操作可以并发进行,从而提高执行效率。流水线模式的介绍包括指令获取、解码、执行、写回等阶段,以及潜在的瓶颈如数据 hazards 和分支预测技术,这些都对提升处理器性能至关重要。

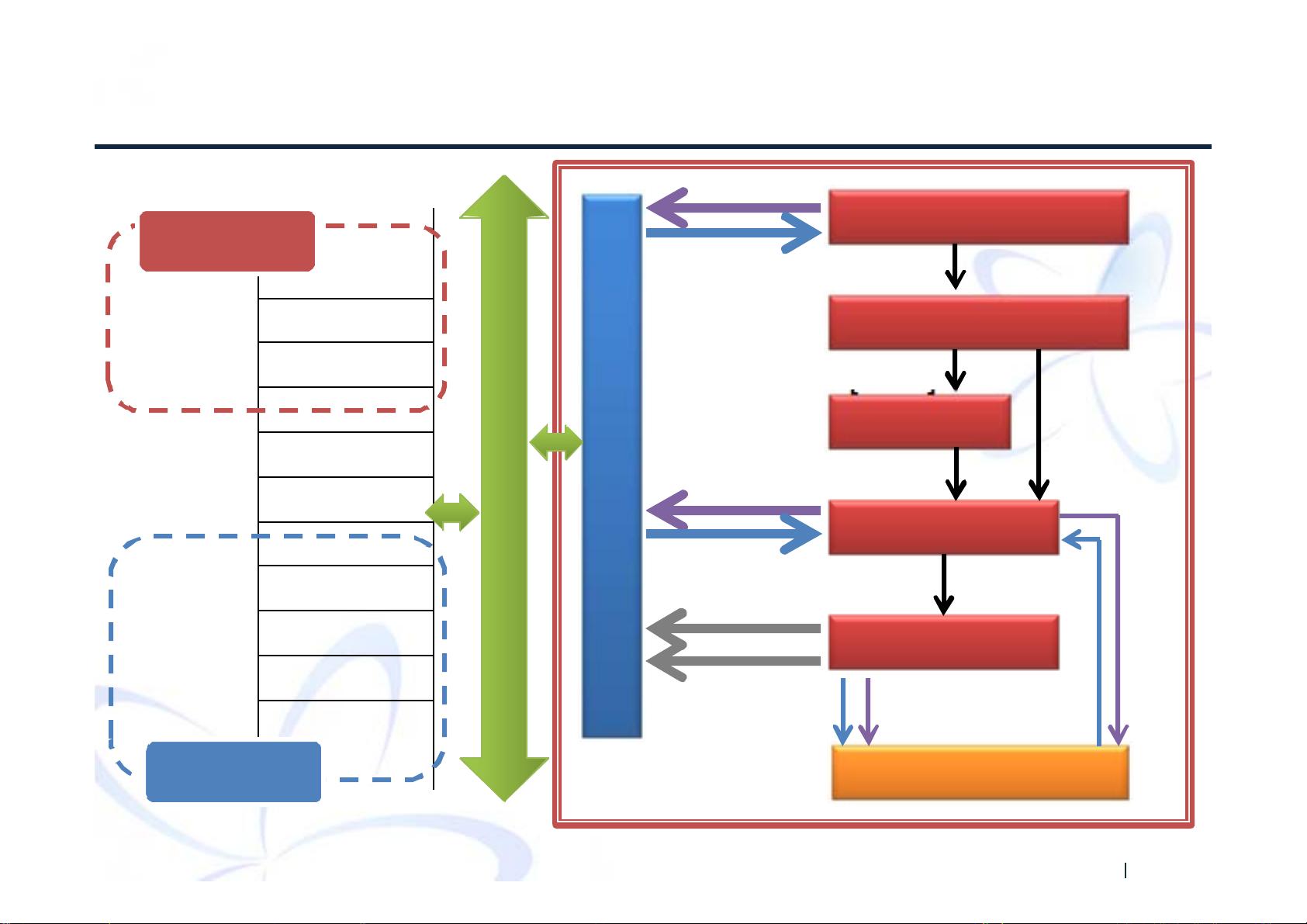

超标量流水线是进一步提升并行处理能力的技术,它在单个时钟周期内同时执行多个指令,增加了指令级并行性。Pentium微处理器是一个经典的实例,它是Intel在1993年采用0.8μm工艺推出的首款超标量处理器,其设计包括指令缓存、分支目标缓冲器、预取缓存器、执行单元、ALUs(算术逻辑单元)和数据缓存等组件,这些构成了一个高度复杂的执行架构。

控制单元(CU)作为微处理器的大脑,负责指令的解释和控制流程的调度,其内部结构复杂,包括指令缓存、分支预测、指令译码器、EU(执行单元)、ALUs、寄存器组、微码ROM、FPU(浮点处理单元)以及BIU(总线接口单元)等,这些部分通过不同的总线进行通信,确保高效的数据流和控制信号传递。

此外,课程还通过实例分析了Pentium微处理器的结构示意图,直观地展示了各部分的功能和连接方式,以及32位和64位数据总线对于处理能力和兼容性的提升。

本课程详细介绍了微处理器硬件结构的各个方面,从宏观的体系结构到微观的组件设计,以及实际应用中的优化策略,这对于理解和设计高性能微处理器具有重要的指导意义。

127 浏览量

点击了解资源详情

点击了解资源详情

2008-07-02 上传

2023-02-06 上传

点击了解资源详情

点击了解资源详情

2022-06-29 上传

编程神弱

- 粉丝: 0

- 资源: 3

最新资源

- opc ua客户端,opcua客户端界面,C#源码.zip

- MyMovies:在MEAN堆栈上进行的实验

- ciphermate:旨在简化简单的加密解密哈希base64任务的实用程序

- p2.mockup:设想

- carpentries-manchester:SoftwareDataLibrary曼彻斯特大学的木工活动@

- 库存品公开招标公告范例

- PHP实例开发源码—php二线小说网源码.zip

- react-Learning-roadmap

- Cap-Stone-TTP_backend

- leetcode答案-LeetCodeByPython:由Python编写的LeetCode

- automatic_ordering_system

- DrawLine

- easycal:简单的周历jQuery插件

- UDF 源项,udf源项编程问题,C,C++源码.zip

- 美的校园招聘面试官培训方案

- App:用于管理国际象棋事件的主Web应用程序