FPGA进阶:优化功耗设计策略与技巧

"FPGA进阶教程,关注时序约束、毛刺消除及降低功耗"

在FPGA设计中,深入理解和掌握高级技巧是成为专家的关键。本教程专注于解决FPGA设计中的经典问题,如处理毛刺、设定时序约束以及有效地降低功耗,这些都是现代高速、高密度FPGA设计中不可忽视的要素。

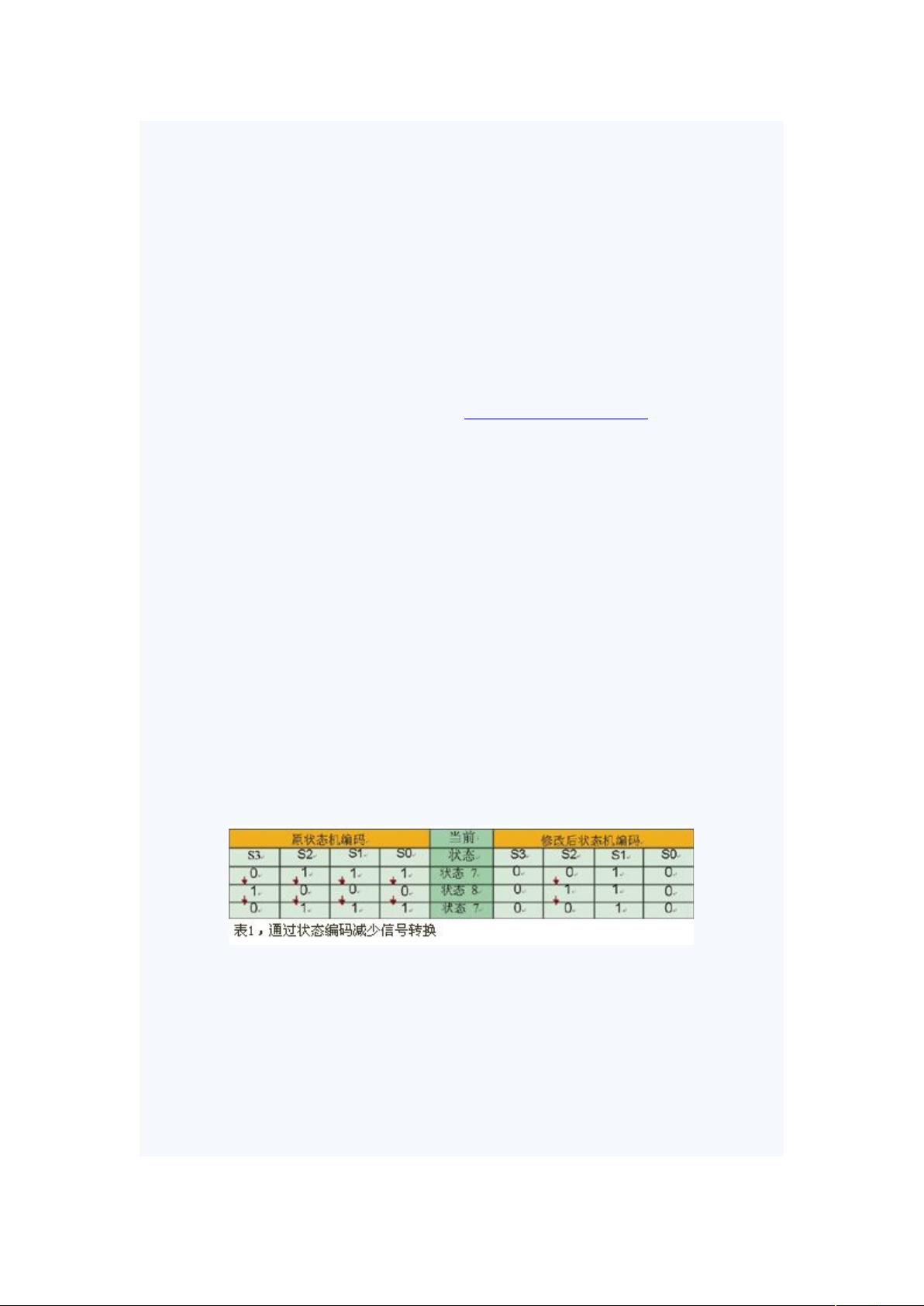

毛刺消除是FPGA设计中的一个重要环节,因为毛刺可能导致错误的信号传输和系统不稳定。毛刺通常是由信号线上的快速电压变化引起的,这种变化可能超出逻辑门的阈值范围。消除毛刺的方法包括使用滤波器、同步电路、适当的信号调理以及确保足够的信号上升/下降时间。理解毛刺产生的原因并采取相应的预防措施,可以提高系统的可靠性。

时序约束是确保FPGA设计正确运行的基石。它涉及到定义各个设计模块之间的路径延迟,以满足系统时钟周期的需求。通过正确设置时序约束,可以避免数据竞争、流水线阶段的正确同步以及满足关键路径的时序要求。Xilinx的ISE工具提供了强大的时序分析和约束管理功能,帮助设计师实现最佳性能与稳定性。

降低功耗是现代FPGA设计中的主要挑战,因为随着技术的进步,速度和密度的提升带来了更大的能耗。动态功耗和静态功耗是功耗的两大组成部分。动态功耗可以通过减小电压、降低工作频率和优化逻辑设计来控制。静态功耗主要与泄漏电流有关,受制于工艺技术、结温和元件尺寸。更小的工艺技术虽然可能导致更高的静态功耗,但同时也降低了动态功耗,因为其电压和电容更低。

在设计阶段就应考虑功耗优化,从选择合适的器件开始。不同工艺技术的FPGA有不同的功耗特性,选择低功耗技术或具有专用逻辑的器件可以有效降低功耗。例如,Xilinx的Virtex-4系列在90nm技术下表现出较低的静态功耗。此外,利用专门逻辑如块RAM、乘法器和DSP块,可以以较低的功率实现高性能操作。

I/O标准的选择也对功耗有显著影响。使用低驱动强度或低电压标准的I/O可以减少功耗。设计时应考虑I/O的默认状态,例如,使用需要上拉电阻的GTL/+标准时,保持I/O在高电平时可降低功耗。

FPGA设计的进阶涉及到多方面的知识,包括但不限于毛刺处理、时序约束的设定以及功耗的优化。通过深入了解这些主题,设计师可以创建出既高效又可靠的FPGA解决方案。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-01-11 上传

2021-02-27 上传

点击了解资源详情

点击了解资源详情

shuxin20

- 粉丝: 0

- 资源: 2

最新资源

- spotify-tournament:Spotify歌曲的单消除支架

- landing_LeWagon

- leaflet-virtual-grid:用于Leaflet的轻量级,无DOM的平铺图层,可用于查询具有边界框或中心半径的API,而无需加载平铺

- cochediviuroverride,c语言源码转exe格式,c语言

- [removed]遵循原始码实现的简易框架

- KnightLauncher:螺旋骑士的开源游戏启动器。 支持自动64位Java VM安装,Discord集成,更轻松的改装等等

- Latihan_Wardah

- MVBFA,c语言3d射击游戏源码,c语言

- 幸运星

- OL3-AnimatedCluster:OL3-AnimatedCluster现在是ol-ext项目的一部分

- website_files:开源社交媒体平台-Source website php

- Hold-Onto-Your-Body_64969:紧紧抓住你的身体! 理查德·刘易斯(Richard O.Lewis)撰写的古腾堡计划书,现在在Github上

- bmdview.zip

- Tesseract-OCR.zip

- C#-Leetcode编程题解之第21题合并两个有序链表.zip

- nodejs-server-wechat-landLordGame:微信小游戏-斗地主,包含nodejs-服务器