定时器与循环码计数器设计分析

需积分: 11 110 浏览量

更新于2024-08-26

收藏 551KB DOCX 举报

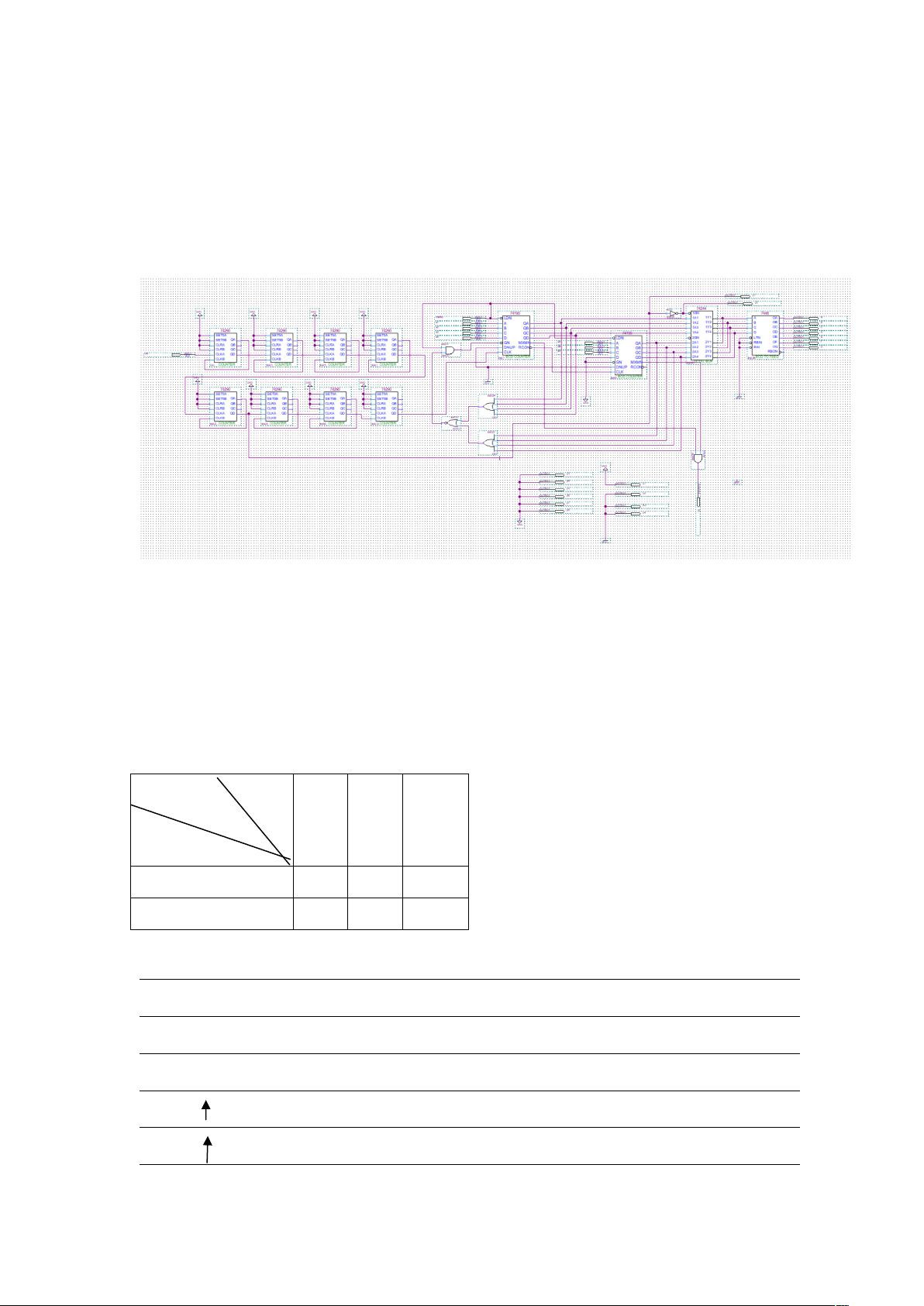

"该文档包含了两个电子技术领域的项目,分别是定时器和循环码计数器的设计。定时器使用七位二进制数表示计数,其中七段数码管用于显示,有特定的状态转换表和图。循环码计数器则涉及分频和循环计数,使用了Verilog语言进行编程实现,并控制8个LED灯显示计数状态。"

在数字电子技术中,定时器和循环码计数器是常见的数字逻辑设计应用。

首先,定时器的设计通常基于计数器,这里的定时器使用了74190作为核心部件,这是一个二进制减法计数器,能实现递减计数。电路设计允许用户通过拨码开关设定倒计时的初始值,当计数到零时,会触发一个信号(如R),指示计时结束。状态转换表和图描述了定时器在不同状态(S0、S1、S2)间的转换逻辑,这有助于理解定时器的工作流程。此外,仿真波形提供了实际操作中的计数过程验证,显示了正确计时和结束的标志。

其次,循环码计数器是利用分频和循环计数原理设计的。在Verilog代码中,`COUNT12`变量作为计数器,其值在每个时钟上升沿递增,直到达到预设的最大值(25'b1011111010111100000111111),然后重置为零,实现分频功能。同时,`F`信号用于控制计数循环,当`COUNT12`达到最大值时,`F`翻转,开始新的一轮计数。`num`变量用于跟踪当前的计数值,并通过`case`语句控制数码管的显示,使得数码管按照预定顺序循环显示,这里只显示第一个数码管,其他关闭。

循环码计数器的实现中,`always @(posedge clk)`和`always @(posedge F)`块分别对应于时钟同步的计数更新和循环条件的检查。`L1`到`L8`是连接到数码管的输出,用于显示当前的计数值。通过这样的设计,计数器可以在每次`F`翻转时更新数码管的显示,形成连续的循环计数效果。

总结来说,这两个项目展示了数字逻辑设计的基础,包括状态机的设计、计数器的使用以及硬件描述语言(Verilog)编程技巧。这些知识对于理解和设计数字系统,尤其是在嵌入式系统和微控制器应用中至关重要。

105 浏览量

485 浏览量

2022-10-17 上传

258 浏览量

2022-11-24 上传

2022-11-10 上传

2022-11-23 上传

2022-11-02 上传

161 浏览量

weixin_52366295

- 粉丝: 0

- 资源: 5

最新资源

- simulatedevice_v1.0.7.zip

- 垃圾分类网站管理系统-毕业设计

- 火车订票系统.rar

- Moriyama.SuperDocTypeCreate

- CordovaGui-开源

- mri_demo

- 练习4

- Jekyll静态站点生成器 v3.6.1

- class26rishon

- C++面向对象多线程编程-pdf

- 基于Springboot与Vue的学生选课系统毕业设计

- 租赁系统。。.rar

- AreaTri(P1,P2,P3):给定顶点的 3D 坐标的三角形面积-matlab开发

- dynamic-charts-reactjs

- FirebaseAuthentication

- C++后台开发 核心技术与应用实践