清华大学微电子所:数字集成电路速度优化与延时模型详解

需积分: 10 175 浏览量

更新于2024-07-27

收藏 1.68MB PDF 举报

清华大学数字2012数字集成电路课程的第四章深入探讨了数字集成电路的速度设计与优化。这一章节由李翔宇教授,来自清华大学微电子学研究所,主要讲解了以下几个核心知识点:

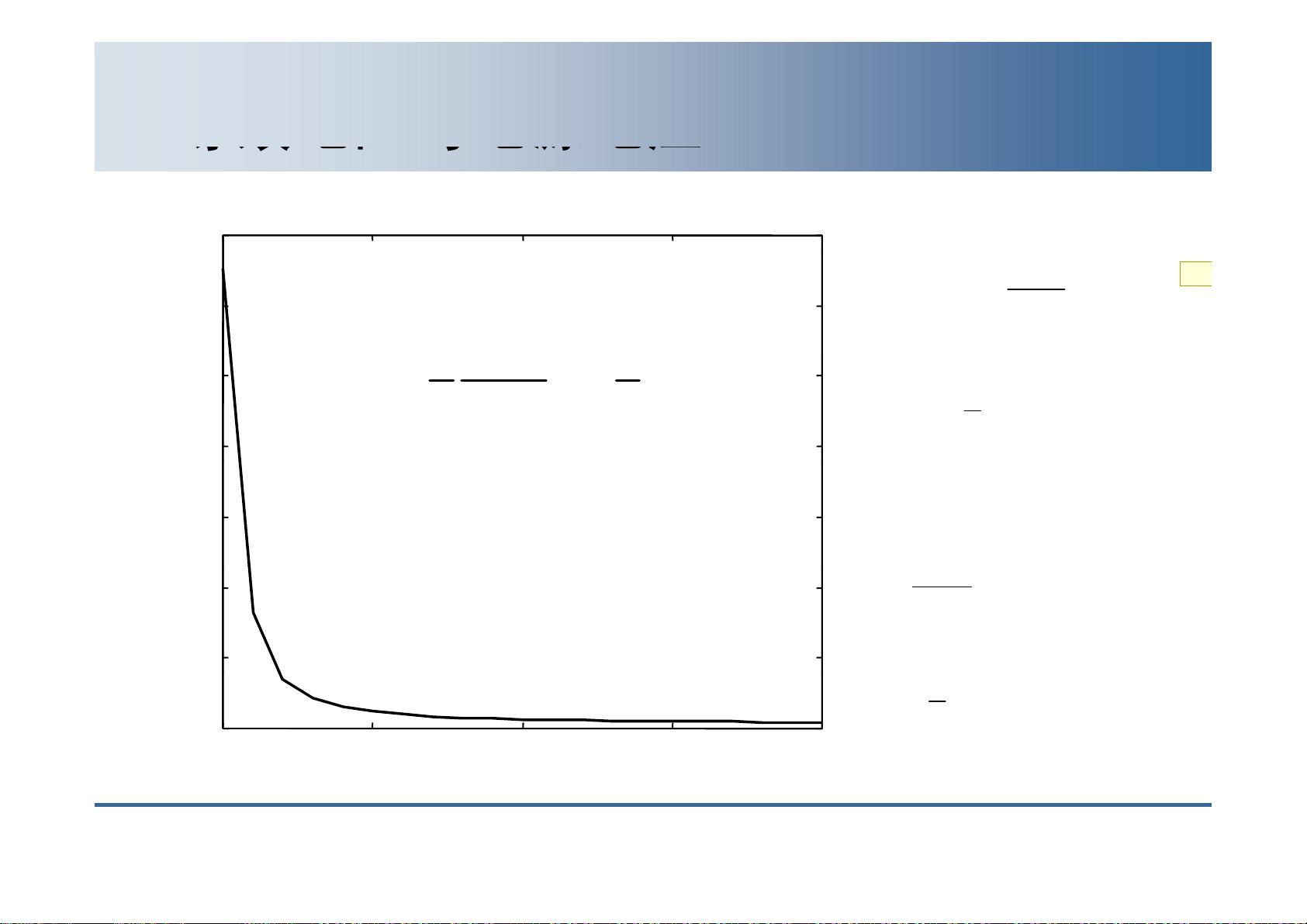

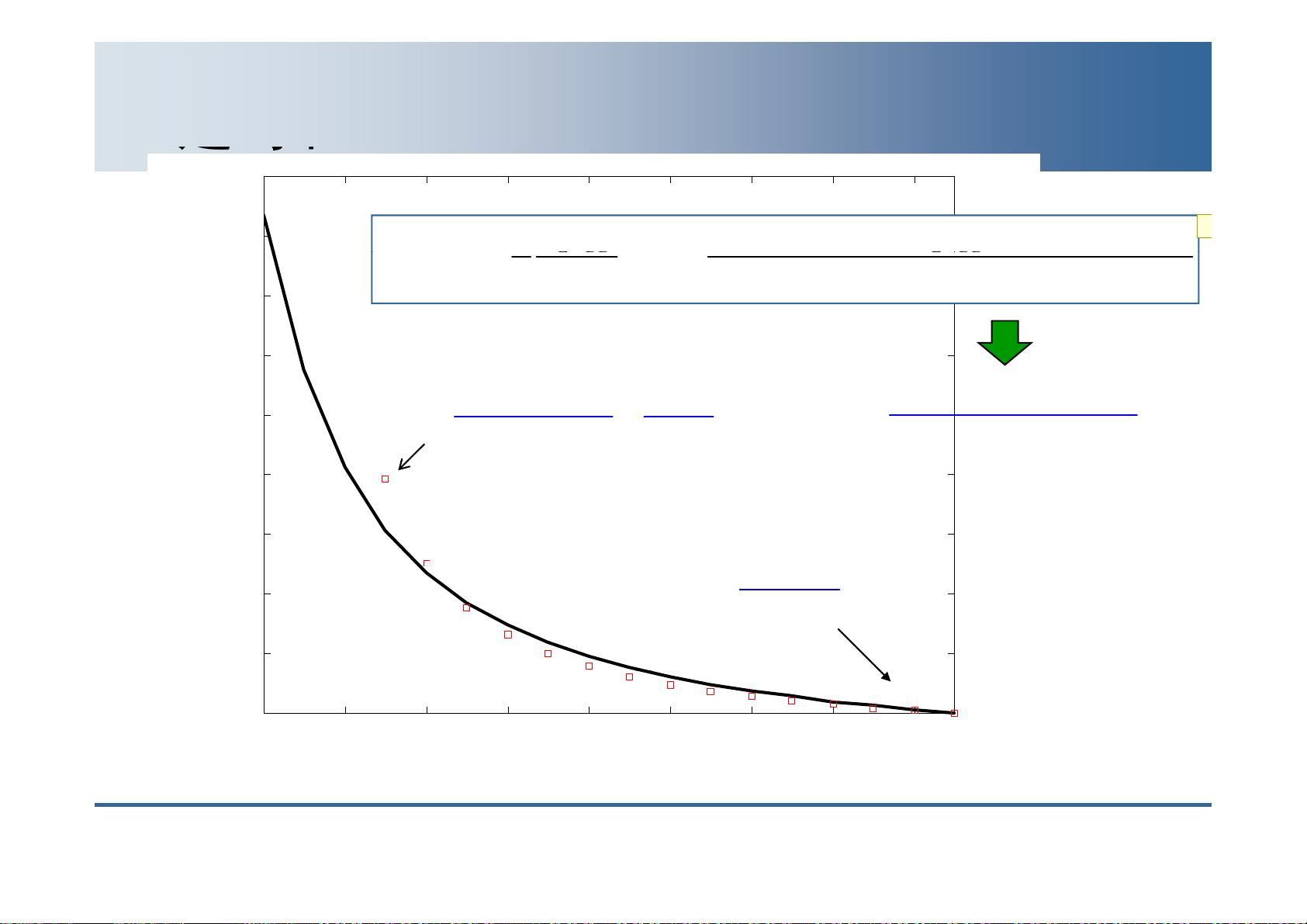

1. 延时模型:延时是衡量集成电路性能的重要指标,包括RC网络延时、CMOS逻辑门延时和复杂逻辑门的延时模型。延时模型是设计过程中必不可少的工具,它帮助工程师理解信号从输入到输出所需的时间。一阶RC网络的延时计算公式涉及电容C和电阻R,而更复杂的逻辑门如CMOS反相器,其延时会根据门级结构有所不同。

2. VLSI设计指标:VLSI(Very Large Scale Integration)设计中,关键的指标包括传播延时(tp)和翻转时间(tr)。传播延时是指信号从输入到达输出达到特定幅度的时间,例如90%的幅值变化;翻转时间则是信号从低电平变为高电平或反之所需的时间。对于阶跃输入,传播延时可以通过ln(2)τ=0.69RC来近似计算,翻转时间则为ln(9)τ=2.2RC。

3. RC树模型:这是电路设计中的一个重要概念,用于估算多级电路的延迟。RC树模型考虑了树状结构中节点之间的电容和电阻关系,特别是当只有一个输入节点且所有电容都是对地电容,且没有电阻回路的情况下,可以使用Elmore延迟近似来估计源点到其他节点的时间常数。

4. 速度优化:在实际设计中,为了提高集成电路的速度,工程师需要对延时进行精细控制,可能通过改进电路结构、选择合适的材料以及利用自动化工具进行分析和优化。手工分析和自动化工具在延时模型的处理上各有优势,前者适合简单的模型,后者则在大规模复杂电路中发挥关键作用。

通过学习本章内容,学生将能够掌握数字集成电路设计中关于速度的关键概念和技术,这对于理解和优化现代数字电路的性能至关重要。这些理论知识不仅适用于芯片设计初学者,也对从事该领域研究和应用的专业人士具有实际指导意义。

2024-02-29 上传

2024-02-29 上传

2023-10-21 上传

2024-02-29 上传

2024-01-14 上传

2023-06-20 上传

wuf0009

- 粉丝: 0

- 资源: 2

最新资源

- 深入理解23种设计模式

- 制作与调试:声控开关电路详解

- 腾讯2008年软件开发笔试题解析

- WebService开发指南:从入门到精通

- 栈数据结构实现的密码设置算法

- 提升逻辑与英语能力:揭秘IBM笔试核心词汇及题型

- SOPC技术探索:理论与实践

- 计算图中节点介数中心性的函数

- 电子元器件详解:电阻、电容、电感与传感器

- MIT经典:统计自然语言处理基础

- CMD命令大全详解与实用指南

- 数据结构复习重点:逻辑结构与存储结构

- ACM算法必读书籍推荐:权威指南与实战解析

- Ubuntu命令行与终端:从Shell到rxvt-unicode

- 深入理解VC_MFC编程:窗口、类、消息处理与绘图

- AT89S52单片机实现的温湿度智能检测与控制系统