FPGA竞争冒险详解:功能、结构与解决策略

需积分: 9 94 浏览量

更新于2024-08-11

收藏 1.88MB PDF 举报

FPGA(Field-Programmable Gate Array)是一种高度可编程的集成电路,由逻辑功能块构成阵列,并通过内部可配置连线实现灵活的逻辑功能。它在数字系统设计中扮演着重要角色,特别是在原型设计阶段,能够降低成本和缩短开发周期。与PLD(可编程逻辑器件)和ASIC(专用集成电路)相比,FPGA提供了更大的灵活性和可扩展性。

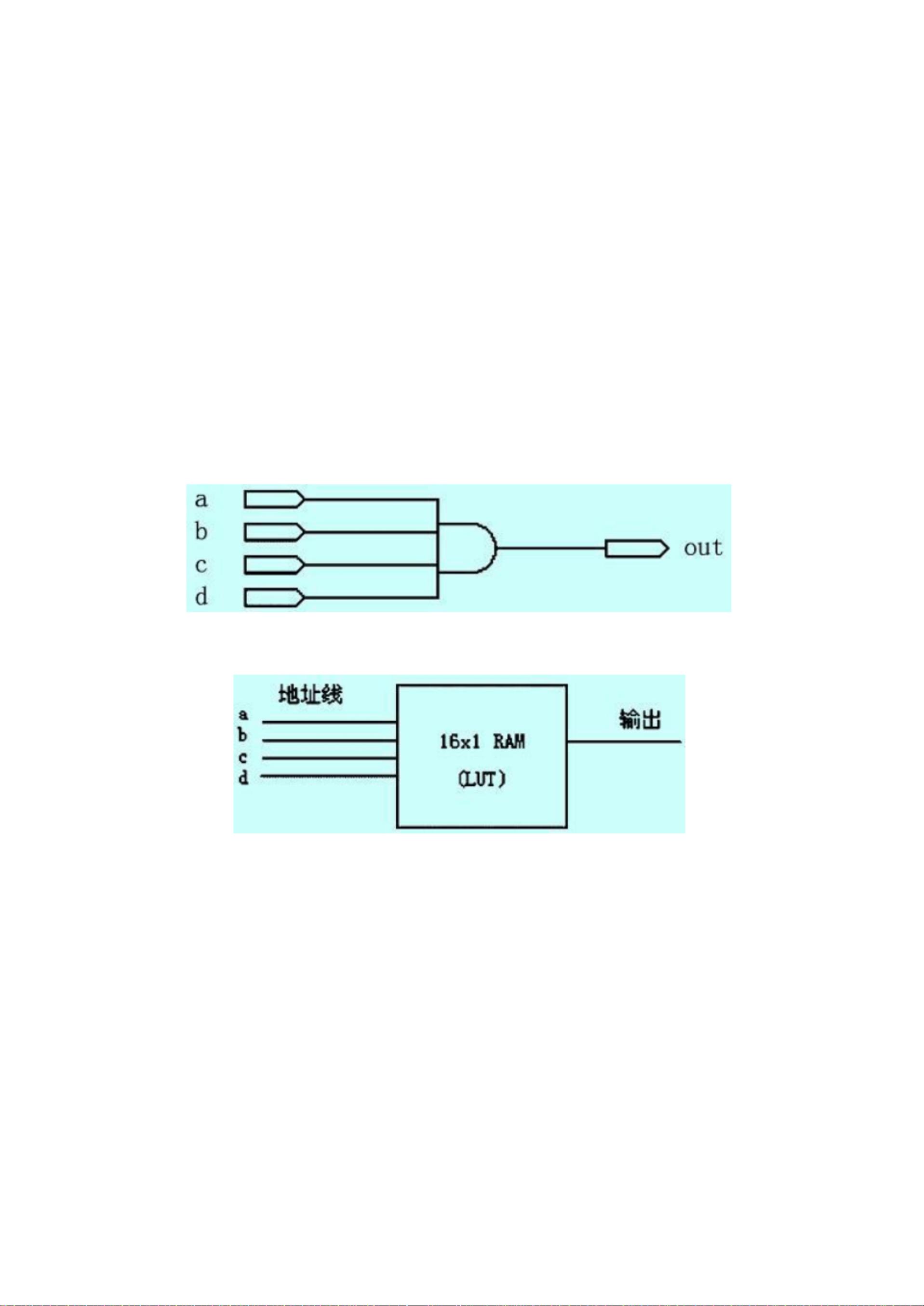

FPGA的核心功能取决于其配置数据,这些数据通常存储在片内的SRAM或熔丝中。对于SRAM型FPGA,配置过程通常需要外部加载,可以通过EPROM或其他存储介质进行管理,允许用户在运行时修改器件的逻辑行为。LUT(Look-Up Table),作为FPGA的基本构建模块,是可编程的最小逻辑单元,它决定了FPGA能实现的逻辑功能种类。

FPGA的典型结构如Altera的FLEX10KE系列,其内部包含嵌入式阵列块(EAB)、逻辑阵列块(LAB)、快速通道互连和输入/输出单元(IOE)。嵌入式阵列用于实现复杂功能如数字信号处理和微控制器,而逻辑阵列则用于执行基础逻辑操作。EAB具有变形RAM的能力,拥有输入输出端口和内置寄存器。快速通道互连提供高速内部通信,而IOE负责连接外部接口,确保数据的输入输出。

然而,如同所有数字电路,FPGA设计中会遇到竞争冒险问题。这种现象源于多个路径同时试图访问同一数据而导致的不确定性和潜在错误。解决竞争冒险的方法包括但不限于:

1. **时序分析和设计**: 通过精确地定义时钟周期、数据传输时间和控制信号延迟,确保信号的同步性,避免同时读写同一个寄存器。

2. **使用锁存器(Latches)和同步信号**: 在关键路径上添加锁存器可以确保数据在多条路径之间的单一流向,减少冒险。

3. **流水线设计**: 分解任务为独立的步骤,每个步骤在一个特定时间完成,减少同时操作的可能性。

4. **仲裁逻辑**: 使用专门的硬件逻辑来决定哪个请求优先,确保一个时间只有一个信号被处理。

5. **使用保持和预置逻辑**: 保持信号可以防止数据在信号传输期间改变,预置逻辑则保证数据在下一次时钟周期之前已准备好。

6. **使用专门的硬件资源解决竞争冒险**: 一些FPGA器件提供特殊的资源,如同步寄存器或冲突检测单元,用于预防和解决竞争冒险。

理解并正确处理FPGA的竞争冒险至关重要,因为它直接影响到系统的性能、可靠性和稳定性。通过优化设计策略和利用FPGA特有的解决方案,设计师可以最大限度地减少此类问题的影响,确保系统的正常运行。

2021-05-25 上传

2022-11-02 上传

2011-08-12 上传

2023-10-28 上传

2023-08-10 上传

2023-08-22 上传

2023-05-29 上传

2024-10-28 上传

2023-07-22 上传

紫藤花叶子

- 粉丝: 286

- 资源: 889

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库