华为大规模逻辑设计指导:VERILOG编程与注意事项

需积分: 32 132 浏览量

更新于2024-07-29

收藏 3.45MB PDF 举报

《华为大规模逻辑设计指导书》是一份详尽的内部使用文档,针对FPGA设计提供专业指导。该文档共140页,分为两大部分:方法论和VERILOG语言编写规范。在第一篇中,作者强调了设计过程中的关键环节,包括:

1. 命名规则:信号和变量的命名需具有明确的意义,如反映其来源、功能和状态,以便于理解和维护。例如,推荐使用包含信息如"origin"、"validState"的名称。

2. 编码风格:规定了VERILOG语言的编写规范,如选择有意义的信号和变量名,使用case语句、IF语句、表达式、net和register的正确用法。

3. 模块设计:讨论了模块划分的重要性,以及如何清晰地组织和分层结构。

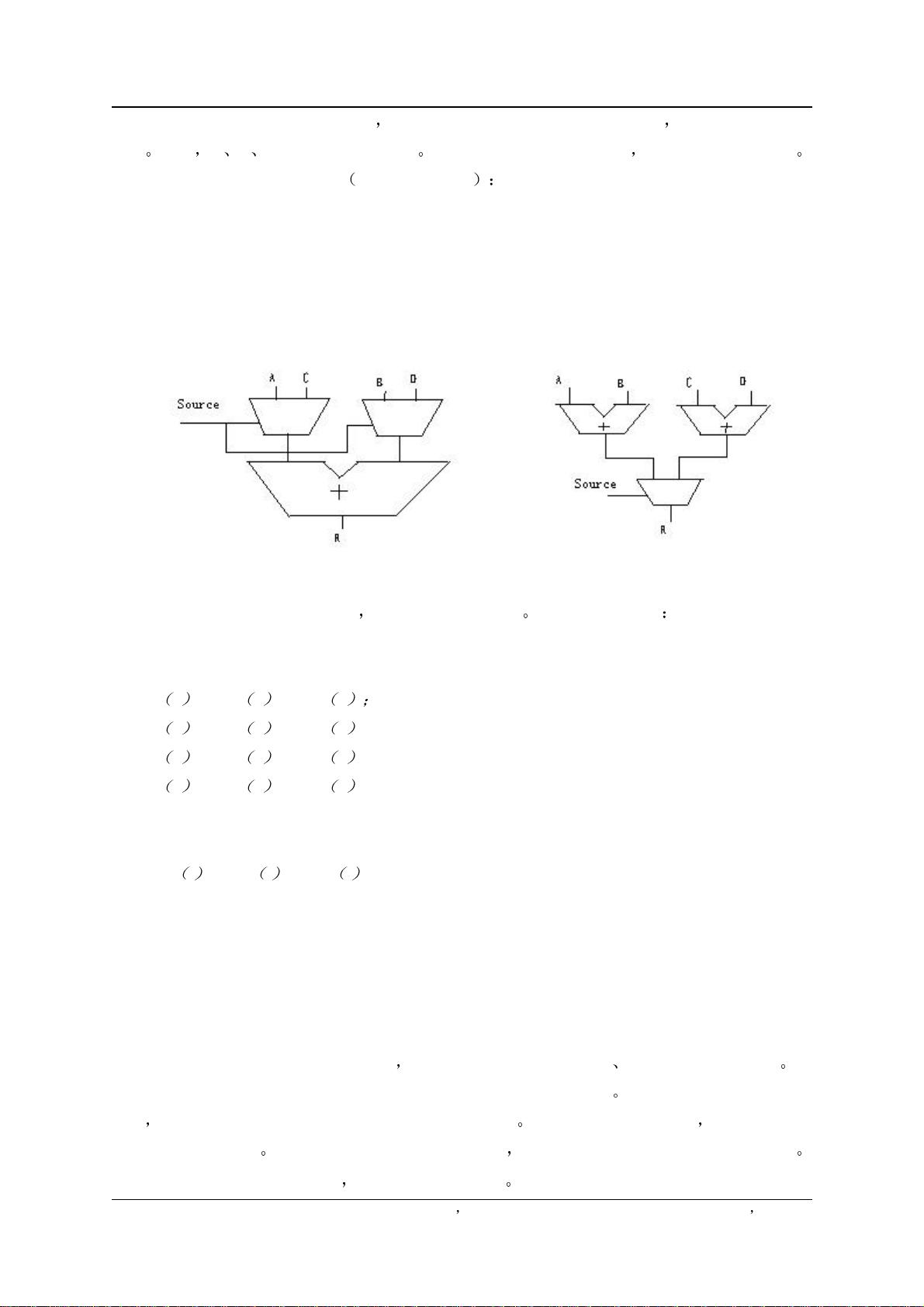

4. 编程技巧:如避免使用Latch,理解多赋值语句的应用,处理三态总线,以及考虑代码执行时间和资源共享问题。

5. 语言实例:给出了参数化元件实例、程序包和函数的书写示例,以及VHDL语言的基本用法和保留字。

6. 状态机(FSM):阐述了有限状态机在设计中的应用和注意事项。

7. 包与类属(generics):讲解了包的定义和使用,以及类属在参数化设计中的作用。

8. 过程与函数:介绍了function和procedure的写法,以及运算符的运用。

9. 代码编写细节:包括TAB键间距的规范,以及对常见错误和优化技巧的关注。

附录部分深入探讨了综合执行时间的考虑,提供了具体案例和最佳实践。这份文档对于理解和遵循华为在大规模逻辑设计中的标准化流程和技术要求至关重要,适用于从事相关领域设计的专业人士。由于文档涉及敏感信息,确保仅限内部使用,并强调版权和保密性。

2010-03-29 上传

132 浏览量

2008-10-16 上传

2009-10-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

我是小撸

- 粉丝: 3

最新资源

- Servlet核心技术与实践:从基础到高级

- Servlet核心技术详解:从基础到过滤器与监听器

- 操作系统实验:进程调度与优先数算法

- 《Div+CSS布局大全》教程整理

- 创建客户反馈表单的步骤

- Java容器深度解析:Array、List、Set与Map

- JAVA字符集与编码转换详解

- 华为硬件工程师的手册概览

- ASP.NET 2.0 实现动态广告管理与随机显示

- 使用Dreamweaver创建网页过渡动画效果

- 创建ASP登录系统:步骤详解

- ASP论坛搭建:资料转义与版主权限管理

- C#新手必读:新版设计模式详解与实例

- 提升网站论坛制作:技术优化与点击计数

- AVR微处理器ATmega32L/32:高级特性和功能详解

- C++实现经典矩阵:螺旋及蛇形排列