FPGA/CPLD设计心得:时序控制与高效系统构建

需积分: 48 76 浏览量

更新于2024-08-02

2

收藏 1.47MB PDF 举报

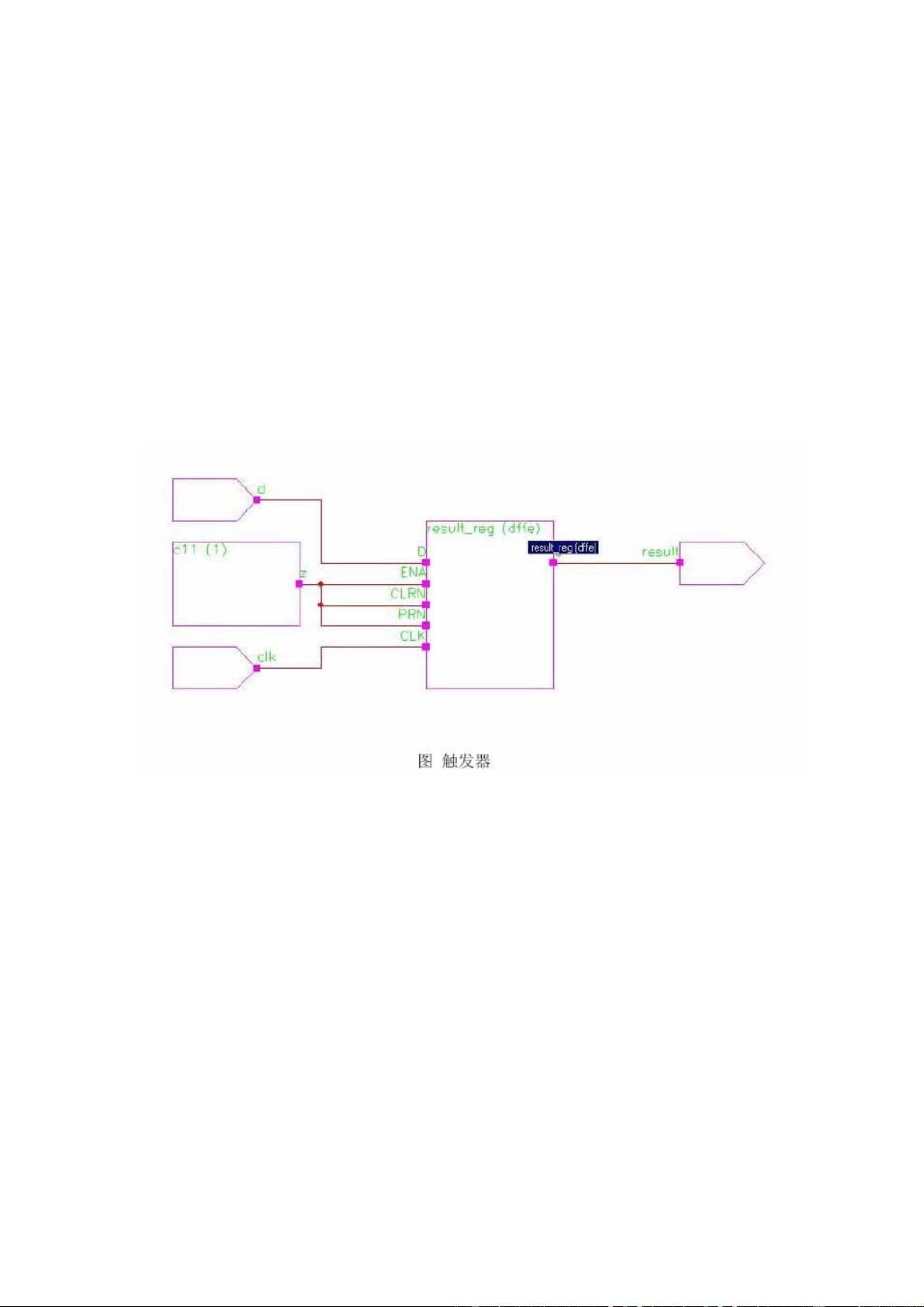

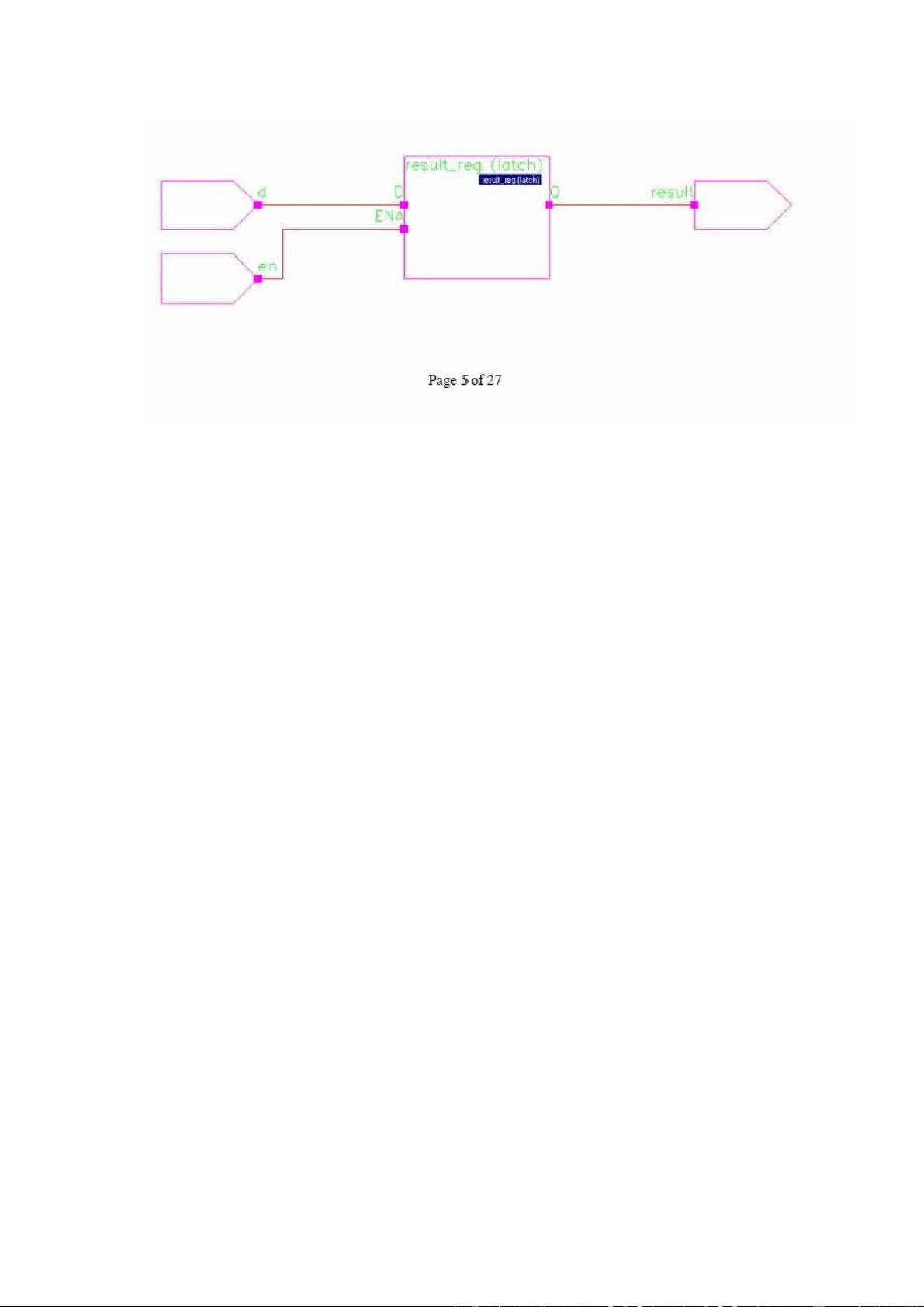

在本文中,作者分享了他们在FPGA和CPLD数字电路设计过程中的宝贵经验,强调了时序设计在这些可编程逻辑器件中的关键作用。首先,建立时间和保持时间是数字电路设计的基础概念,它们分别定义了数据稳定进入触发器之前和之后所需的时间窗口。若这两个参数不足,可能导致数据丢失,影响电路的正确性。设计者需要利用开发软件自动计算输入之间的建立和保持时间,并在后仿真的过程中分别检查最大延迟(用于建立时间)和最小延时(用于保持时间)。

文章指出,建立时间受限于时钟周期,当系统运行在高频时钟下无法满足要求时,可以通过降低时钟频率来解决。然而,保持时间是独立于时钟周期的,它更依赖于逻辑结构和布局布线的质量。如果保持时间设计不合理,即使调整时钟频率也可能无法满足要求,可能需要对整个系统进行大幅度修改,严重影响设计效率。

在FPGA中,由于连线长度、逻辑单元数量、工艺等因素,信号在器件内部传输会引入竞争和冒险现象。多路信号的电平变化可能会导致输出不一致,因为组合逻辑的响应并非同步。为避免这些问题,设计者需要充分理解和管理信号的延迟,确保信号的准确传输。

本文提供了关于如何在FPGA和CPLD设计中有效地处理时序问题,包括理解并管理建立时间和保持时间,以及识别和解决竞争和冒险现象的实用技巧。这对于提高可编程逻辑器件的设计质量和工作效率至关重要。通过实践经验的分享和实例验证,读者可以从中学习到如何在实际项目中应用这些原则。

2023-05-12 上传

2023-07-17 上传

2023-06-28 上传

2023-08-08 上传

2023-06-14 上传

2023-05-11 上传

qaz0158

- 粉丝: 0

- 资源: 9

最新资源

- OptiX传输试题与SDH基础知识

- C++Builder函数详解与应用

- Linux shell (bash) 文件与字符串比较运算符详解

- Adam Gawne-Cain解读英文版WKT格式与常见投影标准

- dos命令详解:基础操作与网络测试必备

- Windows 蓝屏代码解析与处理指南

- PSoC CY8C24533在电动自行车控制器设计中的应用

- PHP整合FCKeditor网页编辑器教程

- Java Swing计算器源码示例:初学者入门教程

- Eclipse平台上的可视化开发:使用VEP与SWT

- 软件工程CASE工具实践指南

- AIX LVM详解:网络存储架构与管理

- 递归算法解析:文件系统、XML与树图

- 使用Struts2与MySQL构建Web登录验证教程

- PHP5 CLI模式:用PHP编写Shell脚本教程

- MyBatis与Spring完美整合:1.0.0-RC3详解