Xilinx原语详解:功能分类与Verilog应用

Xilinx原语是Xilinx公司为其特定FPGA器件开发的一系列预定义模块,它们类似于C++编程中的库函数,直接对应于硬件中的基本逻辑单元,如查找表(LUT)、D触发器、随机存取存储器(RAM)等。这些原语是用户设计过程中的基础构建块,允许设计师以最直接的方式控制硬件,无需过多的底层转换。在使用时,设计师可以直接在Verilog或VHDL等高级硬件描述语言(HDL)中实例化这些原语,就像使用汇编语言中的指令。

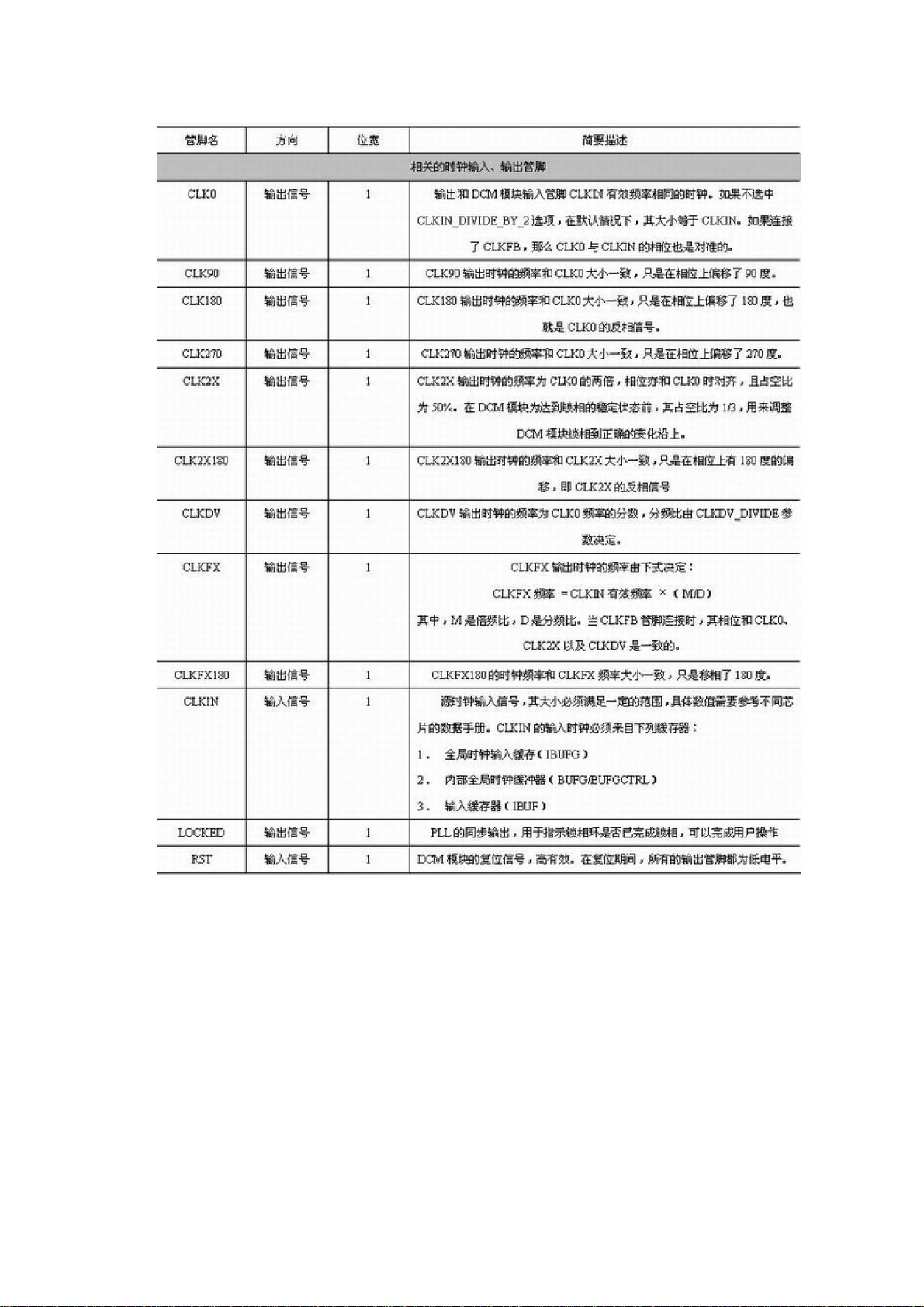

Xilinx原语的使用非常灵活,但需要注意的是,它们依赖于特定的硬件配置,不是所有原语都能在所有Xilinx芯片上通用。例如,Virtex-4平台提供了较为全面的原语种类,包括计算组件(如DSP48核,一种硬件乘法器)、I/O端口组件、寄存器与锁存器、时钟组件、处理器组件、移位寄存器等十类。每个组件都有其特定的功能和结构,如DSP48核是一个18x18位的有符号乘法器加上一个可配置流水线的3输入加法器,广泛应用于滤波器系统,可以提升系统稳定性和节省逻辑资源。

在Verilog中,使用这些原语时,设计者只需要按照模板实例化,例如对于DSP48核的实例化可能如下:

```verilog

module fpga_v4_dsp48 (

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN, CARRYINSEL, CECTRL, CEM, CEP, CLK, OPMODE, PCIN,

RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RS

);

```

这表示该模块包含了多个输入和输出接口,以及控制信号,通过指定的参数来配置乘法器和加法器的行为。原语的使用不仅简化了设计过程,而且有助于提高代码效率和硬件性能。

然而,值得注意的是,虽然原语提供了便利,但过度依赖可能导致设计缺乏灵活性,因此在实际设计中,还需结合高级设计抽象来平衡效率和可维护性。同时,熟悉不同类型的原语及其适用场景,对于高效利用Xilinx FPGA的潜力至关重要。

165 浏览量

2018-03-27 上传

114 浏览量

136 浏览量

2022-09-07 上传

126 浏览量

灰灰_08

- 粉丝: 0

- 资源: 2

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录