Intel IXP2400网络处理器驱动的路由器架构与挑战

69 浏览量

更新于2024-09-04

收藏 1.64MB DOC 举报

随着互联网流量的爆炸性增长和新业务需求的多元化,传统的路由器设计面临着巨大的挑战。通用处理器(GPP)虽然灵活,但在处理速度上无法满足高速网络的需求;专用集成电路ASIC虽然能提升处理效率,但牺牲了灵活性。因此,一种新的解决方案——网络处理器(NP)应运而生,它结合了ASIC的高速性能与GPP的灵活性,为下一代路由器设计提供了理想选择。

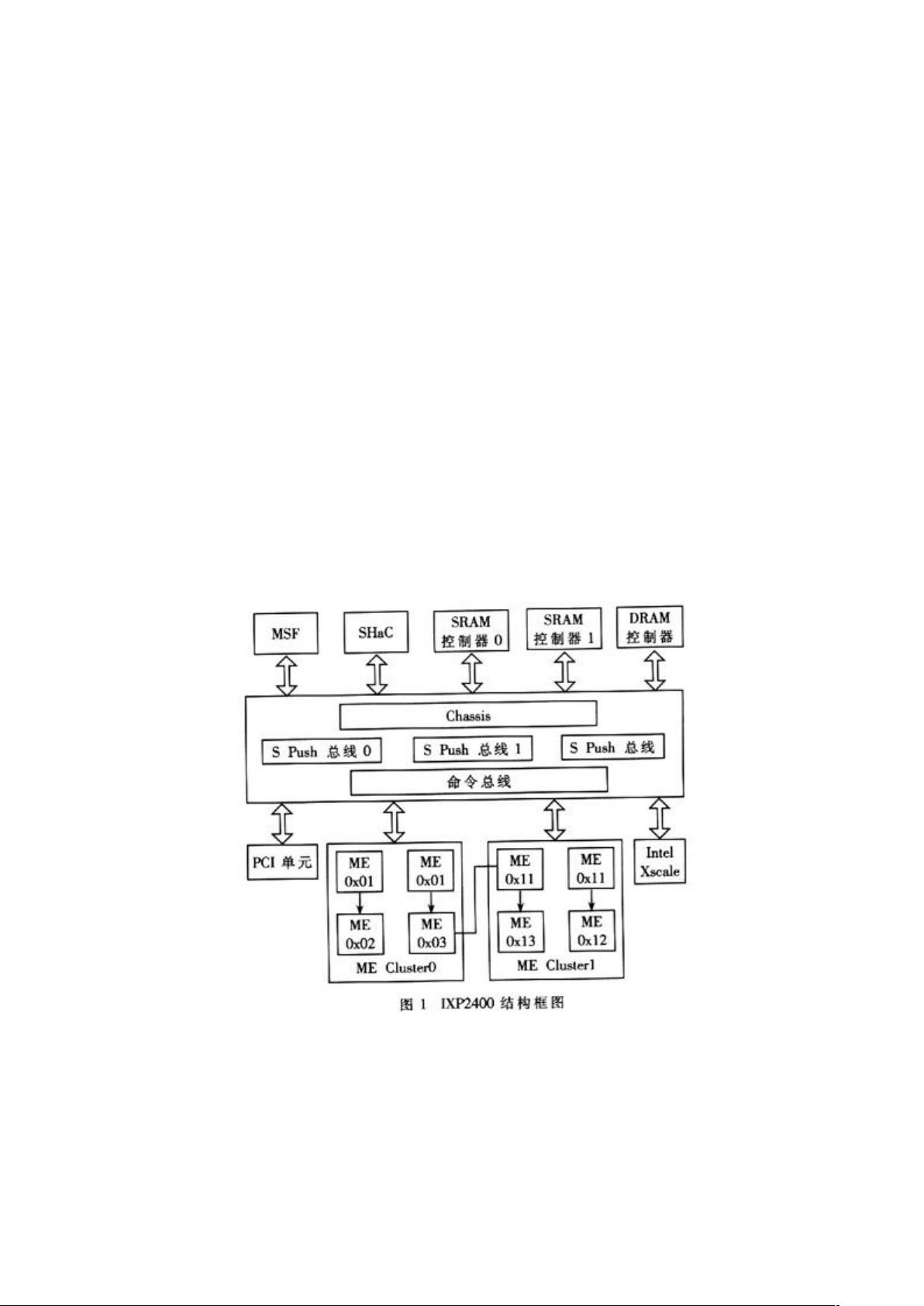

本文以Intel的IXP2400网络处理器为例进行深入研究。作为Intel在2002年推出的第二代IXA网络处理器,IXP2400专为中高端应用设计,支持OC-48级别的网络路由交换。其架构遵循片上系统(SoC)理念,包含8个可编程的8线程微引擎ME,用于高效处理数据包,以及一个XScale核,作为系统的控制和管理核心。XScale核是32位的嵌入式精简指令集处理器,运行在600MHz的时钟频率下,拥有指令和数据缓存,负责初始化、配置、提供时钟、管理路由表以及地址映射等功能。

微引擎是IXP2400的关键组成部分,每个微引擎都是独立的32位RISC处理器,工作频率同样为600MHz,8个线程可并行执行,极大地提升了数据包的接收、处理和发送效率。IXP2400通过数据总线连接多种存储设备,如SRAM和DRAM,其中DRAM主要用于存储大容量的数据结构,如路由表,而SRAM则提供快速的数据访问。

基于网络处理器的路由器设计不仅实现了高性能的转发处理,而且通过硬件并行性优化,能够在流量处理上达到线速。然而,这种设计并非一蹴而就,未来仍需面对诸多挑战,如功耗管理、软件可编程性、适应新技术(如SDN和NFV)等。随着技术的进步,基于网络处理器的路由器有望在性能、成本和灵活性上实现更好的平衡,推动网络基础设施的进一步演进。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-09 上传

2020-12-08 上传

2021-10-09 上传

2021-10-09 上传

2021-10-09 上传

2021-10-09 上传

weixin_38652058

- 粉丝: 9

- 资源: 901

最新资源

- encapsulamento

- 3D花瓶模型效果图

- learnC-4-macro

- 首页列表翻页教程网(带手机) v3.74

- Pan

- bdsegal.github.io

- FP-PSP-SERVER

- awesome-playgrounds:一系列令人敬畏的Xcode Swift游乐场,围绕诸如计算机科学,数学和物理等主题的交互性和指导性使用而集中

- login-mypage

- CKEditor v4.7.1

- engrid-scripts

- 麻将厅3D模型设计

- CodeFun:存放代码示例的地方

- automationpractice:与Azure DevOps集成的测试项目

- 塞恩·普勒

- prettyconf:用于设置代码分离的可扩展库