DDR3信号完整性分析指南:仿真报告编写要点

下载需积分: 50 | PDF格式 | 16.15MB |

更新于2024-07-17

| 14 浏览量 | 举报

"DDR3 SI 分析报告是针对DDR3内存系统信号完整性的详细分析文档,旨在指导初学者如何编写DDR3仿真的分析报告。该报告由Alexander Karas于2012年12月27日编写,涵盖了DDR3 PCB布局、关键网络列表、时钟、地址线、数据线的路由、时序分析等方面的内容,同时提供了附录,包括层概述和最佳模拟模型的选择指南。"

DDR3 SI(Signal Integrity)分析报告是深入理解DDR3内存系统信号完整性的关键文档,对于设计和验证高速数字电路的工程师尤其重要。以下是报告中的主要知识点:

1. **DDR3简介**:报告开头简要介绍了DDR3技术的基本概念,包括其在现代计算平台中的作用,以及信号完整性在确保系统稳定性和性能方面的重要性。

2. **项目活动与交付物**:这部分可能描述了进行DDR3仿真分析的过程,包括设计目标、仿真工具选择、预期结果等,以帮助读者了解整个项目的工作流程。

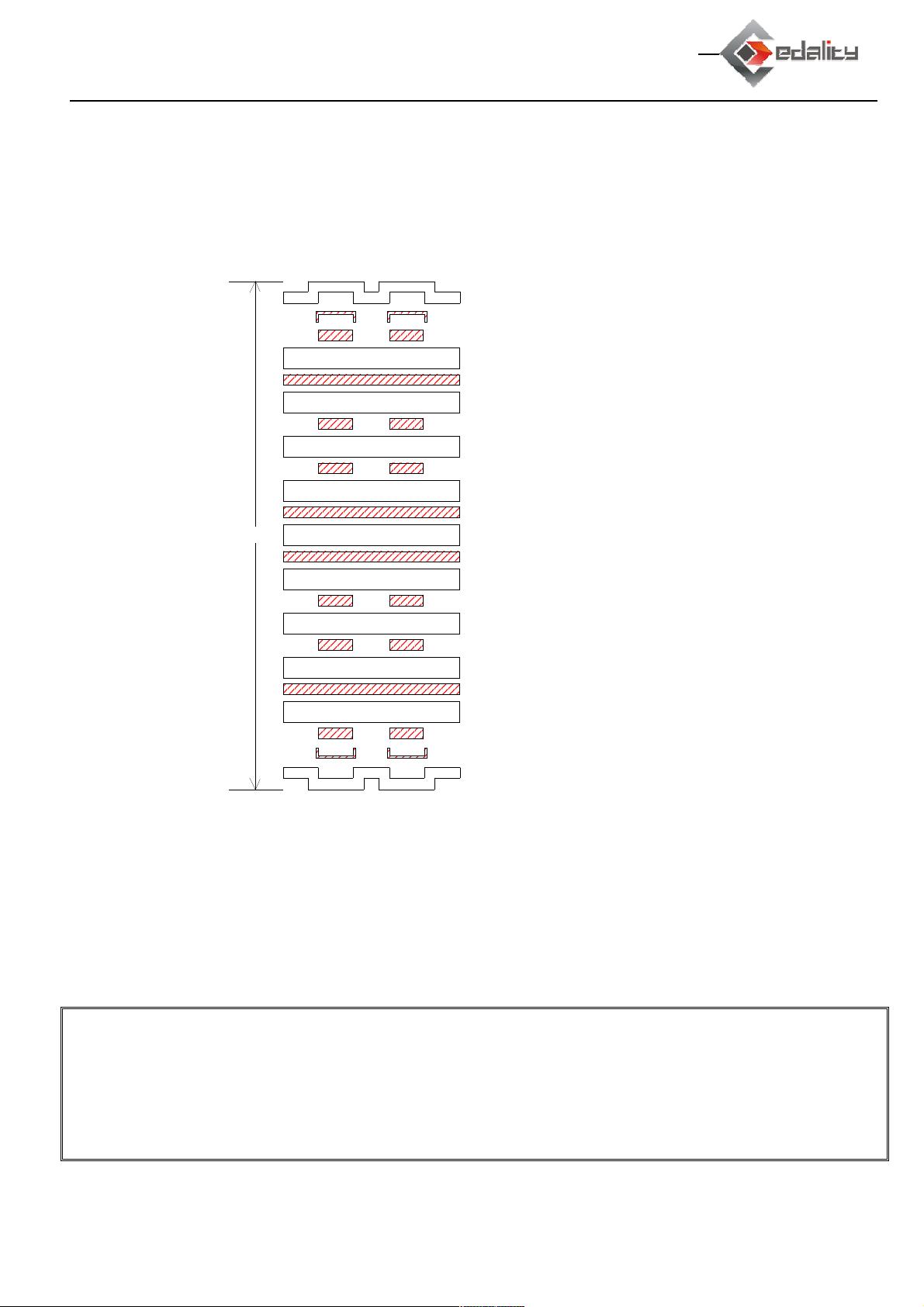

3. **DDR3 PCB布局**:报告详细分析了DDR3内存模块在PCB上的布局策略,重点关注了板层堆栈信息,这直接影响到信号的质量和速度。

4. **关键网络列表**:列出并分析了对DDR3系统性能至关重要的信号线,这些信号线通常包括时钟、地址线、数据线以及控制信号,确保它们在PCB上的布线满足信号完整性的要求。

5. **DDR3时钟**:详细探讨了DDR3内存系统的时钟信号,时钟是DDR3系统同步的基础,对其准确性和稳定性有严格要求。

6. **DDR3地址线**:报告深入研究了地址线的信号特性,包括地址信号的路由、时序和相互关系,确保地址正确无误地传输至内存控制器。

7. **数据线的路由**:针对每个字节 lane(Byte Lane)进行了单独分析,从字节lane 0到字节lane 3,探讨了数据传输过程中的信号完整性问题,以及如何优化数据线的布局和阻抗匹配。

8. **时序分析**:报告对地址和时钟的时序进行了深入分析,并展示了时序分析的结果,这对于确保DDR3的正确操作至关重要,因为时序错误可能导致数据丢失或系统不稳定。

9. **结论**:这部分总结了信号完整性和时序分析的关键发现,强调了优化设计以减少潜在问题的必要性。

10. **附录**:提供了关于PCB层的概述,以及选择适合模拟的最佳模型的指南,如驱动器阻抗、信号强度和ODT(On-Die Termination)参数,这些对于精确仿真和问题诊断非常有用。

这份DDR3 SI分析报告是学习DDR3内存系统设计和信号完整性分析的重要参考资料,它不仅涵盖了理论知识,还包含了实际操作和问题解决的经验分享。对于从事高速数字电路设计的工程师来说,它是一个宝贵的教育资源。

相关推荐

449 浏览量

2022-07-25 上传

180 浏览量

135 浏览量

2021-05-27 上传

2021-04-05 上传

qq_34778088

- 粉丝: 0

最新资源

- Node.js打造WH1080气象站服务:数据与界面全解析

- OV7670与CY7C68013配合的上位机软件开发指南

- 传感器原理及应用习题答案解析

- 二维码生成工具的核心jar包介绍

- jbpm4.4邮件发送功能演示与实现分析

- Strava数据同步至Home Assistant的自定义组件介绍

- C#实现支持向量机:实例分析

- 双语版OpenCV函数查询手册

- 快速搭建React Native商城项目基础结构指南

- Android WebView利用腾讯X5内核优化在线视频播放缓存

- 软件测试工程师的职业成长四条发展路径

- Adafruit开发的TLC5947库助力Arduino PWM/LED驱动

- 掌握Flutter开发:flutter-common-widgets-app实战指南

- C#操作Windows用户及MySQL数据库权限管理教程

- 掌握TypeScript:全面学习JavaScript开发指南

- LianYiSmsCom短信猫二次开发包指南