基于HDL的十进制计数器设计:实验与实现

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

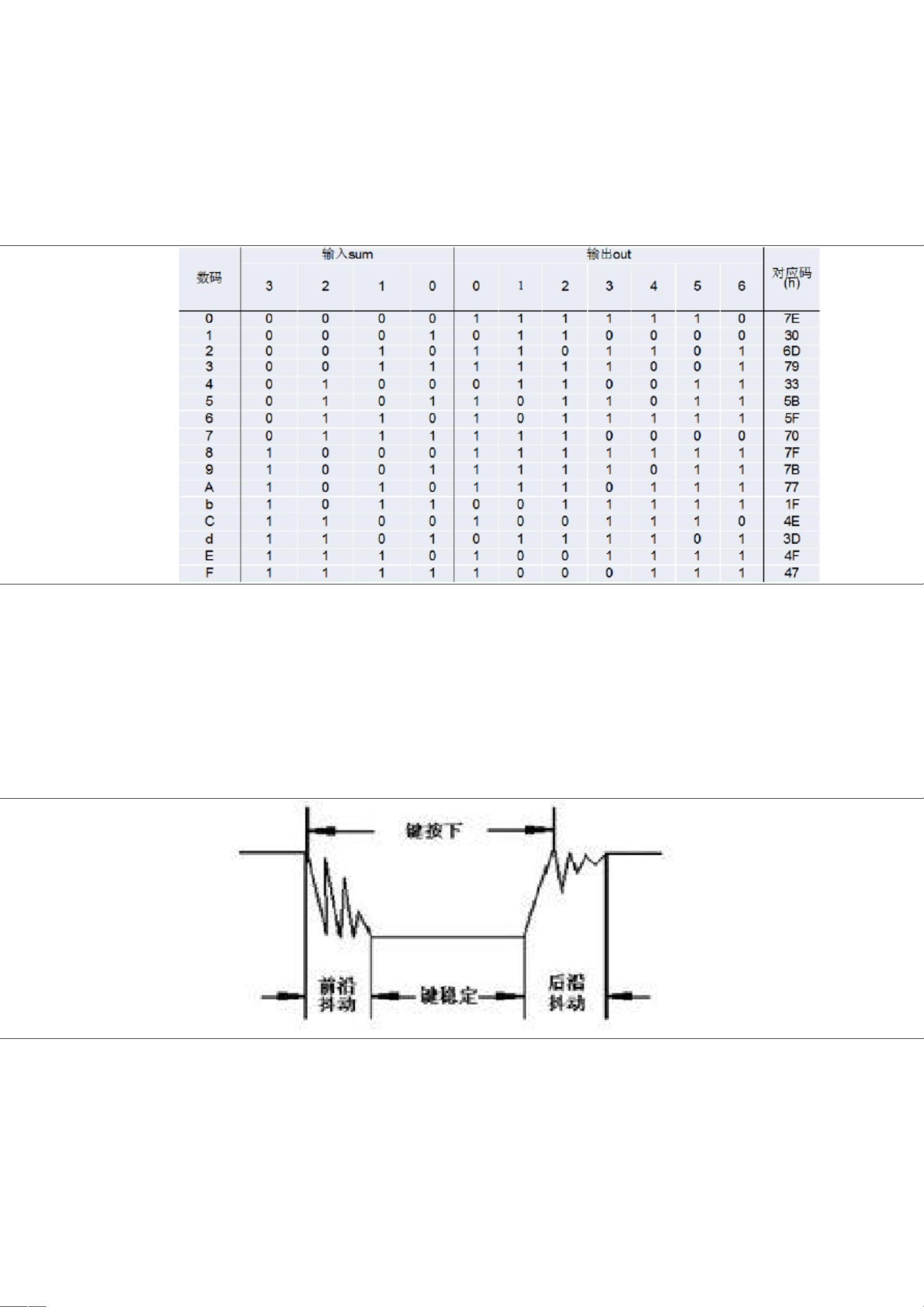

该文档详细介绍了基于HDL (Hardware Description Language) 十进制计数器的设计实验。实验的主要目的是让学生掌握Verilog HDL语言在数字电路设计中的应用,特别是组合和时序逻辑电路的设计技巧。实验内容包括设计一个具有数显输出功能的十进制计数器,其核心部分包括: 1. 实验目的: - 学习和掌握基于ISE工具的HDL设计流程。 - 熟悉并实践Verilog HDL来描述和实现数字电路逻辑。 - 理解和运用组合逻辑与时序逻辑的设计策略。 2. 实验要求: - 设计一个七段显示译码电路,以及一个能与之配合工作的十进制加法计数器。 - LED需正确显示计数器的值,包括个位和十位的进位。 - 通过仿真分析LED七段码波形,并确保在目标板上的实际操作符合设计预期。 3. 实验原理: - 采用共阴极数码管,根据时钟脉冲CLK的上升沿,计数器的值递增并在数码管上显示,同时通过cout输出十位进位信息。 - 七段显示译码器负责解读计数器的输出并控制数码管的显示。 - 消抖模块在此实验中暂不做设计,仅作为顶层设计的一部分,用于处理时钟信号的抖动问题。 4. 实验步骤: - 设计前的准备工作,明确输入和输出信号,如clk、clr、ce等。 - 实现三个主要模块:十进制计数器、七段数码管驱动模块和消抖模块。 - 十进制计数器负责处理时钟信号,通过异步清零信号CLR来控制计数状态。 - 在实际应用中,消抖模块确保时钟信号稳定,防止计数错误。 在整个实验过程中,学生需要将理论知识与实际编程相结合,通过编写和调试Verilog代码,不仅提升数字逻辑设计技能,还能加深对硬件描述语言的理解。完成这项实验后,学生将能够独立设计和实现简单的数字电路,并能有效地利用HDL工具进行电路设计和验证。

剩余19页未读,继续阅读

- 粉丝: 8457

- 资源: 2万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 多功能HTML网站模板:手机电脑适配与前端源码

- echarts实战:构建多组与堆叠条形图可视化模板

- openEuler 22.03 LTS专用openssh rpm包安装指南

- H992响应式前端网页模板源码包

- Golang标准库深度解析与实践方案

- C语言版本gRPC框架支持多语言开发教程

- H397响应式前端网站模板源码下载

- 资产配置方案:优化资源与风险管理的关键计划

- PHP宾馆管理系统(毕设)完整项目源码下载

- 中小企业电子发票应用与管理解决方案

- 多设备自适应网页源码模板下载

- 移动端H5模板源码,自适应响应式网页设计

- 探索轻量级可定制软件框架及其Http服务器特性

- Python网站爬虫代码资源压缩包

- iOS App唯一标识符获取方案的策略与实施

- 百度地图SDK2.7开发的找厕所应用源代码分享

信息提交成功

信息提交成功