VHDL实验:8421码转格雷码、数值比较器与全加器设计

"本实验手册包含了三个主要的数字逻辑实验:8421码到格雷码转换、数值比较器和全加器的设计。实验使用VHDL语言编写代码,并通过波形图仿真来验证其功能。"

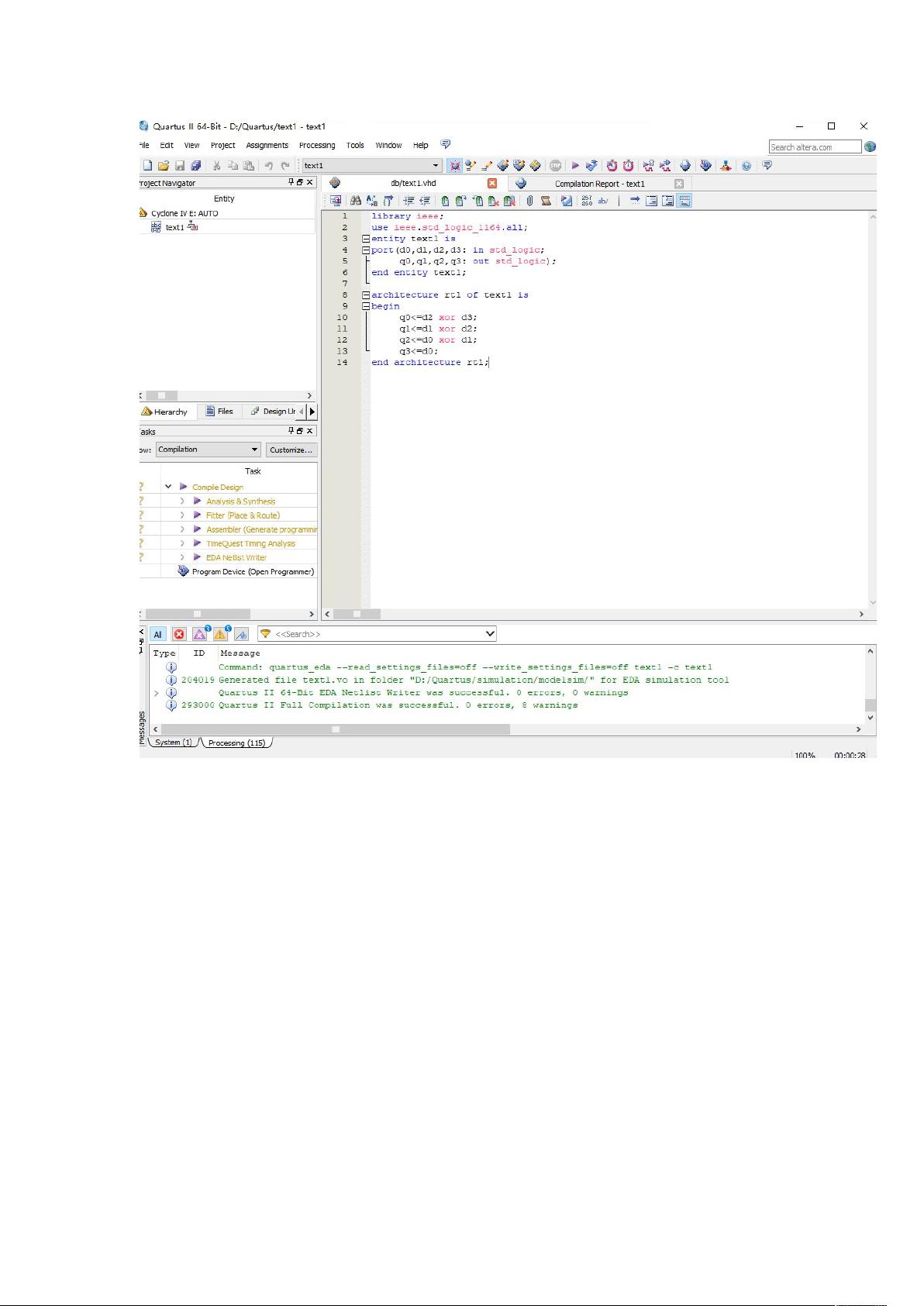

在第一个实验中,学生被要求设计一个4位的8421码到4位格雷码的编码器。8421码是一种最常见的二进制数表示方式,而格雷码(Gray Code)是一种相邻码,相邻两个数之间只有一个位不同。VHDL代码定义了一个名为`text1`的实体,它有4个输入端口`d0`, `d1`, `d2`, `d3`,对应8421码的每一位,以及4个输出端口`q0`, `q1`, `q2`, `q3`,用于输出相应的格雷码。在RTL架构中,每个格雷码位是通过与其相邻的8421码位进行异或操作得到的,这样就实现了8421码到格雷码的转换。

第二个实验涉及数值比较器,它比较两个4位二进制数`A`和`B`的大小。VHDL实体`text2`接收这两个4位输入,并产生3个输出:`YA`, `YB`, `YC`,分别表示`A`大于`B`、`A`小于`B`和`A`等于`B`的情况。通过使用`if`语句,程序根据输入的`A`和`B`比较它们的大小,并设置相应的输出。在仿真过程中,这些输出将展示出两个数的比较结果。

第三个实验是关于全加器的设计。全加器是数字逻辑中的基本单元,它考虑了进位信号,能够处理二进制加法。全加器的逻辑表达式包含3个输入(加数`Ai`,被加数`Bi`和低位进位`Ci-1`)和2个输出(和`Si`和高位进位`Ci`)。实验要求根据全加器的电路结构和真值表编写VHDL程序,然后通过仿真验证其正确性。全加器通常由2个半加器和1个或门组成,半加器仅处理两个输入的加法,不考虑进位。

这三个实验都强调了VHDL在数字逻辑设计中的应用,通过代码实现逻辑功能,并通过仿真工具验证设计的正确性。这有助于学习者掌握数字逻辑的基础知识,包括编码转换、二进制比较以及加法运算的硬件实现。

4074 浏览量

261 浏览量

2022-10-15 上传

325 浏览量

121 浏览量

115 浏览量

2022-10-29 上传

2022-10-19 上传

weixin_43835957

- 粉丝: 0

最新资源

- 虚幻引擎4经典FPS游戏开发包解析

- 掌握LaTeX中psfig.sty的使用技巧

- 探索X102 51学习板:深入嵌入式系统开发

- 深入理解STM32外部中断的实现与应用

- 大冶市数字高程模型(DEM)数据详细解读

- 俄罗斯方块游戏制作教程:Protues实现指南

- ASP.NET视频点播系统源代码及论文:多技术项目资源集锦

- Platzi JavaScript课程体系:全面覆盖初、中、高级

- cutespotify:跨平台MeeSpot音乐播放器兼容SailfishOS

- PictureEx类:在VC6下显示jpg与gif动图

- 基于stc89C51的数字时钟Proteus仿真设计

- MATLAB全面基础教程与实践技巧分享

- 实现双行文字向上滚动效果的js插件

- Labview温度报警系统:实时监控与声光警报

- Java官网ehcache-2.7.3实例教程

- A-Frame超级组件集:超帧的创新与应用