Verilog实现基本RS与JK触发器设计

需积分: 45 59 浏览量

更新于2024-08-30

2

收藏 233KB DOC 举报

本资源主要介绍了如何设计和实现基本的RS触发器以及JK触发器,以数字电路课程设计的实验报告形式呈现,适用于学习Verilog HDL语言的学生。实验设备包括个人电脑、ISE软件以及ARTIX7教学开发板。实验目标是理解和掌握RS和JK触发器的工作原理,并利用Verilog HDL进行逻辑电路的描述和建模。

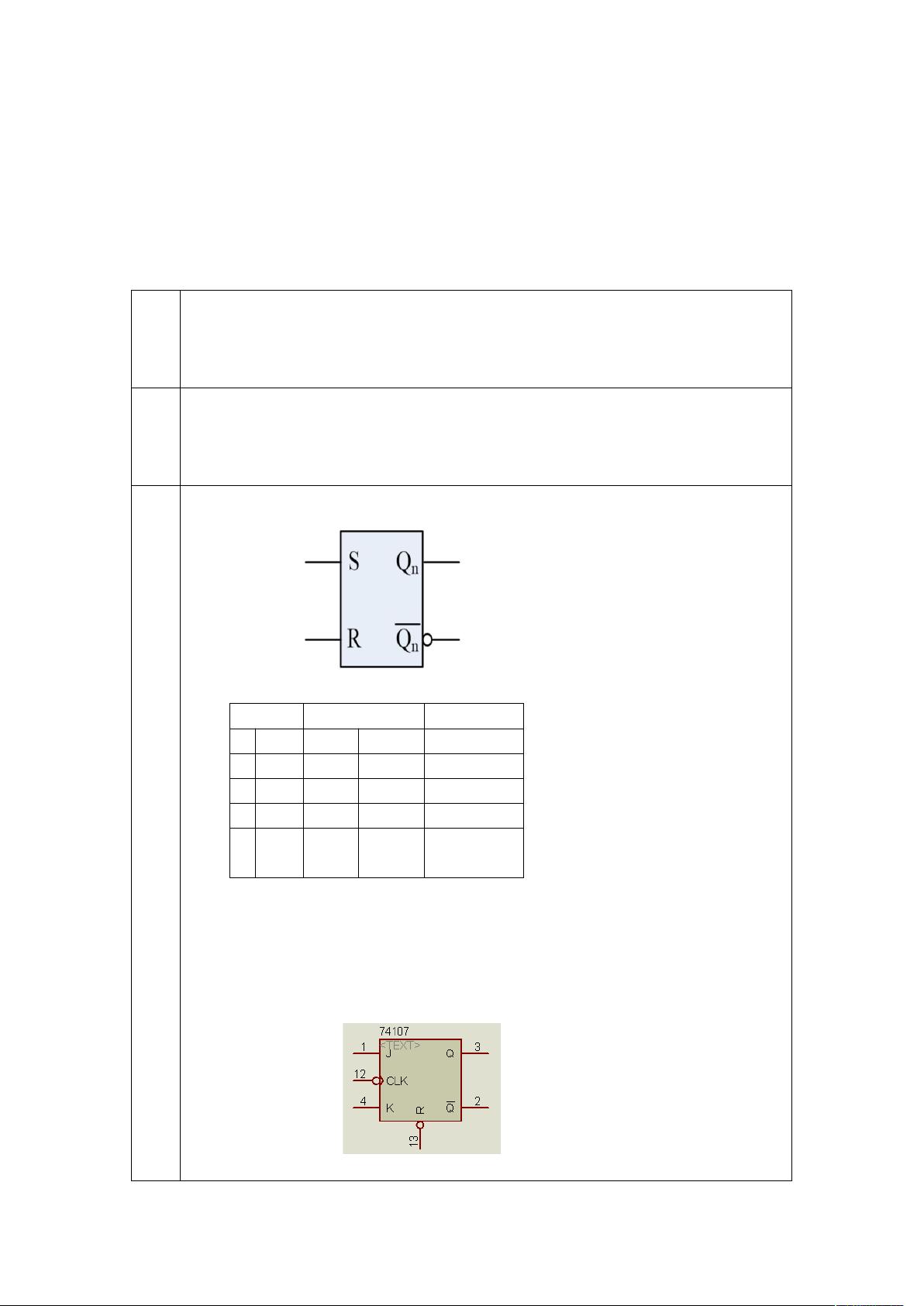

基本RS触发器

RS触发器是一种双稳态电路,由两个交叉耦合的非门或NOR门构成。在RS触发器中,"R"代表复位(Reset)输入,"S"代表置位(Set)输入,"Q"表示输出,"Qn+1"是下一个时钟周期的输出状态。根据输入S和R的不同组合,RS触发器有以下四种工作状态:

1. 当S=1,R=0时,触发器被置为1状态,Qn+1=1。

2. 当S=0,R=1时,触发器被复位为0状态,Qn+1=0。

3. 当S=0,R=0时,触发器保持当前状态,Qn+1=Qn。

4. 当S=1,R=1时,触发器进入不定状态,这称为竞争-冒险现象,应避免出现,因为它可能导致输出不稳定。

JK触发器

JK触发器是一种具有更复杂功能的边沿触发D触发器,它在时钟脉冲上升沿(CLK的上升沿有效)时根据J和K输入改变状态。JK触发器的输出状态与J和K的取值关系如下:

- 当CLK上升沿到来且J=K=0时,输出Q保持不变,即Qn+1=Qn。

- 当CLK上升沿且J=0,K=1时,输出Q被置为0,即Qn+1=0。

- 当CLK上升沿且J=1,K=0时,输出Q被置为1,即Qn+1=1。

- 当CLK上升沿且J=K=1时,输出Q的值会反转,即Qn+1=1-Qn。

JK触发器相比于RS触发器,增加了J和K输入,使得在某些应用场景下能够实现更为灵活的逻辑控制,如翻转、置0、置1或保持原状态。

Verilog HDL实现

在Verilog HDL中,可以使用always块来描述触发器的行为。对于RS触发器,可能的代码实现如下:

```verilog

module RS触发器 (

input wire R, S,

output reg Q, Qn

);

always @(posedge clk) begin

if (R == 1) begin

Q <= 0; // 复位

end else if (S == 1) begin

Q <= 1; // 置位

end else begin

Q <= Qn; // 保持

end

end

assign Qn = Q; // 输出的下一状态

endmodule

```

对于JK触发器,Verilog代码可能如下:

```verilog

module JK触发器 (

input wire clk, J, K,

output reg Q, Qn

);

always @(posedge clk) begin

if (J != K) begin

if (J) Q <= ~Q; // 翻转

else Q <= 1'b0; // K=1时置0

end else begin

Q <= Q; // 保持

end

end

assign Qn = Q; // 输出的下一状态

endmodule

```

以上代码展示了如何使用Verilog语言描述RS和JK触发器的基本逻辑行为,但实际应用中,还需要考虑时钟同步、 metastability( metastable states)等问题,以确保电路的可靠性和稳定性。

1167 浏览量

643 浏览量

102 浏览量

104 浏览量

287 浏览量

104 浏览量

谨年不开心

- 粉丝: 0

最新资源

- iBatis 2.0 开发指南:快速上手与高级特性

- Linux USB内核学习笔记

- J2EE电商系统入门精通:Struts+Hibernate实战教程

- JUnit测试框架:简化Java开发的利器

- 使用Struts2构建Web 2.0项目的实战指南

- 软件开发笔试试题解析与解答

- SWT图形用户界面教程:Java GUI开发

- 华为面试题解析:JAVA面试焦点

- Cisco路由器密码恢复步骤详解

- 面向对象分析与设计实战指南

- Quest Software's TOAD for Oracle 演示与介绍

- 《Struts in Action》中文版详解:Java Web框架深度解析

- 软件工程模式与项目管理探讨

- UML设计与软件工程实践:案例分析与工具详解

- 面向对象技术与UML方法:软件工程访谈与实践

- Core J2EE模式:最佳实践与设计策略