Intel Quartus Prime Pro Edition Timing Analyzer详解与步骤

需积分: 26 50 浏览量

更新于2024-07-15

收藏 2.27MB PDF 举报

Intel® Quartus® Prime Pro Edition User Guide 提供了关于 Timing Analyzer 的深入介绍和详细指南,适用于20.1版本的Intel® Quartus® Prime Design Suite。这份文档旨在帮助用户理解和优化他们的设计以满足时序要求,确保系统性能。

章节1主要介绍了Timing Analysis的基本概念和方法。其中包括:

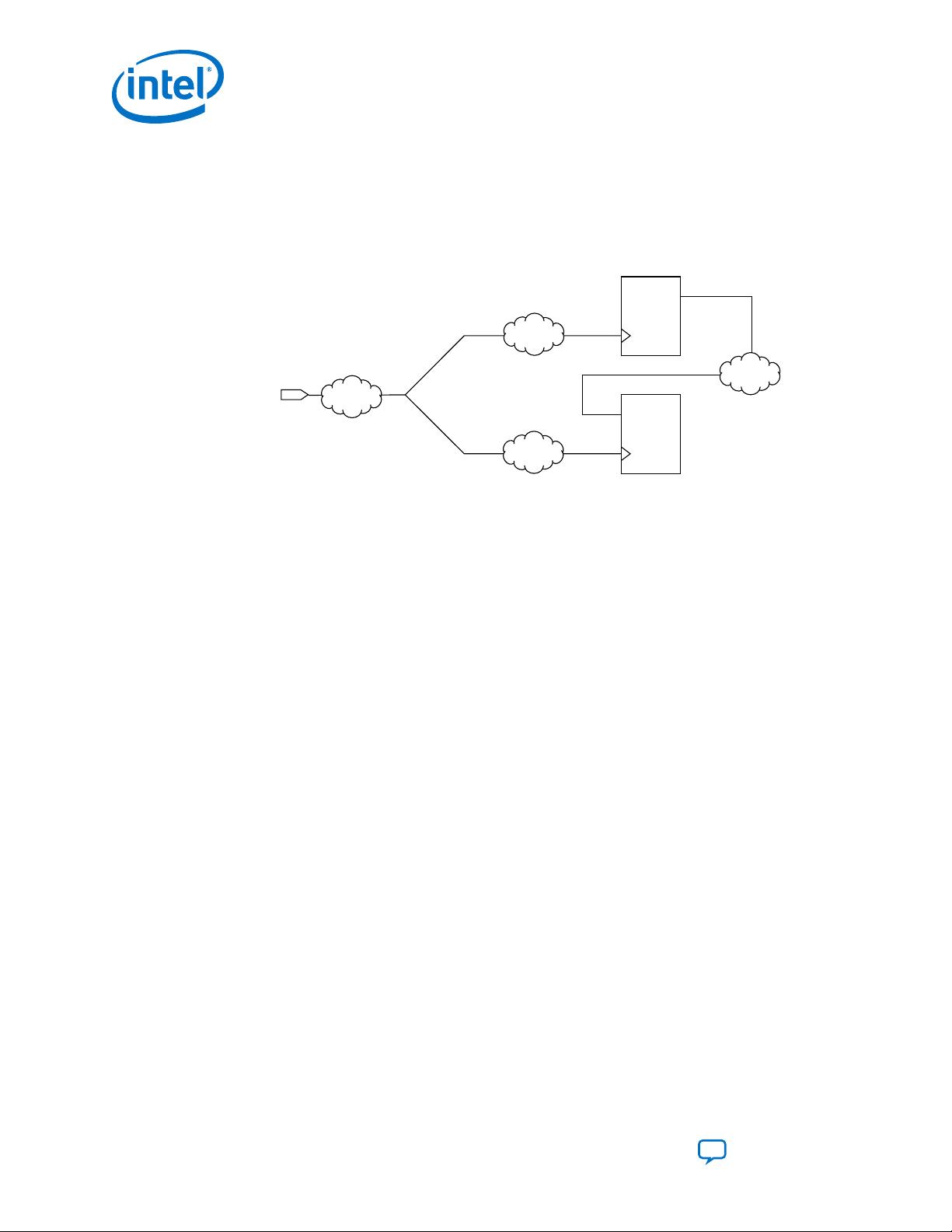

1.1 **Timing Path and Clock Analysis**:阐述了路径分析的重要性,它涉及查找和分析设计中的关键路径,即决定系统速度的最慢路径,以及确定各个路径上信号到达目标的时间。

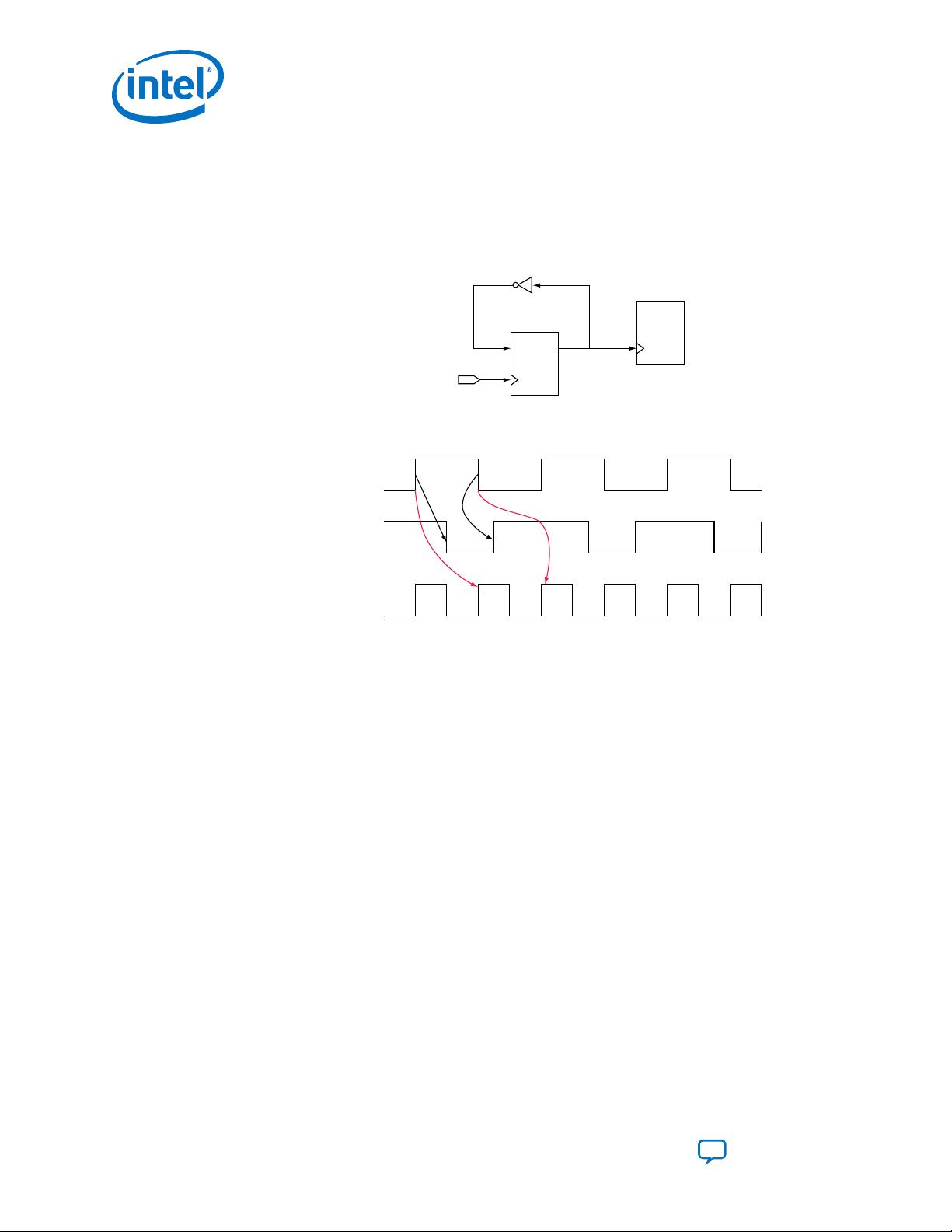

1.1.1 **Clock Setup Analysis**:讲解了在时钟上升沿之前信号必须到达目的地以避免setup violation(设置违反)的概念,这对于维持正确的逻辑行为至关重要。

1.1.2 **Clock Hold Analysis**:关注的是在时钟下降沿后信号需要保持稳定以避免hold violation(保持违反),这对防止数据丢失至关重要。

1.1.3 **Recovery and Removal Analysis**:涉及恢复时间(从故障状态恢复到正常操作所需时间)和去除时间(信号从电路中消失并重新出现所需时间),确保在错误条件下的可靠性和响应速度。

1.1.4 **Multicycle Path Analysis**:分析那些可能需要多个时钟周期完成的操作,以便提前规划和优化资源分配。

1.1.5 **Metastability Analysis**:解释了在快速时钟下,电路可能产生的暂态不稳定现象,如何通过设置metastability detection(暂稳态检测)来处理。

1.1.6 **Timing Pessimism**:讨论了设计中固有的悲观估计,即为保证最坏情况下的时序而预留的裕度,这有助于确保设计的鲁棒性。

1.1.7 **Clock-As-Data Analysis**:当时钟信号用于数据传输时,如何正确处理时钟信号本身的时间特性,避免潜在的误操作。

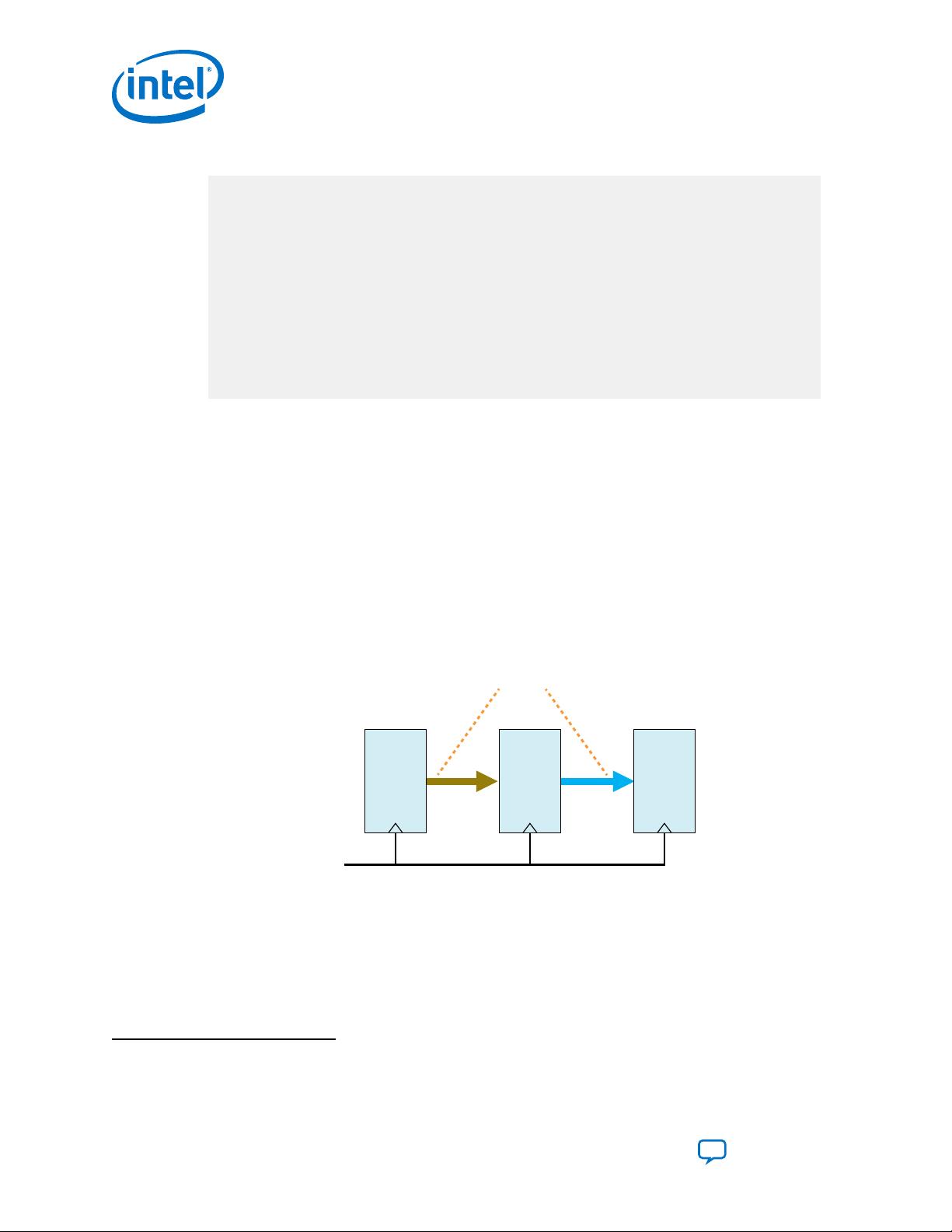

1.1.8 **Multicorner Timing Analysis**:考虑到不同工艺角(温度、电压和过程变量)对时序的影响,进行多条件下的时序分析,确保设计的广泛适应性。

1.1.9 **Time Borrowing**:一种策略,允许在满足特定条件时,从其他路径借用时间,以缓解关键路径上的紧张时序。

2. 使用 Intel Quartus Prime Timing Analyzer 的步骤详细指导了整个流程:

2.1 **Timing Analysis Flow**:从打开项目,运行布线工具,设定时序约束,到执行分析和解读结果,逐步指导用户进行时序优化。

2.2 **Using Timing Constraints**:强调了推荐的初始SDF(Synthesis Delay Format)约束,以及SDC文件的优先级设置,并讨论了迭代分析的策略。

综上,Intel Quartus Prime Pro Edition Timing Analyzer 是设计者必备的工具,它提供了全面的时序分析框架,帮助用户识别和解决设计中的时序问题,以实现高性能和可靠的集成电路设计。通过理解这些基本概念和工作流程,设计师可以更有效地管理他们的项目,并确保最终产品的性能满足规格要求。

2021-04-26 上传

2021-07-24 上传

2020-03-27 上传

2010-10-09 上传

2019-07-28 上传

2021-03-07 上传

2021-09-28 上传

ECC&SM9

- 粉丝: 120

- 资源: 1