没有合适的资源?快使用搜索试试~ 我知道了~

首页TMS320C6713BGDP数据手册

TMS320C6713BGDP数据手册

和众达SEED-DEC6713开发板的DSP芯片就是TMS320C6713BGDP,这是这块芯片的数据手册!

资源详情

资源评论

资源推荐

TMS320C6713, TMS320C6713B

FLOATING-POINT DIGITAL SIGNAL PROCESSORS

SPRS186I − DECEMBER 2001 − REVISED MAY 2004

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

D Highest-Performance Floating-Point Digital

Signal Processors (DSPs): C6713/C6713B

− Eight 32-Bit Instructions/Cycle

− 32/64-Bit Data Word

− 300-, 225-, 200-MHz (GDP), and 200-,

167-MHz (PYP) Clock Rates

− 3.3-, 4.4-, 5-, 6-Instruction Cycle Times

− 2400/1800, 1800 /1350 , 1600 /1200 , and

1336 /1000 MIPS /MFLOPS

− Rich Peripheral Set, Optimized for Audio

− Highly Optimized C/C++ Compiler

D Advanced Very Long Instruction Word

(VLIW) TMS320C67x DSP Core

− Eight Independent Functional Units:

− Two ALUs (Fixed-Point)

− Four ALUs (Floating- and Fixed-Point)

− Two Multipliers (Floating- and

Fixed-Point)

− Load-Store Architecture With 32 32-Bit

General-Purpose Registers

− Instruction Packing Reduces Code Size

− All Instructions Conditional

D Instruction Set Features

− Native Instructions for IEEE 754

− Single- and Double-Precision

− Byte-Addressable (8-, 16-, 32-Bit Data)

− 8-Bit Overflow Protection

− Saturation; Bit-Field Extract, Set, Clear;

Bit-Counting; Normalization

D L1/L2 Memory Architecture

− 4K-Byte L1P Program Cache

(Direct-Mapped)

− 4K-Byte L1D Data Cache (2-Way)

− 256K-Byte L2 Memory Total: 64K-Byte

L2 Unified Cache/Mapped RAM, and

192K-Byte Additional L2 Mapped RAM

D Device Configuration

− Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

− Endianness: Little Endian, Big Endian

D 32-Bit External Memory Interface (EMIF)

− Glueless Interface to SRAM, EPROM,

Flash, SBSRAM, and SDRAM

− 512M-Byte Total Addressable External

Memory Space

D Enhanced Direct-Memory-Access (EDMA)

Controller (16 Independent Channels)

D 16-Bit Host-Port Interface (HPI)

D Two Multichannel Audio Serial Ports

(McASPs)

− Two Independent Clock Zones Each

(1 TX and 1 RX)

− Eight Serial Data Pins Per Port:

Individually Assignable to any of the

Clock Zones

− Each Clock Zone Includes:

− Programmable Clock Generator

− Programmable Frame Sync Generator

− TDM Streams From 2-32 Time Slots

− Support for Slot Size:

8, 12, 16, 20, 24, 28, 32 Bits

− Data Formatter for Bit Manipulation

− Wide Variety of I2S and Similar Bit

Stream Formats

− Integrated Digital Audio Interface

Transmitter (DIT) Supports:

− S/PDIF, IEC60958-1, AES-3, CP-430

Formats

− Up to 16 transmit pins

− Enhanced Channel Status/User Data

− Extensive Error Checking and Recovery

D Two Inter-Integrated Circuit Bus (I

2

C Bus)

Multi-Master and Slave Interfaces

D Two Multichannel Buffered Serial Ports:

− Serial-Peripheral-Interface (SPI)

− High-Speed TDM Interface

− AC97 Interface

D Two 32-Bit General-Purpose Timers

D Dedicated GPIO Module With 16 pins

(External Interrupt Capable)

D Flexible Phase-Locked-Loop (PLL) Based

Clock Generator Module

D IEEE-1149.1 (JTAG

†

)

Boundary-Scan-Compatible

D Package Options:

− 208-Pin PowerPAD Plastic (Low-Profile)

Quad Flatpack (PYP)

− 272-Ball, Ball Grid Array Package (GDP)

D 0.13-µm/6-Level Copper Metal Process

− CMOS Technology

D 3.3-V I/Os, 1.2

‡

-V Internal (GDP & PYP)

D 3.3-V I/Os, 1.4-V Internal (GDP) (300 MHz

only)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This document contains information on products in more than one phase

of development. The status of each device is indicated on the page(s)

specifying its electrical characteristics.

Copyright 2004, Texas Instruments Incorporated

TMS320C67x and PowerPAD are trademarks of Texas Instruments.

I

2

C Bus is a trademark of Philips Electronics N.V. Corporation

All trademarks are the property of their respective owners.

†

IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

‡

These values are compatible with existing 1.26V designs.

TMS320C6713, TMS320C6713B

FLOATING-POINT DIGITAL SIGNAL PROCESSORS

SPRS186I − DECEMBER 2001 − REVISED MAY 2004

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

Table of Contents

EMIF device speed 93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EMIF big endian mode correctness [C6713B only] 95. . .

bootmode 96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

absolute maximum ratings over operating case

temperature range 97. . . . . . . . . . . . . . . . . . . . . . . . . .

recommended operating conditions 98. . . . . . . . . . . . . . . .

electrical characteristics over recommended ranges of

supply voltage and operating case temperature 99.

parameter measurement information 100. . . . . . . . . . . . . .

signal transition levels 100. . . . . . . . . . . . . . . . . . . . . . . . . . .

timing parameters and board routing analysis 101. . . . . .

input and output clocks 103. . . . . . . . . . . . . . . . . . . . . . . . . .

asynchronous memory timing 107. . . . . . . . . . . . . . . . . . . .

synchronous-burst memory timing 110. . . . . . . . . . . . . . . .

synchronous DRAM timing 112. . . . . . . . . . . . . . . . . . . . . . .

HOLD

/HOLDA timing 118. . . . . . . . . . . . . . . . . . . . . . . . . . .

BUSREQ timing 119. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

reset timing 120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

external interrupt timing 122. . . . . . . . . . . . . . . . . . . . . . . . .

multichannel audio serial port (McASP) timing 123. . . . . .

inter-integrated circuits (I2C) timing 126. . . . . . . . . . . . . . .

host-port interface timing 129. . . . . . . . . . . . . . . . . . . . . . . .

multichannel buffered serial port timing 133. . . . . . . . . . . .

timer timing 143. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

general-purpose input/output (GPIO) port timing 144. . . .

JTAG test-port timing 145. . . . . . . . . . . . . . . . . . . . . . . . . . .

mechanical data 146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

revision history 149. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

GDP 272-Ball BGA package (bottom view) 3. . . . . . . . . . . . .

PYP PowerPAD QFP package (top view) 8. . . . . . . . . . . . .

description 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

device characteristics 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

functional block and CPU (DSP core) diagram 12. . . . . . . . . .

CPU (DSP core) description 13. . . . . . . . . . . . . . . . . . . . . . . . .

memory map summary 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

peripheral register descriptions 17. . . . . . . . . . . . . . . . . . . . . . .

signal groups description 26. . . . . . . . . . . . . . . . . . . . . . . . . . . .

device configurations 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

configuration examples 38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

debugging considerations 45. . . . . . . . . . . . . . . . . . . . . . . . . . .

terminal functions 46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

development support 62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

documentation support 65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CPU CSR register description 66. . . . . . . . . . . . . . . . . . . . . . . .

cache configuration (CCFG) register description (13B) 68. . .

interrupts and interrupt selector 69. . . . . . . . . . . . . . . . . . . . . . .

external interrupt sources 71. . . . . . . . . . . . . . . . . . . . . . . . . . . .

EDMA module and EDMA selector 72. . . . . . . . . . . . . . . . . . . .

PLL and PLL controller 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

multichannel audio serial port (McASP) peripherals 82. . . . .

I2C 87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

general-purpose input/output (GPIO) 88. . . . . . . . . . . . . . . . . .

power-down mode logic 89. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

power-supply sequencing 91. . . . . . . . . . . . . . . . . . . . . . . . . . . .

power-supply decoupling 92. . . . . . . . . . . . . . . . . . . . . . . . . . . .

IEEE 1149.1 JTAG compatibility statement 92. . . . . . . . . . . . .

TMS320C6713, TMS320C6713B

FLOATING-POINT DIGITAL SIGNAL PROCESSORS

SPRS186I − DECEMBER 2001 − REVISED MAY 2004

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

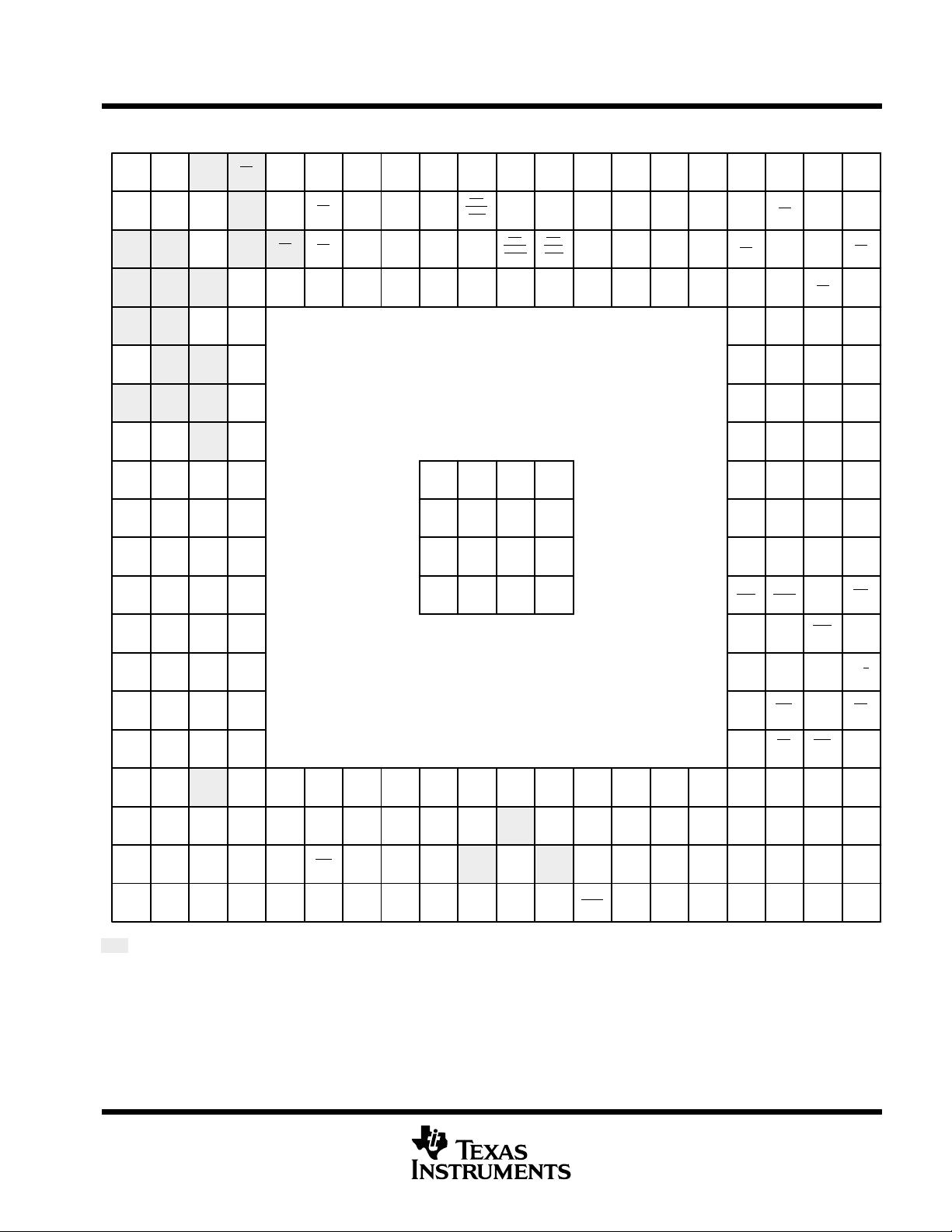

GDP 272-Ball BGA package (bottom view)

V

SS

V

SS

CLKIN CV

DD

V

SS

V

SS

V

SS

CV

DD

DV

DD

CE2

EA4

DV

DD

ED17

EA6 DV

DD

EA13

V

SS

EA15

EA19

CE1

CV

DD

V

SS

GP[5]

(EXT_INT5)/

AMUTEIN0

GP[4]/

(EXT_INT4)/

AMUTEIN1

CV

DD

ED16

BE3

CE3 EA3 EA5 EA8 EA10

EMU4 RSV NMI

EA12

DV

DD

HD9/

GP[9]

HD6/

AHCLKR1

CV

DD

HD4/

GP[0]

HD3/

AMUTE1

ED20

ED19

CV

DD

CLK

MODE0

PLLHV

ARE

/

SDCAS/

SSADS

DV

DD

HD14/

GP[14]

HD12/

GP[12]

CV

DD

DV

DD

V

SS

CV

DD

DV

DD

RSV

V

SS

TRST TMS

EMU1

DV

DD

AOE/

SDRAS

/

SSOE

V

SS

DV

DD

EA11

HD15/

GP[15]

HD10/

GP[10]

V

SS

HD8/

GP[8]

HD5/

AHCLKX1

CV

DD

V

SS

V

SS

V

SS

ED18 BE2

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

1 23 45 67 89 1011121314151617181920

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

V

SS

AWE/

SDWE/

SSWE

RSV

TCK

TDI TDO CV

DD

CV

DD

V

SS

RESET

V

SS

HD13/

GP[13]

HD11/

GP[11]

DV

DD

HD7/

GP[3]

RSV

DV

DD

EA7 EA9 V

SS

EA14 EA16 EA18 DV

DD

EA20EA2

ARDY

ECLKOUT

ECLKIN

CLKOUT2/

GP[2]

EMU3

RSV

EMU5

BE0

DV

DD

CE0

CV

DD

EA17

V

SS

V

SS

V

SS

DV

DD

EMU2

V

SS

DV

DD

CV

DD

DV

DD

V

SS

V

SS

CV

DD

CV

DD

DV

DD

V

SS

CV

DD

CV

DD

DV

DD

V

SS

EA21 BE1 V

SS

V

SS

CV

DD

CV

DD

RSV V

SS

EMU0 CLKOUT3 CV

DD

RSV V

SS

CV

DD

CV

DD

DV

DD

V

SS

HD2/

AFSX1

DV

DD

HD1/

AXR1[7]

ED22 ED21 ED23

GP[6]

(EXT_INT6)

CLKS1/

SCL1

V

SS

GP[7]

(EXT_INT7)

V

SS

V

SS

ED13 ED15 ED14

V

SS

V

SS

HDS1/

AXR1[6]

HAS/

ACLKX1

HD0/

AXR1[4]

ED24 ED25 DV

DD

CV

DD

DV

DD

ED27 ED26

CV

DD

HDS2/

AXR1[5]

V

SS

HCS/

AXR1[2]

TOUT1/

AXR0[4]

TINP1/

AHCLKX0

DV

DD

CV

DD

CV

DD

DV

DD

ED11 ED12

TOUT0/

AXR0[2]

TINP0/

AXR0[3]

CLKX0/

ACLKX0

V

SS

V

SS

ED9 V

SS

ED10

V

SS

ED28 ED29 ED30

V

SS

HCNTL0/

AXR1[3]

HCNTL1/

AXR1[1]

HR/W/

AXR1[0]

FSX0/

AFSX0

SDA0 V

SS

V

SS

ED6 ED7 ED8

CLKR0/

ACLKR0

V

SS

DX0/

AXR0[1]

SCL0 ED31

V

SS

DV

DD

HRDY/

ACLKR1

HHWIL/

AFSR1

FSR0/

AFSR0

CLKR1/

AXR0[6]

DR1/

SDA1

V

SS

V

SS

DV

DD

ED4 ED5

DR0/

AXR0[0]

DV

DD

V

SS

FSR1/

AXR0[7]

HOLD

HOLDA

BUS

REQ

HINT/

GP[1]

FSX1

DX1/

AXR0[5]

CLKX1/

AMUTE0

CV

DD

CV

DD

ED2 ED3 CV

DD

CV

DD

V

SS

CLKS0/

AHCLKR0

CV

DD

CV

DD

ED0 ED1 V

SS

Shading denotes the GDP package pin functions that drop out on the PYP package.

TMS320C6713, TMS320C6713B

FLOATING-POINT DIGITAL SIGNAL PROCESSORS

SPRS186I − DECEMBER 2001 − REVISED MAY 2004

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

GDP 272-Ball BGA package (bottom view) (continued)

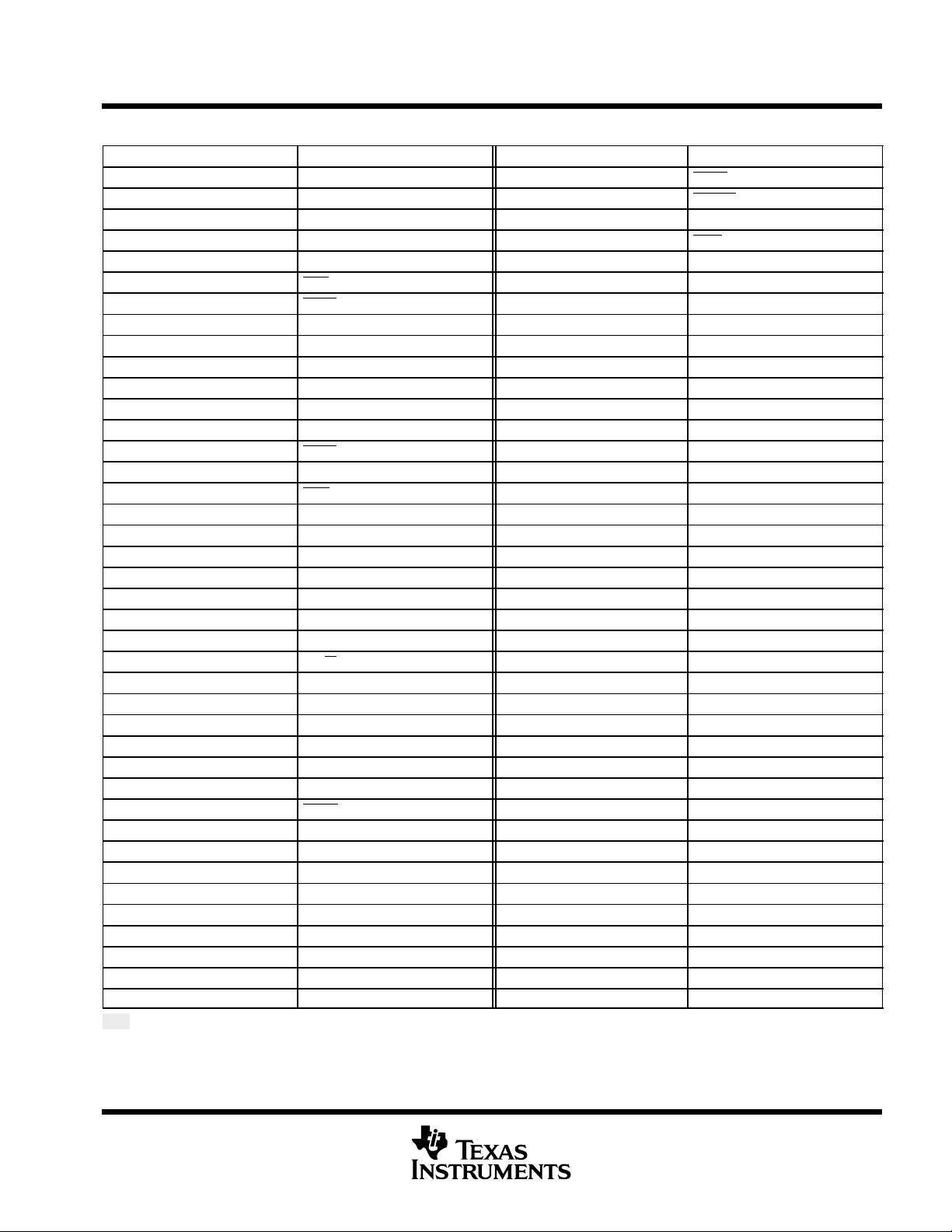

Table 1. Terminal Assignments for the 272-Ball GDP Package (in Order of Ball No.)

BALL NO. SIGNAL NAME BALL NO. SIGNAL NAME

A1 V

SS

C1 GP[5](EXT_INT5)/AMUTEIN0

A2 V

SS

C2 GP[4](EXT_INT4)/AMUTEIN1

A3 CLKIN C3 CV

DD

A4 CV

DD

C4 CLKMODE0

A5 RSV C5 PLLHV

A6 TCK C6 V

SS

A7 TDI C7 CV

DD

A8 TDO C8 V

SS

A9 CV

DD

C9 V

SS

A10 CV

DD

C10 DV

DD

A11 V

SS

C11 EMU4

A12 RSV C12 RSV

A13 RESET C13 NMI

A14 V

SS

C14 HD14/GP[14]

A15 HD13/GP[13] C15 HD12/GP[12]

A16 HD11/GP[11] C16 HD9/GP[9]

A17 DV

DD

C17 HD6/AHCLKR1

A18 HD7/GP[3] C18 CV

DD

A19 V

SS

C19 HD4/GP[0]

A20 V

SS

C20 HD3/AMUTE1

B1 V

SS

D1 DV

DD

B2 CV

DD

D2 GP[6](EXT_INT6)

B3 DV

DD

D3 EMU2

B4 V

SS

D4 V

SS

B5 RSV D5 CV

DD

B6 TRST D6 CV

DD

B7 TMS D7 RSV

B8 DV

DD

D8 V

SS

B9 EMU1 D9 EMU0

B10 EMU3 D10 CLKOUT3

B11 RSV D11 CV

DD

B12 EMU5 D12 RSV

B13 DV

DD

D13 V

SS

B14 HD15/GP[15] D14 CV

DD

B15 V

SS

D15 CV

DD

B16 HD10/GP[10] D16 DV

DD

B17 HD8/GP[8] D17 V

SS

B18 HD5/AHCLKX1 D18 HD2/AFSX1

B19 CV

DD

D19 DV

DD

B20 V

SS

D20 HD1/AXR1[7]

Shading denotes the GDP package pin functions that drop out on the PYP package.

TMS320C6713, TMS320C6713B

FLOATING-POINT DIGITAL SIGNAL PROCESSORS

SPRS186I − DECEMBER 2001 − REVISED MAY 2004

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

Table 1. Terminal Assignments for the 272-Ball GDP Package (in Order of Ball No.) (Continued)

BALL NO. SIGNAL NAME BALL NO. SIGNAL NAME

E1 CLKS1/SCL1 J17 HOLD

E2 V

SS

J18 HOLDA

E3 GP[7](EXT_INT7) J19 BUSREQ

E4 V

SS

J20 HINT/GP[1]

E17 V

SS

K1 CV

DD

E18 HAS/ACLKX1 K2 V

SS

E19 HDS1/AXR1[6] K3 CLKS0/AHCLKR0

E20 HD0/AXR1[4] K4 CV

DD

F1 TOUT1/AXR0[4] K9 V

SS

F2 TINP1/AHCLKX0 K10 V

SS

F3 DV

DD

K11 V

SS

F4 CV

DD

K12 V

SS

F17 CV

DD

K17 CV

DD

F18 HDS2/AXR1[5] K18 ED0

F19 V

SS

K19 ED1

F20 HCS/AXR1[2] K20 V

SS

G1 TOUT0/AXR0[2] L1 FSX1

G2 TINP0/AXR0[3] L2 DX1/AXR0[5]

G3 CLKX0/ACLKX0 L3 CLKX1/AMUTE0

G4 V

SS

L4 CV

DD

G17 V

SS

L9 V

SS

G18 HCNTL0/AXR1[3] L10 V

SS

G19 HCNTL1/AXR1[1] L11 V

SS

G20 HR/W/AXR1[0] L12 V

SS

H1 FSX0/AFSX0 L17 CV

DD

H2 DX0/AXR0[1] L18 ED2

H3 CLKR0/ACLKR0 L19 ED3

H4 V

SS

L20 CV

DD

H17 V

SS

M1 CLKR1/AXR0[6]

H18 DV

DD

M2 DR1/SDA1

H19 HRDY/ACLKR1 M3 FSR1/AXR0[7]

H20 HHWIL/AFSR1 M4 V

SS

J1 DR0/AXR0[0] M9 V

SS

J2 DV

DD

M10 V

SS

J3 FSR0/AFSR0 M11 V

SS

J4 V

SS

M12 V

SS

J9 V

SS

M17 V

SS

J10 V

SS

M18 DV

DD

J11 V

SS

M19 ED4

J12 V

SS

M20 ED5

Shading denotes the GDP package pin functions that drop out on the PYP package.

剩余149页未读,继续阅读

gujunyi66

- 粉丝: 7

- 资源: 26

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2