嵌入式开发:ARM体系下的中断与DMA比较及中断处理机制详解

需积分: 9 142 浏览量

更新于2024-08-04

1

收藏 830KB DOCX 举报

嵌入式开发中的ARM体系与架构在23届秋招中备受关注,特别是针对中断与异常处理、DMA技术以及中断处理的分工。ARM体系架构下,中断与异常是两种不同的信号处理机制。

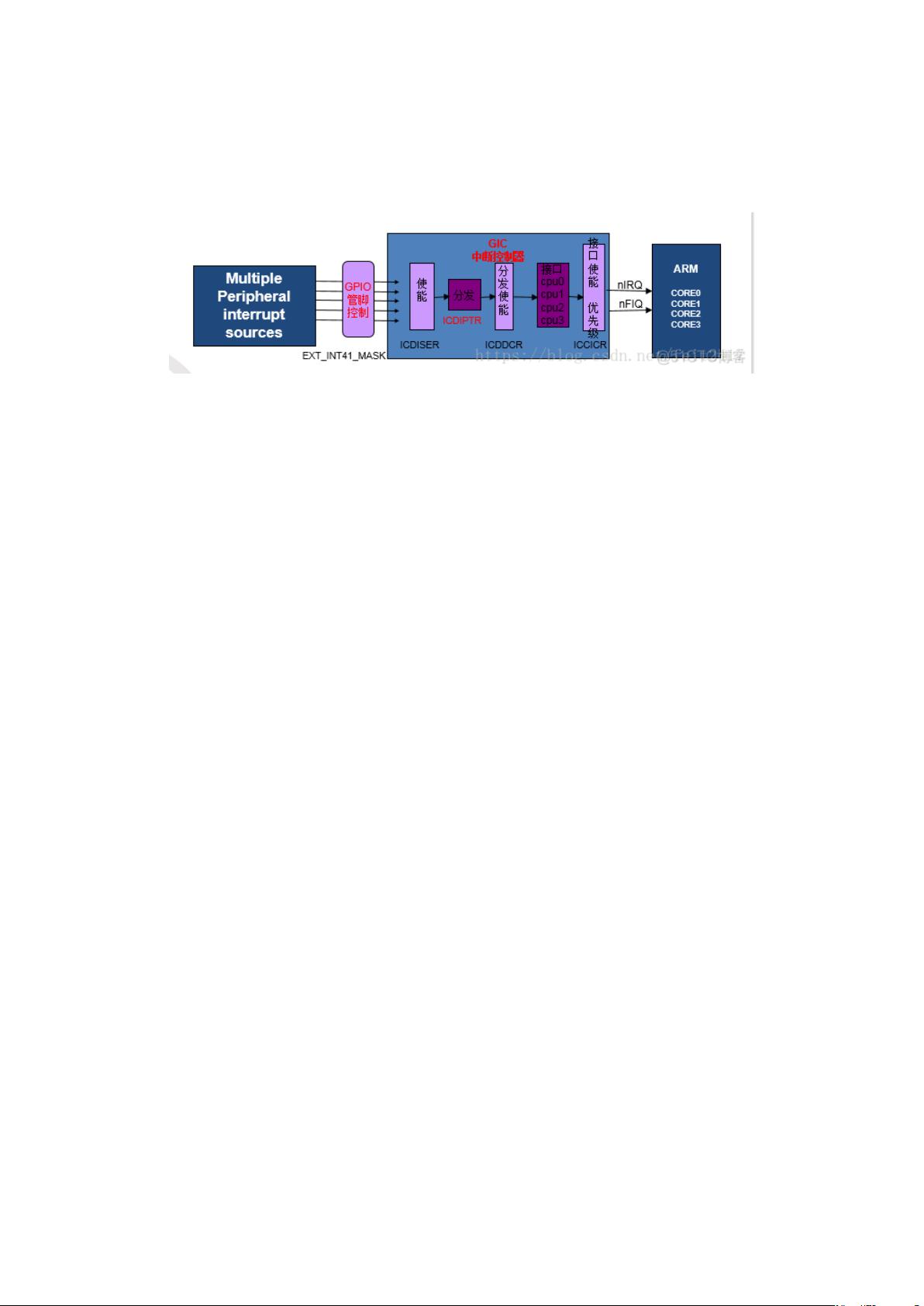

中断(Interrupt)是当系统中外部硬件检测到特定事件时,通过中断请求线向CPU发送信号,迫使CPU暂时停止当前任务,进入中断处理模式。这个过程是被动的,CPU会在中断上半部保存现场,切换到FIQ(快速中断)或IRQ(标准中断)模式,然后通过中断向量表找到对应的中断服务函数(ISR,Interrupt Service Routine)执行,处理完事件后再返回原点继续执行。中断上半部通常处理快速且重要的任务,如定时器或串口接收,但需注意,长时间执行可能影响系统性能。

异常(Exception)则源于软件运行过程中遇到的特殊情况,如编译错误、处理器内部错误等,这些事件会导致CPU自动产生一个异常,类似于同步中断。异常处理需确保与处理器时钟同步,通常由内核负责,因此对系统稳定性至关重要。异常也要求中断服务函数能够正确处理并恢复执行流程。

DMA(Direct Memory Access)技术是一种无需CPU直接介入的数据传输方式,外设可以直接和系统内存交换数据,提高了数据传输效率和系统的吞吐量。相比中断,DMA的特点在于它能在CPU处理其他任务的同时完成数据传输,避免了CPU频繁中断导致的性能损失。

中断处理分为上半部和下半部,上半部处理的是快速、不耗时的任务,而下半部用于执行耗时操作,如设备驱动程序中的复杂操作。目前,中断下半部的实现机制有软中断(Soft Interrupt)、tasklets和工作队列(Work Queues)。软中断是一种特殊的中断类型,包括硬件中断和内核自定义事件,如调度和RCU锁管理,它们是“可延迟函数”,运行在中断上下文中,不可阻塞、并发执行,并且必须是可重入的,以防止数据竞争。

总结来说,嵌入式开发中理解ARM体系的中断与异常机制,以及如何有效利用DMA和中断处理机制,对于提升系统性能和稳定运行至关重要。熟练掌握这些概念有助于求职者在秋招面试中脱颖而出。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-06-20 上传

2019-06-26 上传

2023-08-14 上传

2021-10-16 上传

2022-09-26 上传

点击了解资源详情

剑锋-

- 粉丝: 22

- 资源: 5

最新资源

- cpp_from_control_to_objects_8e:从C到对象,从控制结构开始,第8版

- import:R的导入机制

- vue2+vue-router+es6+webpack+node+mongodb的项目.zip

- Golang中的神经网络+培训框架-Golang开发

- 仅在页脚部分的最后一页的最底部打印表格页脚

- mac-config:Brewfile和脚本来设置全新的Mac安装

- writexl:轻巧的便携式数据帧,用于R的xlsx导出器

- Bootstrap模态登录框

- exif_read.rar_图形图像处理_Visual_C++_

- 福橘-股票行情-crx插件

- :magnifying_glass_tilted_right::bug:Golang fmt.Println调试和跟踪工具,能够可视化函数调用路径。-Golang开发

- 投资组合:我的个人投资组合以及由React提供的Dot Net服务器

- streamy-server

- voices:p5.js小实验

- New Tab Wallpaper-crx插件

- xml-website:监控项目的网站