Allegro HDL原理图创建与元器件设计指南

下载需积分: 16 | PDF格式 | 879KB |

更新于2024-08-05

| 89 浏览量 | 举报

"Allegro HDL原理图操作流程"

在电子设计自动化(EDA)领域,Cadence Allegro是一款广泛使用的PCB设计工具,其Entry HDL模块则专门用于绘制和编辑电路原理图。以下是对Allegro Entry HDL原理图操作流程的详细说明:

1. 创建原理图:

首先,你需要配置库路径,这通常通过设置cds.lib文件来完成。工程管理文档使用.cpm后缀,并通过Project Manager打开。对于创建原理图,有两种选择:XL(Legacy)和LibrarianXL。XL主要用于常规操作,而LibrarianXL则在创建原理图封装时提供预览功能。

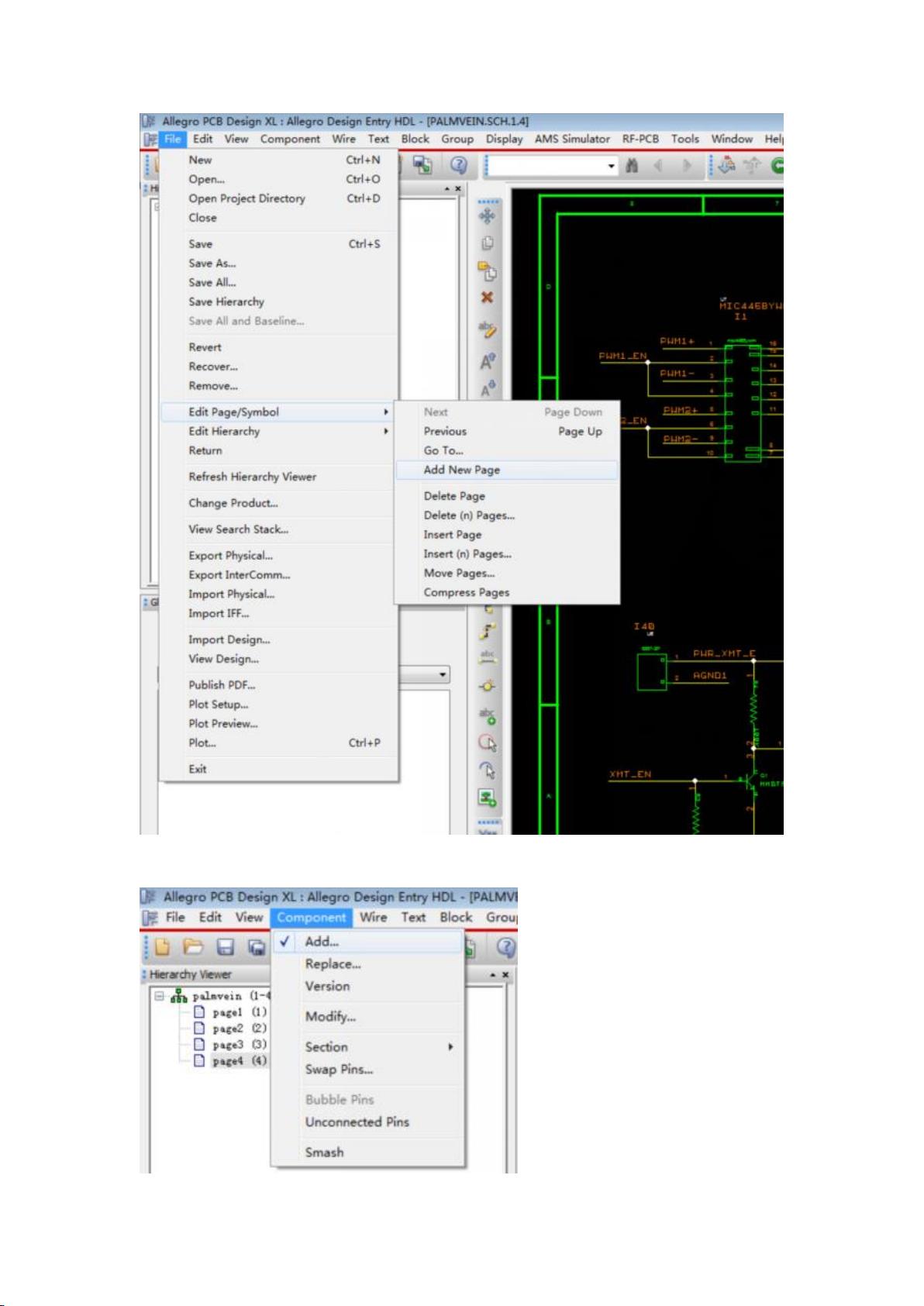

- 添加或删除原理图页面:在File > Edit > Page/Symbol菜单中进行操作。新添加的页面最初会显示为黑色,只有保存后才会显示内容。

- 添加器件:可以通过点击“Add”按钮或在Part Name下选择器件并点击“Add”,将器件添加到原理图中。

- 绘制信号线:使用Draw工具可以绘制连接器件的信号线。

- 器件操作:在Edit菜单中,你可以对器件进行各种操作,如旋转、镜像等。

- 群组操作:通过右键点击空白区域,可以调出群组操作快捷按钮,方便批量移动或复制多个对象。

2. 创建新的元器件原理图:

- 更改工程类型:在工程管理界面,将工程类型更改为LibrarianXL。

- 创建器件:在Part Developer中,选择器件类型,命名并点击“New”。接着,定义Class类型和REFDES丝印,例如,U表示集成电路,C表示电容,D表示二极管,L表示电感,J表示接插件,R表示电阻,T表示变压器。

- 添加引脚:在PackagePin中,通过Pins > Add添加引脚,并为每个引脚指定对应的原理图引脚名。

- 映射物理封装:确保引脚数目与物理封装匹配,然后进行映射操作,确保每个引脚名称正确。

- 生成器件符号:点击“Generate Symbol(s)”生成器件的原理图符号。

- 调整引脚位置:在预览模式下,可以手动调整器件引脚的位置,确保符合实际布局需求。

- 创建pptfile:最后,为器件创建pptfile,通过右键点击Part Table Files,新建Header并填写关键属性。

通过以上步骤,你可以在Allegro Entry HDL中创建并编辑复杂的电路原理图。理解并熟练掌握这些操作对于高效地进行PCB设计至关重要。在设计过程中,确保每个步骤的准确性,避免后期出现设计错误,这对于整个电子产品的性能和可靠性至关重要。

相关推荐

我论文写不出来

- 粉丝: 3

- 资源: 3

最新资源

- 基于STM32硬件IIC DMA传输的SSD1306 OLED屏的高级应用程序

- 唯美创意PPT.zip

- witness:用于识别《见证人》中拼图模式的深度学习模型

- Free Password Manager & Authenticator & SSO-crx插件

- apkeasytool反编译工具

- automaticSkilledReaching_arduino:为Leventhal实验室中使用的鼠标单颗粒熟练触及盒开发的Arduino代码

- NSIS安装工具.rar

- torch_sparse-0.6.5-cp37-cp37m-linux_x86_64whl.zip

- 二级图文平滑下拉菜单

- IPVT Screen Capturing-crx插件

- hypothesis-gufunc:扩展假设以测试numpy通用函数

- 电信设备-基于移动终端的用户衣橱服饰管理方法.zip

- video downloadhelper 7.4及VdhCoAppSetup-1.5.0.exe

- 组合:来自训练营的项目组合

- 顶部固定、二级栏目之间相互滑动的导航菜单

- LJSuperScanParse