首页

pcie总线标准协议中文版

pcie总线标准协议中文版

时间: 2023-08-11 10:08:02

浏览: 502

PCIe总线标准协议中文版是一种电脑总线标准,用于连接外部设备和计算机主板,提供高速数据传输和通信。其最新版本是PCIe 5.0,其协议标准包括物理层、数据链路层、传输层和应用层。该协议支持多种传输速率,可达到每秒32GB/s的传输速度,并且具有高可靠性和可扩展性。PCIe总线标准协议中文版的详细规范可以在PCI-SIG(PCI Special Interest Group)官网上获取。

相关推荐

PCIE2.0总线规范

PCIE2.0总线规范

PCIE规范.rar

收集的PCIE规范: PCIE Base 规范4.0 PCIE 卡电气规范 1.0a, 1,1, 3.0 PCIE Mini 卡电气规范 1.2 对于想了解 PCIE 的技术人员,可以参考一下哦!

pcie中文详解

超级详细的pcie中文文档

PCIe总线接口与高速数据传输

PCIe总线接口概述 PCIe(Peripheral Component Interconnect Express)总线接口是一种用于连接扩展卡、显卡等外围设备到计算机主板的接口标准,其采用高速串行通信技术,为现代计算机系统提供了高效、可靠的数据...

pcie处理层协议中文详解.pdf

这是翻译的PCIE协议处理层的相关的中文解释。 这里对原版英文PCIE 协议处理层的部分做了翻译,并且做了相关的理解。对于学习者来说应该会有比较大的帮助。希望帮助初学者能够很好的学习PCIE

pcie 协议 5.0

开源pcie 5.0 官方文档 PCI, PCI Express, PCIe, and PCI-SIG are trademarks or registered trademarks of PCI-SIG. All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

pcie3.0规范

OBJECTIVE OF THE SPECIFICATION.................................................................................... 27 DOCUMENT ORGANIZATION ................................................................................................ 27 DOCUMENTATION CONVENTIONS...................................................................................... 28 TERMS AND ACRONYMS........................................................................................................ 29 REFERENCE DOCUMENTS...................................................................................................... 36 1. INTRODUCTION ................................................................................................................ 37 1.1. A THIRD GENERATION I/O INTERCONNECT ................................................................... 37 1.2. PCI EXPRESS LINK......................................................................................................... 39 1.3. PCI EXPRESS FABRIC TOPOLOGY .................................................................................. 41 1.3.1. Root Complex........................................................................................................ 41 1.3.2. Endpoints .............................................................................................................. 42 1.3.3. Switch.................................................................................................................... 45 1.3.4. Root Complex Event Collector.............................................................................. 46 1.3.5. PCI Express to PCI/PCI-X Bridge........................................................................ 46 1.4. PCI EXPRESS FABRIC TOPOLOGY CONFIGURATION....................................................... 46 1.5. PCI EXPRESS LAYERING OVERVIEW.............................................................................. 47 1.5.1. Transaction Layer................................................................................................. 48 1.5.2. Data Link Layer .................................................................................................... 48 1.5.3. Physical Layer ...................................................................................................... 49 1.5.4. Layer Functions and Services............................................................................... 49 2. TRANSACTION LAYER SPECIFICATION ..................................................................... 53 2.1. TRANSACTION LAYER OVERVIEW.................................................................................. 53 2.1.1. Address Spaces, Transaction Types, and Usage................................................... 54 2.1.2. Packet Format Overview ...................................................................................... 56 2.2. TRANSACTION LAYER PROTOCOL - PACKET DEFINITION............................................... 58 2.2.1. Common Packet Header Fields ............................................................................ 58 2.2.2. TLPs with Data Payloads - Rules ......................................................................... 61 2.2.3. TLP Digest Rules .................................................................................................. 65 2.2.4. Routing and Addressing Rules .............................................................................. 65 2.2.5. First/Last DW Byte Enables Rules........................................................................ 69 2.2.6. Transaction Descriptor......................................................................................... 71 2.2.7. Memory, I/O, and Configuration Request Rules................................................... 77 2.2.8. Message Request Rules......................................................................................... 83 2.2.9. Completion Rules.................................................................................................. 97 2.2.10. TLP Prefix Rules ................................................................................................. 100 2.3. HANDLING OF RECEIVED TLPS.................................................................................... 104

PCIE规范详细文档

Traditional multi-drop, parallel bus technology is approaching its practical performance limits. It is clear that balancing system performance requires I/O bandwidth to scale with processing and application demands. There is an industry mandate to re-engineer I/O connectivity within cost constraints. PCI Express comprehends the many I/O requirements presented across the spectrum of computing and communications platforms, and rolls them into a common scalable and extensible I/O industry specification. Alongside these increasing performance demands, the enterprise server and communications markets have the need for improved reliability, security, and quality of service guarantees. This specification will therefore be applicable to multiple market segments. Technology advances in high-speed, point-to-point interconnects enable us to break away from the bandwidth limitations of multi-drop, parallel buses. The PCI Express basic physical layer consists of a differential transmit pair and a differential receive pair. Dual simplex data on these point-to-point connections is self-clocked and its bandwidth increases linearly with interconnect width and frequency. PCI Express takes an additional step of including a message space within its bus protocol that is used to implement legacy “side- band” signals. This further reduction of signal pins produces a very low pin count connection for components and adapters. The PCI Express Transaction, Data Link, and Physical Layers are optimized for chip-to-chip and board-to-board interconnect applications. An inherent limitation of today’s PCI-based platforms is the lack of support for isochronous data delivery, an attribute that is especially important to streaming media applications. To enable these emerging applications, PCI Express adds a virtual channel mechanism. In addition to use for support of isochronous traffic, the virtual channel mechanism provides an infrastructure for future extensions in supporting new applications. By adhering to the PCI Software Model, today’s applications are easily migrated even as emerging applications are enabled.

PCIe规范详细解析

PCIe规范介绍的文档,很详细。

PCIe规范各版本合集(1.0a、2.0、2.1、3.0、4.0、5.0)

PCIe规范各版本合集,包括1.0a、2.0、2.1、3.0、4.0、5.0四个版本,调试pcie必备资料,给大家分享一下。

PCIe规范各版本合集(1.0a、2.0、2.1、3.0)

PCIe规范各版本合集,包括1.0a、2.0、2.1、3.0四个版本,调试pcie必备资料,给大家分享一下。

PCIE 4.0规范(包括Base和CEM)

NCB-PCI_Express_Base_4.0r1.0_September-27-2017-c 和PCIe_CEM_SPEC_R4_V9_12072018_NCB

PCI协议中文版

PCI局部总线规范 2 文档约定 2 第1章 简介 3 规范的内容 3 规范的动机 3 PCI局部总线的应用 3 PCI局部总线的架构 4 PCI局部总线的特性和益处 5 第2章 信号定义 7 2.1 信号类型的定义 7 2.2 引脚功能分组 8 2.2.1 系统引脚 8 2.2.2 地址和数据引脚 8 2.2.3 接口控制引脚 9 2.2.4 仲裁引脚 10 2.2.5 错误报告引脚 10 2.2.6 中断引脚(可选的) 10 2.2.7 支持高速缓存的引脚(可选的) 12 2.2.8 额外的信号引脚 13 2.2.9 64位中线扩展引脚(可选的) 14 2.2.10 JTAG/边界扫描(Boundary Scan)引脚(可选的) 14 2.3 旁带信号(Sideband Signals) 15 2.4 中央资源的功能 15 第3章 总线操作 16 第6章 PCI配置空间 17 6.1概述 17 6.2配置空间的组织 17 6.3配置空间的功能 19 6.3.1 设备识别 19 6.3.2 设备控制与命令寄存器 20 6.3.3设备状态寄存器和设备状态 22 6.3.4 配置空间的其他域的功能 23 6.3.4.1 CacheLine Size 23 6.3.5 23

PCI总线标准协议(中文版).

pci-e学习的最好文档,介绍pci-e的各种时序描述

pcie接口协议学习资料

文档中包含pcie1.0,pcie2.0,pcie3.0英文原版资料,资料齐全,供需要tx学习

PCIE协议.zip

内涵PCIE1.0-5.0所有协议版本。PCI Express Base Specification Revision 1.0 April 29, 2002 PCI Express® Base Specification Revision 5.0 Version 1.0 22 May 2019

PCIE nvme协议

关于pcie的nvme协议的详细说明。包括物理层,应用层的说明与应用

PCI-E协议3.0

PCI-e 3.0 标准。希望对大家又用。

PCIE处理层协议(Transaction Layer Specifications)

处理层协议( transaction Layer specification transaction Layer specificationtransaction Layer specificationtransaction Layer specification transaction Layer specificationtransaction Layer specification transaction Layer specificationtransaction Layer specificationtransaction Layer specification transaction Layer specificationtransaction Layer specificationtransaction Layer specificationtransaction Layer specificationtransaction Layer specification transaction Layer specificationtransaction Layer specificationtransaction Layer specification transaction Layer specificationtransaction Layer specificationtransaction Layer specification transaction Layer specification) ◆TLPTLPTLP概况。 ◆寻址 定位和路由导向 定位和路由导向 定位和路由导向 定位和路由导向 。 ◆i/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message request i/o,memory,configuration,message request i/o,memory,configuration,message requesti/o,memory,configuration,message request i/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message request i/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message request i/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message request i/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message request i/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message requesti/o,memory,configuration,message request、completion completioncompletioncompletioncompletioncompletioncompletioncompletioncompletion详解。 详解。 ◆请求和 ◆请求和 响应 处理机制。 处理机制。 处理机制。 ◆virtual channel(vc)Mechanism虚拟通道机制。 ◆data integrity数据完整性。

PCIe 1.0协议规范

PCIe 1.0协议规范,对PCIe接口的电气特性、机械特性以及PCIe协议的各层都进行了详细的说明和描述

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

海量

VIP免费资源

千本

正版电子书

商城

会员专享价

千门

课程&专栏

全年可省5,000元

立即开通

全年可省5,000元

立即开通

最新推荐

Elasticsearch初识与简单案例.pdf

Elasticsearch是一个基于Lucene的分布式全文搜索引擎,提供灵活且高效的搜索和分析功能。通过HTTP请求和客户端库,用户可以索引和搜索文档,执行复杂查询,进行数据分析,并享受高亮显示等特性。其高级功能如复合查询、聚合分析、滚动搜索等,使其适用于各种数据处理和分析场景。Elasticsearch还具有强大的监控和日志功能,确保集群稳定运行。总之,Elasticsearch是企业级搜索和分析的理想选择。

RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

REALTEK 8188FTV 8188eus 8188etv linux驱动程序稳定版本, 支持AP,STA 以及AP+STA 共存模式。 稳定支持linux4.0以上内核。

管理建模和仿真的文件

管理Boualem Benatallah引用此版本:布阿利姆·贝纳塔拉。管理建模和仿真。约瑟夫-傅立叶大学-格勒诺布尔第一大学,1996年。法语。NNT:电话:00345357HAL ID:电话:00345357https://theses.hal.science/tel-003453572008年12月9日提交HAL是一个多学科的开放存取档案馆,用于存放和传播科学研究论文,无论它们是否被公开。论文可以来自法国或国外的教学和研究机构,也可以来自公共或私人研究中心。L’archive ouverte pluridisciplinaire

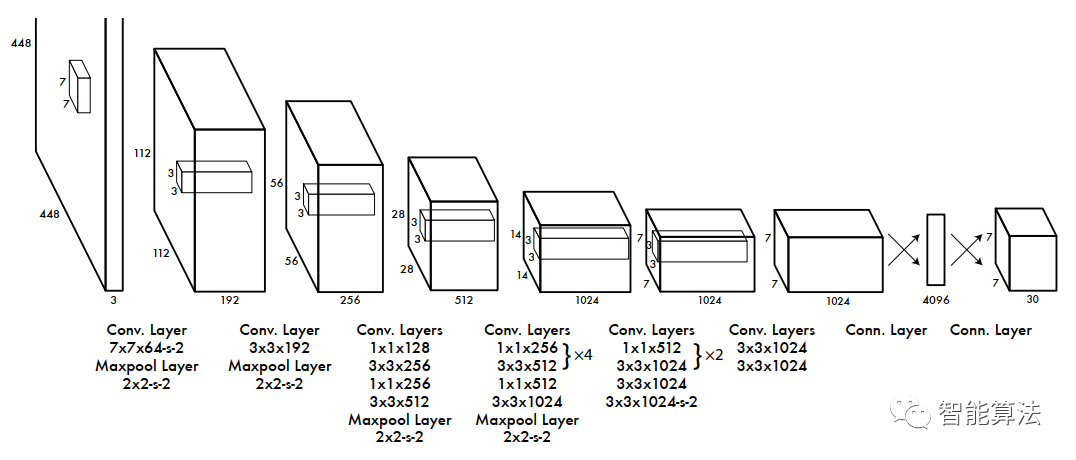

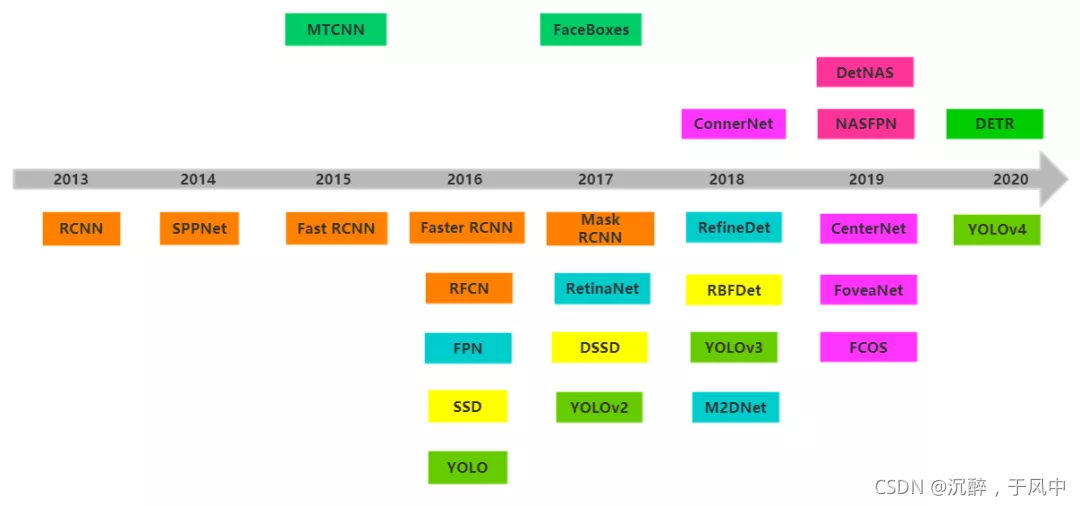

:YOLOv1目标检测算法:实时目标检测的先驱,开启计算机视觉新篇章

# 1. 目标检测算法概述 目标检测算法是一种计算机视觉技术,用于识别和定位图像或视频中的对象。它在各种应用中至关重要,例如自动驾驶、视频监控和医疗诊断。 目标检测算法通常分为两类:两阶段算法和单阶段算法。两阶段算法,如 R-CNN 和 Fast R-CNN,首先生成候选区域,然后对每个区域进行分类和边界框回归。单阶段算法,如 YOLO 和 SSD,一次性执行检

设计算法实现将单链表中数据逆置后输出。用C语言代码

如下所示: ```c #include <stdio.h> #include <stdlib.h> // 定义单链表节点结构体 struct node { int data; struct node *next; }; // 定义单链表逆置函数 struct node* reverse(struct node *head) { struct node *prev = NULL; struct node *curr = head; struct node *next; while (curr != NULL) { next

c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

校园超市商品信息管理系统课程设计旨在帮助学生深入理解程序设计的基础知识,同时锻炼他们的实际操作能力。通过设计和实现一个校园超市商品信息管理系统,学生掌握了如何利用计算机科学与技术知识解决实际问题的能力。在课程设计过程中,学生需要对超市商品和销售员的关系进行有效管理,使系统功能更全面、实用,从而提高用户体验和便利性。 学生在课程设计过程中展现了积极的学习态度和纪律,没有缺勤情况,演示过程流畅且作品具有很强的使用价值。设计报告完整详细,展现了对问题的深入思考和解决能力。在答辩环节中,学生能够自信地回答问题,展示出扎实的专业知识和逻辑思维能力。教师对学生的表现予以肯定,认为学生在课程设计中表现出色,值得称赞。 整个课程设计过程包括平时成绩、报告成绩和演示与答辩成绩三个部分,其中平时表现占比20%,报告成绩占比40%,演示与答辩成绩占比40%。通过这三个部分的综合评定,最终为学生总成绩提供参考。总评分以百分制计算,全面评估学生在课程设计中的各项表现,最终为学生提供综合评价和反馈意见。 通过校园超市商品信息管理系统课程设计,学生不仅提升了对程序设计基础知识的理解与应用能力,同时也增强了团队协作和沟通能力。这一过程旨在培养学生综合运用技术解决问题的能力,为其未来的专业发展打下坚实基础。学生在进行校园超市商品信息管理系统课程设计过程中,不仅获得了理论知识的提升,同时也锻炼了实践能力和创新思维,为其未来的职业发展奠定了坚实基础。 校园超市商品信息管理系统课程设计的目的在于促进学生对程序设计基础知识的深入理解与掌握,同时培养学生解决实际问题的能力。通过对系统功能和用户需求的全面考量,学生设计了一个实用、高效的校园超市商品信息管理系统,为用户提供了更便捷、更高效的管理和使用体验。 综上所述,校园超市商品信息管理系统课程设计是一项旨在提升学生综合能力和实践技能的重要教学活动。通过此次设计,学生不仅深化了对程序设计基础知识的理解,还培养了解决实际问题的能力和团队合作精神。这一过程将为学生未来的专业发展提供坚实基础,使其在实际工作中能够胜任更多挑战。

"互动学习:行动中的多样性与论文攻读经历"

多样性她- 事实上SCI NCES你的时间表ECOLEDO C Tora SC和NCESPOUR l’Ingén学习互动,互动学习以行动为中心的强化学习学会互动,互动学习,以行动为中心的强化学习计算机科学博士论文于2021年9月28日在Villeneuve d'Asq公开支持马修·瑟林评审团主席法布里斯·勒菲弗尔阿维尼翁大学教授论文指导奥利维尔·皮耶昆谷歌研究教授:智囊团论文联合主任菲利普·普雷教授,大学。里尔/CRISTAL/因里亚报告员奥利维耶·西格德索邦大学报告员卢多维奇·德诺耶教授,Facebook /索邦大学审查员越南圣迈IMT Atlantic高级讲师邀请弗洛里安·斯特鲁布博士,Deepmind对于那些及时看到自己错误的人...3谢谢你首先,我要感谢我的两位博士生导师Olivier和Philippe。奥利维尔,"站在巨人的肩膀上"这句话对你来说完全有意义了。从科学上讲,你知道在这篇论文的(许多)错误中,你是我可以依

:YOLO目标检测算法的挑战与机遇:数据质量、计算资源与算法优化,探索未来发展方向

# 1. YOLO目标检测算法简介 YOLO(You Only Look Once)是一种

在xlwings里.循环读取A列和B列的数据。当A列某单元格值等于特品,且同行B列单元格值等于热销品时。在同行的C列单元格输出值999。这代码怎么写

您好!感谢您对ChitGPT的使用! 为了回答您的问题,您可以使用xlwings的API和Excel公式配合完成以下任务: ``` import xlwings as xw wb = xw.Book('workbook.xlsx') # 打开工作簿 sht = wb.sheets['Sheet1'] # 打开工作表 # 遍历A列和B列数据 for i in range(1, sht.range('A' + str(sht.cells.last_cell.row)).end('up').row + 1): if sht.range(f'A{i}').value == '特品'

建筑供配电系统相关课件.pptx

建筑供配电系统是建筑中的重要组成部分,负责为建筑内的设备和设施提供电力支持。在建筑供配电系统相关课件中介绍了建筑供配电系统的基本知识,其中提到了电路的基本概念。电路是电流流经的路径,由电源、负载、开关、保护装置和导线等组成。在电路中,涉及到电流、电压、电功率和电阻等基本物理量。电流是单位时间内电路中产生或消耗的电能,而电功率则是电流在单位时间内的功率。另外,电路的工作状态包括开路状态、短路状态和额定工作状态,各种电气设备都有其额定值,在满足这些额定条件下,电路处于正常工作状态。而交流电则是实际电力网中使用的电力形式,按照正弦规律变化,即使在需要直流电的行业也多是通过交流电整流获得。 建筑供配电系统的设计和运行是建筑工程中一个至关重要的环节,其正确性和稳定性直接关系到建筑物内部设备的正常运行和电力安全。通过了解建筑供配电系统的基本知识,可以更好地理解和应用这些原理,从而提高建筑电力系统的效率和可靠性。在课件中介绍了电工基本知识,包括电路的基本概念、电路的基本物理量和电路的工作状态。这些知识不仅对电气工程师和建筑设计师有用,也对一般人了解电力系统和用电有所帮助。 值得一提的是,建筑供配电系统在建筑工程中的重要性不仅仅是提供电力支持,更是为了确保建筑物的安全性。在建筑供配电系统设计中必须考虑到保护装置的设置,以确保电路在发生故障时及时切断电源,避免潜在危险。此外,在电气设备的选型和布置时也需要根据建筑的特点和需求进行合理规划,以提高电力系统的稳定性和安全性。 在实际应用中,建筑供配电系统的设计和建设需要考虑多个方面的因素,如建筑物的类型、规模、用途、电力需求、安全标准等。通过合理的设计和施工,可以确保建筑供配电系统的正常运行和安全性。同时,在建筑供配电系统的维护和管理方面也需要重视,定期检查和维护电气设备,及时发现和解决问题,以确保建筑物内部设备的正常使用。 总的来说,建筑供配电系统是建筑工程中不可或缺的一部分,其重要性不言而喻。通过学习建筑供配电系统的相关知识,可以更好地理解和应用这些原理,提高建筑电力系统的效率和可靠性,确保建筑物内部设备的正常运行和电力安全。建筑供配电系统的设计、建设、维护和管理都需要严谨细致,只有这样才能确保建筑物的电力系统稳定、安全、高效地运行。