首页

用Verilog编写一个基于radix-2 booth算法设计一个乘法器

用Verilog编写一个基于radix-2 booth算法设计一个乘法器

时间: 2024-05-27 19:12:53

浏览: 201

对于您提出的问题,我可以回答。Radix-2 Booth算法乘法器通常是基于移位和加减运算的。它可以快速计算两个二进制数的乘积,而不需要进行除法运算。在Verilog中,可以定义输入的两个二进制数和输出的乘积,并利用移位和加法电路实现基于Radix-2 Booth算法的乘法器。具体实现细节需要进一步研究和设计。

阅读全文

相关推荐

采用booth算法的乘法器设计

别人写的论文 大家可以参考一下 还是挺不错的

基于booth算法的乘法器代码

基于booth算法的乘法器代码,清晰实用!可复用性强

用Verilog实现阵列乘法器

用Verilog实现阵列乘法器,采用的是流水线的做法

RTL.zip_booth_mac unit verilog_radix2

标题“RTL.zip_booth_mac_unit_verilog_radix2”表明这是一个使用Verilog语言编写的、采用Booth算法的二进制乘法器(乘加器单元)的RTL(Register Transfer Level)设计,其基础是基数2的表示方法。 首先,让我们...

FastMultiplier:使用 verilog 的快速乘法器实现

这个代表是一个modelsim 10.2c项目,该项目是一个快速乘法器电路的Verilog实现。 细节: 使用booth-radix 4算法生成部分乘积 使用基于 CSA 的 Wallace-tree-like 树来压缩部分乘积 进位超前加法器进行最终压缩。 ...

Verilog实现Booth算法的MAC单元设计

本节将详细介绍关于数字设计领域中一个重要的硬件结构——Booth RADIX-2乘累加器(MAC)单元在Verilog中的实现。本资源包内包含的RTL(Register Transfer Level)设计文件,通常用于硬件描述语言(HDL)形式的电子...

Verilog HDL实现:优化阵列乘法器与Booth编码乘法器的性能对比

"该文介绍了如何使用Verilog HDL语言实现阵列乘法器和Booth编码乘法器,特别地,文中提出了采用4-2和5-2混合压缩器来优化部分积处理,从而降低乘法器的延迟和资源消耗。通过在Xilinx ISE和Quartus II平台上进行仿真...

Verilog实现定点乘法器详解

"乘法器Verilog设计与实现"这个资源详细介绍了乘法器的Verilog实现过程,涵盖了从基本的位乘法到高级的优化算法,以及多种设计示例,是学习数字系统设计和Verilog编程的重要参考资料。通过学习这些内容,读者可以...

定点乘法器设计:蒋小龙乘法器实现详解

本文档主要介绍了蒋小龙设计的一种定点乘法器,重点探讨了乘法器设计的关键环节,包括编码、压缩和加法选择,并提供了多个设计示例,适用于Verilog语言实现。文档中提到了几种不同的算法和方法,以优化乘法器的性能...

定点乘法器文档

- 阵列乘法器使用并行结构,每个输入位对应一个乘法单元,同时进行多对位的乘法,然后将结果相加。这种实现方法适合于较大位宽的乘法,因为它可以在更短的时间内完成计算。 8. **乘加运算**: - 乘加运算结合了...

蒋小龙乘法器实现说明文档

定点乘法器的设计涉及多种算法,其中编码阶段提到了Booth编码,这是一种常用于减少乘法器中加法操作的算法,通过减少进位来提高效率。Booth算法分为标准形式和高基(High Radix)形式,高基形式在某些情况下可以...

Verilog快速乘法器实现:原理与压缩技术解析

快速乘法器的设计采用Booth-Radix 4算法生成部分乘积,然后通过基于 CSA(进位保存加法器)的Wallace树压缩结构来压缩部分乘积,最后使用进位超前加法器完成最终的压缩。Wallace树是用于实现并行乘法的一种结构,...

FPGA算术部件优化:高性能大数据算法研究

采用了改进的Booth算法来降低部分积的数量,同时利用5-2压缩器改进传统的4-2压缩树结构,以减小硬件资源的占用和提高运算速度。 再者,文章提到了FPGA除法器的改进设计。基于32位Radix-16 SRT除法器,每次循环能...

基于booth算法的乘法器的verilog实现

8位Booth乘法器设计,8位乘8位的基2的booth乘法器的verilog实现。满足1)利用硬件描述语言描述8位数乘法器运算;2)输入为复位信号、乘法执行按键;3)时钟信号为开发板上时钟信号。

Booth算法乘法器的Verilog代码实现(组合逻辑和流水线两种)

计算机组成原理中的Booth乘法器,相信大家都是非常熟悉的了。我在这里用了两种方法实现。 1.booth_com.v。首先把输入的两个操作数锁存一拍,然后用组合逻辑算出乘积,通过寄存器输出。 tbooth_com.v。booth_com的testbench。利用随机函数$random产生两个机数,然后将booth_com算出的结果与预期结果进行比较,并将比较的结果写入report_com文件。 2.booth_pipeline.v。用四级流水线实现的4位Booth算法乘法器。相信对大家理解流水线会有所帮助。 tbooth_pipeline.v。booth_pipeline的testbench。利用随机函数$random产生两个机数,然后将booth_pipeline算出的结果与预期结果进行比较,并将比较的结果写入report_pipeline文件。 两个源文件均在quartus5.0中实现。

乘法器的Verilog实现

包含有符号乘法器以及无符号乘法器的Verilog源码,同时带有tb文件用于仿真测试,在Vivado和Modelsim上验证通过

基于booth算法的乘法器的verilog HDL实现

基于booth算法的乘法器的verilog HDL实现。

booth算法的Verilog实现

booth算法的Verilog实现、压缩包中包含booth算法的Verilog实现与仿真的两个.v文件

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

海量

VIP免费资源

千本

正版电子书

商城

会员专享价

千门

课程&专栏

全年可省5,000元

立即开通

全年可省5,000元

立即开通

最新推荐

原码一位乘法器——组成原理课程设计

加法器模块是原码一位乘法器的最后一个部分,负责将中间结果相加,得到最终的乘法结果。加法器模块的设计需要考虑到数据的精度、运算速度和面积等多个因素。 在实现原码一位乘法器时,需要使用 FPGA 或 ASIC 等数字...

基于Verilog HDL的SVPWM算法的设计与仿真

总的来说,基于Verilog HDL的SVPWM算法设计与仿真涉及到电机控制理论、逆变器原理、硬件描述语言编程以及电力系统的实时控制等多个领域。这样的设计方法不仅可以提高控制精度,还能够灵活适应不同的应用需求,为现代...

基于Verilog HDL的一种绝对值编码器实时读出算法

《基于Verilog HDL的绝对值编码器实时读出算法》 在现代自动化系统中,光电编码器扮演着至关重要的角色,它能将机械位置转换为数字信号,为精确的定位和速度控制提供数据。本文章主要探讨了一种利用Verilog HDL语言...

DSP硬件实现的优化(一)—FPGA中复数乘法器的优化

通过减少一个乘法器的使用,可以节省宝贵的逻辑资源,提高系统的效率和性能。 对于使用Xilinx IP Core实现的复数乘法器,设计可能已经考虑了这样的优化,采用类似的方法。然而,在ASIC(Application-Specific ...

4位乘法器vhdl程序

4位乘法器是数字电路设计中的一个基本组件,它能将两个4位二进制数相乘,生成一个7位的结果。在VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)中,我们可以编写程序来描述这个逻辑功能...

JHU荣誉单变量微积分课程教案介绍

资源摘要信息:"jhu2017-18-honors-single-variable-calculus" 知识点一:荣誉单变量微积分课程介绍 本课程为JHU(约翰霍普金斯大学)的荣誉单变量微积分课程,主要针对在2018年秋季和2019年秋季两个学期开设。课程内容涵盖两个学期的微积分知识,包括整合和微分两大部分。该课程采用IBL(Inquiry-Based Learning)格式进行教学,即学生先自行解决问题,然后在学习过程中逐步掌握相关理论知识。 知识点二:IBL教学法 IBL教学法,即问题导向的学习方法,是一种以学生为中心的教学模式。在这种模式下,学生在教师的引导下,通过提出问题、解决问题来获取知识,从而培养学生的自主学习能力和问题解决能力。IBL教学法强调学生的主动参与和探索,教师的角色更多的是引导者和协助者。 知识点三:课程难度及学习方法 课程的第一次迭代主要包含问题,难度较大,学生需要有一定的数学基础和自学能力。第二次迭代则在第一次的基础上增加了更多的理论和解释,难度相对降低,更适合学生理解和学习。这种设计旨在帮助学生从实际问题出发,逐步深入理解微积分理论,提高学习效率。 知识点四:课程先决条件及学习建议 课程的先决条件为预演算,即在进入课程之前需要掌握一定的演算知识和技能。建议在使用这些笔记之前,先完成一些基础演算的入门课程,并进行一些数学证明的练习。这样可以更好地理解和掌握课程内容,提高学习效果。 知识点五:TeX格式文件 标签"TeX"意味着该课程的资料是以TeX格式保存和发布的。TeX是一种基于排版语言的格式,广泛应用于学术出版物的排版,特别是在数学、物理学和计算机科学领域。TeX格式的文件可以确保文档内容的准确性和排版的美观性,适合用于编写和分享复杂的科学和技术文档。

管理建模和仿真的文件

管理Boualem Benatallah引用此版本:布阿利姆·贝纳塔拉。管理建模和仿真。约瑟夫-傅立叶大学-格勒诺布尔第一大学,1996年。法语。NNT:电话:00345357HAL ID:电话:00345357https://theses.hal.science/tel-003453572008年12月9日提交HAL是一个多学科的开放存取档案馆,用于存放和传播科学研究论文,无论它们是否被公开。论文可以来自法国或国外的教学和研究机构,也可以来自公共或私人研究中心。L’archive ouverte pluridisciplinaire

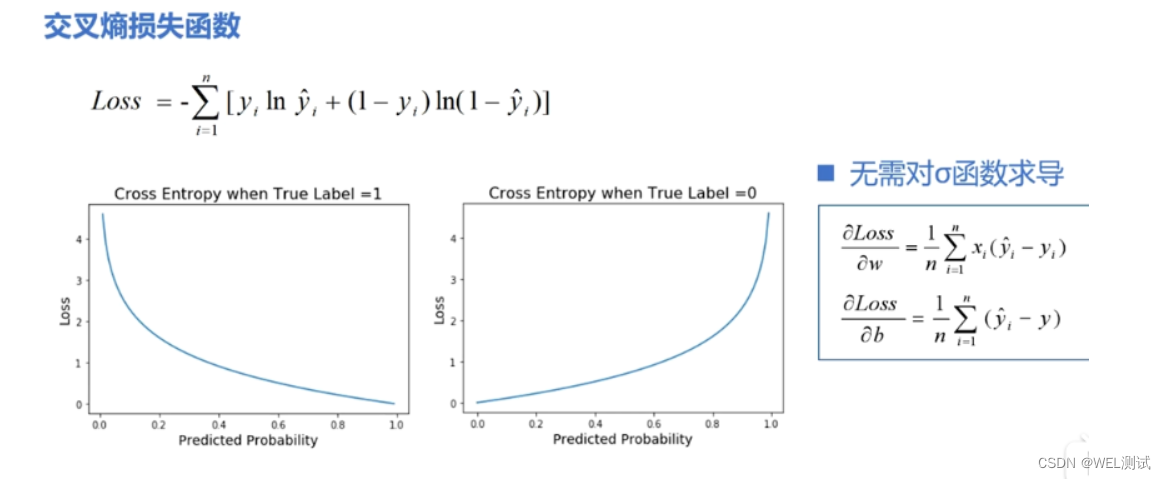

【实战篇:自定义损失函数】:构建独特损失函数解决特定问题,优化模型性能

# 1. 损失函数的基本概念与作用 ## 1.1 损失函数定义 损失函数是机器学习中的核心概念,用于衡量模型预测值与实际值之间的差异。它是优化算法调整模型参数以最小化的目标函数。 ```math L(y, f(x)) = \sum_{i=1}^{N} L_i(y_i, f(x_i)) ``` 其中,`L`表示损失函数,`y`为实际值,`f(x)`为模型预测值,`N`为样本数量,`L_i`为第`i`个样本的损失。 ## 1.2 损

如何在ZYNQMP平台上配置TUSB1210 USB接口芯片以实现Host模式,并确保与Linux内核的兼容性?

要在ZYNQMP平台上实现TUSB1210 USB接口芯片的Host模式功能,并确保与Linux内核的兼容性,首先需要在硬件层面完成TUSB1210与ZYNQMP芯片的正确连接,保证USB2.0和USB3.0之间的硬件电路设计符合ZYNQMP的要求。 参考资源链接:[ZYNQMP USB主机模式实现与测试(TUSB1210)](https://wenku.csdn.net/doc/6nneek7zxw?spm=1055.2569.3001.10343) 具体步骤包括: 1. 在Vivado中设计硬件电路,配置USB接口相关的Bank502和Bank505引脚,同时确保USB时钟的正确配置。

Naruto爱好者必备CLI测试应用

资源摘要信息:"Are-you-a-Naruto-Fan:CLI测验应用程序,用于检查Naruto狂热者的知识" 该应用程序是一个基于命令行界面(CLI)的测验工具,设计用于测试用户对日本动漫《火影忍者》(Naruto)的知识水平。《火影忍者》是由岸本齐史创作的一部广受欢迎的漫画系列,后被改编成同名电视动画,并衍生出一系列相关的产品和文化现象。该动漫讲述了主角漩涡鸣人从忍者学校开始的成长故事,直到成为木叶隐村的领袖,期间包含了忍者文化、战斗、忍术、友情和忍者世界的政治斗争等元素。 这个测验应用程序的开发主要使用了JavaScript语言。JavaScript是一种广泛应用于前端开发的编程语言,它允许网页具有交互性,同时也可以在服务器端运行(如Node.js环境)。在这个CLI应用程序中,JavaScript被用来处理用户的输入,生成问题,并根据用户的回答来评估其对《火影忍者》的知识水平。 开发这样的测验应用程序可能涉及到以下知识点和技术: 1. **命令行界面(CLI)开发:** CLI应用程序是指用户通过命令行或终端与之交互的软件。在Web开发中,Node.js提供了一个运行JavaScript的环境,使得开发者可以使用JavaScript语言来创建服务器端应用程序和工具,包括CLI应用程序。CLI应用程序通常涉及到使用诸如 commander.js 或 yargs 等库来解析命令行参数和选项。 2. **JavaScript基础:** 开发CLI应用程序需要对JavaScript语言有扎实的理解,包括数据类型、函数、对象、数组、事件循环、异步编程等。 3. **知识库构建:** 测验应用程序的核心是其问题库,它包含了与《火影忍者》相关的各种问题。开发人员需要设计和构建这个知识库,并确保问题的多样性和覆盖面。 4. **逻辑和流程控制:** 在应用程序中,需要编写逻辑来控制测验的流程,比如问题的随机出现、计时器、计分机制以及结束时的反馈。 5. **用户界面(UI)交互:** 尽管是CLI,用户界面仍然重要。开发者需要确保用户体验流畅,这包括清晰的问题呈现、简洁的指令和友好的输出格式。 6. **模块化和封装:** 开发过程中应当遵循模块化原则,将不同的功能分隔开来,以便于管理和维护。例如,可以将问题生成器、计分器和用户输入处理器等封装成独立的模块。 7. **单元测试和调试:** 测验应用程序在发布前需要经过严格的测试和调试。使用如Mocha或Jest这样的JavaScript测试框架可以编写单元测试,并通过控制台输出调试信息来排除故障。 8. **部署和分发:** 最后,开发完成的应用程序需要被打包和分发。如果是基于Node.js的应用程序,常见的做法是将其打包为可执行文件(如使用electron或pkg工具),以便在不同的操作系统上运行。 根据提供的文件信息,虽然具体细节有限,但可以推测该应用程序可能采用了上述技术点。用户通过点击提供的链接,可能将被引导到一个网页或直接下载CLI应用程序的可执行文件,从而开始进行《火影忍者》的知识测验。通过这个测验,用户不仅能享受答题的乐趣,还可以加深对《火影忍者》的理解和认识。