首页

lx2160a uart2

lx2160a uart2

时间: 2023-11-15 16:55:24

浏览: 66

lx2160a芯片是一款高性能的Arm架构处理器,其中UART2是其中一个串口接口。您可以通过以下步骤在lx2160a上使用UART2: 1. 确认UART2的引脚分配和电气特性。 2. 在设备树中启用UART2节点。 3. 在Linux内核中启用UART2驱动程序。 4. 在应用程序中打开并使用UART2。

阅读全文

相关推荐

Renasas RAA215300 Programing Special

该芯片具有丰富的 peripheral Interface,包括 UART、SPI、I2C、I2S 等,适合用于各种嵌入式系统和 IoT 应用。 二、RAA215300 芯片引脚配置 RAA215300 芯片具有 56 个引脚,每个引脚都有其特定的功能和描述,如表 ...

ESP-S2资料,ESP-S2硬件操作指南,ESP-S2技术参考手册,ESP-S2数据表

5. 丰富接口:内置USB、UART、SPI、I2C、PWM、DAC等接口,可接多种传感器和模块。 ESP32-S2是ESP32系列芯片中性价比较高的一个,它的主要特点是低功耗、价格低廉和高性能,非常适合于IoT应用的开发和插入式设备的...

XILINX XC6SLX16 Spartan6 FPGA开发板AD集成库(原理图库+PCB库).zip

CH340G USB2UART DB9 DC JW5060T_6 DC降压芯片 EA3059 FPC-40 FPC-40P-0.5mm FU 贴片保险丝 HDMI_A HEAD2 HR911130C RJ45 + MAG HS0038 Header 20X2 Header, 20-Pin, Dual row Header 2X2 Header, 2-Pin, Dual ...

ESP32-S2-SOLO模组技术规格与使用指南

ESP32-S2-SOLO和ESP32-S2-SOLO-U拥有丰富的外设接口,包括GPIO、SPI、UART、I2C、I2S、LCD接口、Camera接口、IR、脉冲计数器、LED PWM、TWAI(符合ISO11898-1标准,适用于车载通信)、USB 1.1、ADC、DAC、触摸传感器...

ESP32-S2芯片详情:智能家居与物联网的关键技术

5. 丰富接口:ESP32-S2内置了USB、UART、SPI、I2C、PWM、DAC等多种接口,可以接多种传感器和模块,这使得它在各种物联网设备中的应用变得非常灵活。 ESP32-S2的技术参考手册和数据表详细介绍了ESP32-S2的硬件特性和...

【网络芯片架构揭秘】:深入理解LAN8720A_LAN8720AI的架构与特点

[【网络芯片架构揭秘】:深入理解LAN8720A_LAN8720AI的架构与特点](https://img-blog.csdnimg.cn/20210628151914743.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9...

复古怀旧教室桌椅素材同学聚会毕业纪念册模板.pptx

复古怀旧教室桌椅素材同学聚会毕业纪念册模板

数据结构与算法中的回文串:马拉车算法与中心扩展法的Python实现及其应用

内容概要:本文详细介绍了关于寻找最长回文子串的相关知识,包括前置理论、不同求解方法的具体操作及其优势。首先,阐述了回文串这一特殊结构的概念及其特性——正序逆序完全一致。紧接着,围绕中心扩展法和马拉车算法展开叙述。前者基于字符逐一检查周边字符的方法,在每一点向外延伸探索最长相同序列。而后者利用预处理阶段将字符间隔用特殊符号填充形成全新字符串形式,并建立相应的辅助工具(如回文半径数组)用于跟踪回文中点位置与范围变动情况,再经由巧妙规则判定并逐步推进搜索进度,从而大大降低了运行成本。最后还提到了两种常规方法——动态规划与中心扩展的具体思路以及它们各自适用的情况和局限性。 适合人群:正在研究或学习数据结构和算法特别是字符串处理相关领域的技术人员和爱好者。 使用场景及目标:帮助开发者针对字符串匹配类的问题,尤其是回文判定和查找场景,掌握更多高效的解决方案,优化程序性能。具体应用场景如文本编辑器、搜索引擎中的关键字检索等方面可能会涉及到这类算法的应用。

前端分析-2023071100789

前端分析-2023071100789

国货彩妆品牌Q1社媒营销投放分析报告.pdf

国货彩妆品牌Q1社媒营销投放分析报告

内螺旋覆盖算法(ISC)matlab代码

内螺旋覆盖算法(ISC)是一种用于填充正方形矩阵的算法。它的主要思想是按照一定的规则将矩阵从外部向内部进行覆盖,直到矩阵的中心被填充。在覆盖的环境区域内,机器人按一定的方向如顺时针或逆时针进行覆盖,当前方有未覆盖的栅格时机器人就向前运动,如果前方有障碍物或者已经被覆盖过,则机器要向右(或向左)旋转 90 °继续向前行走。

21电平MMC整流站、MMC逆变站、两端柔性互联的MATLAB仿真模型,4端柔性互联、MMC桥臂平均值模型、MMC聚合模型(四端21电平一分钟即能完成2s的工况仿真) 1-全部能正常运行,图四和图五为

21电平MMC整流站、MMC逆变站、两端柔性互联的MATLAB仿真模型,4端柔性互联、MMC桥臂平均值模型、MMC聚合模型(四端21电平一分钟即能完成2s的工况仿真) 1-全部能正常运行,图四和图五为仿真波形 2-双闭环控制,逆变站PQ控制,整流站站Udc Q控制 3-最近电平逼近调制+子模块电容充电 4-环流抑制控制

永磁同步电机电流滞环控制Matlab simulink仿真模型,参数已设置好,可直接运行 属于PMSM转速电流双闭环矢量控制系统模型 电流内环采用电流滞环控制(pang-pang控制),转速外环为

永磁同步电机电流滞环控制Matlab simulink仿真模型,参数已设置好,可直接运行。 属于PMSM转速电流双闭环矢量控制系统模型。 电流内环采用电流滞环控制(pang-pang控制),转速外环为PI控制。 波形完美,包含原理说明文档和参考文献。

基于java的项目申报管理系统设计与实现.docx

基于java的项目申报管理系统设计与实现.docx

CSDN会员

开通CSDN年卡参与万元壕礼抽奖

海量

VIP免费资源

千本

正版电子书

商城

会员专享价

千门

课程&专栏

全年可省5,000元

立即开通

全年可省5,000元

立即开通

大家在看

SigmaStudioHelp_3.0(中文)

关于DSP 的技术文档,留住入门DSP 控制用作备份;DSP核心技术都在里面了解;

C#线上考试系统源码.zip

C#线上考试系统源码.zip

VITA 62.0.docx

VPX62 电源标准中文

公安大数据零信任体系设计要求.pdf

公安大数据零信任体系设计要求,本规范性技术文件规定了零信任体系的整体设计原则、设计目标、总体架构、整体能力要求和安全流程。用以指导公安大数据智能化访问控制体系的规划、设计、建设、实施、应用、运营等工作。 本规范性技术文件适用于参与公安机关大数据智能化访问控制体系建设工作的各级公安机关、相关单位、以及各类技术厂商等单位及其人员。

AUTOSAR-MCAL -CanDriver-UserMAnnual

EB Tresos,CAN驱动用户手册,有助于进行CAN模块配置及配置项研究

最新推荐

xilinx,zynq uart16550开发手册

《Xilinx Zynq UART16550开发手册》是针对Xilinx Zynq系列FPGA中的UART16550高速串口进行详细解释和技术指导的文档。该手册涵盖了从基本概念到具体实现的全方位知识,适用于FPGA开发、ARM微处理器以及嵌入式硬件设计...

I2C,SPI,UART和CAN等常见通信协议的区别

总结来说,I2C、SPI、UART 和 CAN 各有特点和适用场景。I2C 适合短距离、低速、多设备通信,SPI 适合高速、全双工通信,UART 适用于长距离、异步通信,而 CAN 更适应高可靠性和实时性要求的环境。选择哪种通信协议取...

基于Lua脚本语言的嵌入式UART通信的实现

它的4个通道可分别独立编程,在3.3 V的操作电压下,数据传输速率可高达2 Mbps,适合多种UART通信环境中的应用。 Lua在嵌入式应用领域中的应用比较成熟,主要体现在以下几个方面:Lua与C交互环境的建立、提取脚本中...

verilog实现的UART(带中断、奇偶校验、帧错误)

本篇讨论的是如何使用Verilog实现一个带有中断、奇偶校验和帧错误检测功能的通用异步收发传输器(UART)。 UART是一种串行通信接口,常用于计算机和其他设备之间的通信,它通过串行传输数据,但数据接收和发送是...

A7600C1硬件设计手册规格书

在硬件设计上,A7600C1-MNSE提供了丰富的接口选项,如UART(通用异步收发传输器)、SDIO(Secure Digital Input/Output)、I2C(Inter-Integrated Circuit)和GPIO(General Purpose Input/Output)。这些接口的集成...

HTML挑战:30天技术学习之旅

资源摘要信息: "desafio-30dias" 标题 "desafio-30dias" 暗示这可能是一个与挑战或训练相关的项目,这在编程和学习新技能的上下文中相当常见。标题中的数字“30”很可能表明这个挑战涉及为期30天的时间框架。此外,由于标题是西班牙语,我们可以推测这个项目可能起源于或至少是针对西班牙语使用者的社区。标题本身没有透露技术上的具体内容,但挑战通常涉及一系列任务,旨在提升个人的某项技能或知识水平。 描述 "desafio-30dias" 并没有提供进一步的信息,它重复了标题的内容。因此,我们不能从中获得关于项目具体细节的额外信息。描述通常用于详细说明项目的性质、目标和期望成果,但由于这里没有具体描述,我们只能依靠标题和相关标签进行推测。 标签 "HTML" 表明这个挑战很可能与HTML(超文本标记语言)有关。HTML是构成网页和网页应用基础的标记语言,用于创建和定义内容的结构、格式和语义。由于标签指定了HTML,我们可以合理假设这个30天挑战的目的是学习或提升HTML技能。它可能包含创建网页、实现网页设计、理解HTML5的新特性等方面的任务。 压缩包子文件的文件名称列表 "desafio-30dias-master" 指向了一个可能包含挑战相关材料的压缩文件。文件名中的“master”表明这可能是一个主文件或包含最终版本材料的文件夹。通常,在版本控制系统如Git中,“master”分支代表项目的主分支,用于存放项目的稳定版本。考虑到这个文件名称的格式,它可能是一个包含所有相关文件和资源的ZIP或RAR压缩文件。 结合这些信息,我们可以推测,这个30天挑战可能涉及了一系列的编程任务和练习,旨在通过实践项目来提高对HTML的理解和应用能力。这些任务可能包括设计和开发静态和动态网页,学习如何使用HTML5增强网页的功能和用户体验,以及如何将HTML与CSS(层叠样式表)和JavaScript等其他技术结合,制作出丰富的交互式网站。 综上所述,这个项目可能是一个为期30天的HTML学习计划,设计给希望提升前端开发能力的开发者,尤其是那些对HTML基础和最新标准感兴趣的人。挑战可能包含了理论学习和实践练习,鼓励参与者通过构建实际项目来学习和巩固知识点。通过这样的学习过程,参与者可以提高在现代网页开发环境中的竞争力,为创建更加复杂和引人入胜的网页打下坚实的基础。

【CodeBlocks精通指南】:一步到位安装wxWidgets库(新手必备)

# 摘要 本文旨在为使用CodeBlocks和wxWidgets库的开发者提供详细的安装、配置、实践操作指南和性能优化建议。文章首先介绍了CodeBlocks和wxWidgets库的基本概念和安装流程,然后深入探讨了CodeBlocks的高级功能定制和wxWidgets的架构特性。随后,通过实践操作章节,指导读者如何创建和运行一个wxWidgets项目,包括界面设计、事件

andorid studio 配置ERROR: Cause: unable to find valid certification path to requested target

### 解决 Android Studio SSL 证书验证问题 当遇到 `unable to find valid certification path` 错误时,这通常意味着 Java 运行环境无法识别服务器提供的 SSL 证书。解决方案涉及更新本地的信任库或调整项目中的网络请求设置。 #### 方法一:安装自定义 CA 证书到 JDK 中 对于企业内部使用的私有 CA 颁发的证书,可以将其导入至 JRE 的信任库中: 1. 获取 `.crt` 或者 `.cer` 文件形式的企业根证书; 2. 使用命令行工具 keytool 将其加入 cacerts 文件内: ```

VC++实现文件顺序读写操作的技巧与实践

资源摘要信息:"vc++文件的顺序读写操作" 在计算机编程中,文件的顺序读写操作是最基础的操作之一,尤其在使用C++语言进行开发时,了解和掌握文件的顺序读写操作是十分重要的。在Microsoft的Visual C++(简称VC++)开发环境中,可以通过标准库中的文件操作函数来实现顺序读写功能。 ### 文件顺序读写基础 顺序读写指的是从文件的开始处逐个读取或写入数据,直到文件结束。这与随机读写不同,后者可以任意位置读取或写入数据。顺序读写操作通常用于处理日志文件、文本文件等不需要频繁随机访问的文件。 ### VC++中的文件流类 在VC++中,顺序读写操作主要使用的是C++标准库中的fstream类,包括ifstream(用于从文件中读取数据)和ofstream(用于向文件写入数据)两个类。这两个类都是从fstream类继承而来,提供了基本的文件操作功能。 ### 实现文件顺序读写操作的步骤 1. **包含必要的头文件**:要进行文件操作,首先需要包含fstream头文件。 ```cpp #include <fstream> ``` 2. **创建文件流对象**:创建ifstream或ofstream对象,用于打开文件。 ```cpp ifstream inFile("example.txt"); // 用于读操作 ofstream outFile("example.txt"); // 用于写操作 ``` 3. **打开文件**:使用文件流对象的成员函数open()来打开文件。如果不需要在创建对象时指定文件路径,也可以在对象创建后调用open()。 ```cpp inFile.open("example.txt", std::ios::in); // 以读模式打开 outFile.open("example.txt", std::ios::out); // 以写模式打开 ``` 4. **读写数据**:使用文件流对象的成员函数进行数据的读取或写入。对于读操作,可以使用 >> 运算符、get()、read()等方法;对于写操作,可以使用 << 运算符、write()等方法。 ```cpp // 读取操作示例 char c; while (inFile >> c) { // 处理读取的数据c } // 写入操作示例 const char *text = "Hello, World!"; outFile << text; ``` 5. **关闭文件**:操作完成后,应关闭文件,释放资源。 ```cpp inFile.close(); outFile.close(); ``` ### 文件顺序读写的注意事项 - 在进行文件读写之前,需要确保文件确实存在,且程序有足够的权限对文件进行读写操作。 - 使用文件流进行读写时,应注意文件流的错误状态。例如,在读取完文件后,应检查文件流是否到达文件末尾(failbit)。 - 在写入文件时,如果目标文件不存在,某些open()操作会自动创建文件。如果文件已存在,open()操作则会清空原文件内容,除非使用了追加模式(std::ios::app)。 - 对于大文件的读写,应考虑内存使用情况,避免一次性读取过多数据导致内存溢出。 - 在程序结束前,应该关闭所有打开的文件流。虽然文件流对象的析构函数会自动关闭文件,但显式调用close()是一个好习惯。 ### 常用的文件操作函数 - `open()`:打开文件。 - `close()`:关闭文件。 - `read()`:从文件读取数据到缓冲区。 - `write()`:向文件写入数据。 - `tellg()` 和 `tellp()`:分别返回当前读取位置和写入位置。 - `seekg()` 和 `seekp()`:设置文件流的位置。 ### 总结 在VC++中实现顺序读写操作,是进行文件处理和数据持久化的基础。通过使用C++的标准库中的fstream类,我们可以方便地进行文件读写操作。掌握文件顺序读写不仅可以帮助我们在实际开发中处理数据文件,还可以加深我们对C++语言和文件I/O操作的理解。需要注意的是,在进行文件操作时,合理管理和异常处理是非常重要的,这有助于确保程序的健壮性和数据的安全。

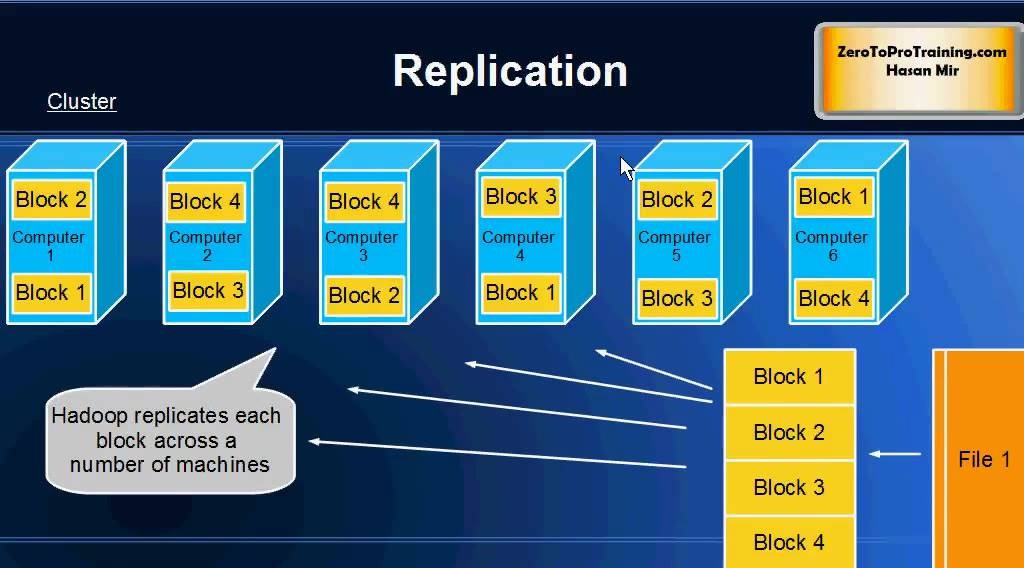

【大数据时代必备:Hadoop框架深度解析】:掌握核心组件,开启数据科学之旅

# 摘要 Hadoop作为一个开源的分布式存储和计算框架,在大数据处理领域发挥着举足轻重的作用。本文首先对Hadoop进行了概述,并介绍了其生态系统中的核心组件。深入分