【Arm®v8-M微控制器编程】:最佳实践与案例分析

发布时间: 2025-01-03 05:58:51 阅读量: 8 订阅数: 9

pyOCD:用于编程和调试Arm Cortex-M微控制器的开源Python库

# 摘要

本文全面介绍了Arm®v8-M微控制器架构的核心特性,包括其编程模型、内存保护机制、异常处理流程和硬件抽象层(HAL)。通过深入探讨Arm®v8-M寄存器结构及状态、内存保护单元(MPU)、异常处理、以及CMSIS标准,为开发者提供了系统级编程的详细指导。同时,本文还提供了关于如何选择和配置开发工具和环境的深入见解,并分享了高效的C/C++编程技巧、确保系统安全性和可靠性的方法,以及软件架构和模块化设计的最佳实践。最后,通过多个应用实例,如实时操作系统(RTOS)、物联网(IoT)设备开发以及高级驱动开发,本文展示了Arm®v8-M微控制器的实际应用,旨在帮助读者更好地理解和掌握相关技术。

# 关键字

Arm®v8-M微控制器;编程模型;内存保护单元;异常处理;HAL;软件架构;实时操作系统;物联网开发;驱动开发;C/C++编程

参考资源链接:[ARMv8-M架构参考手册](https://wenku.csdn.net/doc/646b4795543f844488c9e690?spm=1055.2635.3001.10343)

# 1. Arm®v8-M微控制器架构概述

## 1.1 Arm®v8-M架构简介

Arm®v8-M是Arm公司推出的面向微控制器领域的下一代架构,它继承了传统的Arm架构低功耗、高效能的特点,并引入了更多安全和实时性增强功能,为物联网(IoT)、汽车电子、智能家居等应用提供了更为强大的处理能力。

## 1.2 架构特点与优势

v8-M架构新增了多级访问权限控制和硬件级别的内存保护单元(MPU),在确保系统安全的同时提升了实时性能。通过引入TrustZone®技术,v8-M能够更有效地隔离安全和非安全世界,增强了系统的安全防护能力。同时,它还保留了与先前版本的兼容性,方便开发者进行软件迁移和升级。

## 1.3 应用领域与前景

v8-M架构主要针对要求高实时性、安全性和能效的应用领域,如智能传感器、无线通信模块以及各类工业控制设备。随着技术的进步和物联网的快速发展,v8-M架构的应用场景将会不断拓宽,市场需求持续增长。

# 2. 深入理解Arm®v8-M编程模型

### 2.1 Arm®v8-M寄存器和状态

#### 2.1.1 寄存器结构和用途

Arm®v8-M架构继承了先前版本的许多特征,并引入了新的寄存器以支持更高级别的安全特性和性能优化。在编程模型中,寄存器是处理器中用于存储数据和指令地址的硬件单元,它们在执行指令和处理数据流中扮演着核心角色。

- **通用寄存器**:包括R0至R12,用于一般的算术逻辑运算和数据存储。R0至R7寄存器是通用的,这意味着它们在函数调用中可以无限制地使用。而R8至R12虽然也是通用寄存器,但在某些架构特定的操作中可能有特殊用途。

- **链接寄存器(LR,R14)**:用于存储子程序返回地址。当调用一个子程序时,当前程序的返回地址会保存到LR中,这样子程序执行完毕后可以通过LR返回到正确的地址继续执行。

- **程序计数器(PC,R15)**:指向当前执行的指令。它在每次指令执行后自动增加,指向下一条将要执行的指令。在分支和跳转指令中,程序计数器可以被直接修改以改变执行流程。

- **状态寄存器**:包括应用状态程序计数器(APC,R16)和进程状态寄存器(APSR),APSR包含了进位/借位标志(C)、零标志(Z)、符号标志(N)和溢出标志(V)。这些标志位对于条件执行和分支决策至关重要。

在开发过程中,合理地使用和管理这些寄存器是至关重要的。例如,使用R0至R3传递参数给子程序,在函数中临时存储中间结果,或使用LR来实现函数间的正确跳转和返回。

#### 2.1.2 特权和非特权模式状态

Arm®v8-M架构定义了两种处理器执行状态:特权状态和非特权状态。不同的状态对应不同的权限和访问能力,这主要是为了实现安全的系统设计。

- **特权模式**:在这种模式下,软件可以访问所有的处理器资源和执行所有指令。一般情况下,操作系统内核和设备驱动程序运行在特权模式,它们可以执行敏感操作,如配置外设、管理内存映射等。

- **非特权模式**:在这种模式下,软件的访问受到限制,它不能执行一些可能会影响系统稳定性的操作。通常情况下,运行在非特权模式的应用程序不能直接操作硬件或修改某些关键的系统设置。

Arm®v8-M架构通过状态切换机制支持异常处理和中断服务。当异常发生时,处理器会自动切换到特权模式,并跳转到相应的异常处理程序执行。异常返回后,处理器再切换回先前的状态。

切换模式通常涉及到改变控制寄存器中的状态位,并且在某些情况下,还会涉及到切换栈指针(SP)。例如,在进入异常处理时,处理器会自动切换到主栈指针(MSP),而在退出异常时,可能会切换回进程栈指针(PSP)。

```

// 示例代码:切换栈指针到MSP

MRS R0, MSP // 将主栈指针的当前值读入R0寄存器

MSR PSP, R0 // 将R0的值写入进程栈指针

MSR MSP, R0 // 将R0的值恢复到主栈指针,保持MSP不变

```

上述操作保证了在异常处理程序中,能够使用正确的栈来保存和恢复上下文信息,而不会影响到正常的程序流程。

### 2.2 内存保护和异常处理

#### 2.2.1 内存保护单元(MPU)的工作机制

内存保护单元(MPU)是Arm®v8-M架构中用以实现内存访问控制的重要硬件组件。MPU可以定义内存区域的访问权限,并对访问违规进行限制,从而保障系统的安全性和稳定性。

- **内存区域定义**:MPU允许定义最多8个内存区域(对于某些配置可能有更多限制),每个区域可以单独配置为不同的访问权限,如只读、只执行或可读写等。

- **权限违规处理**:如果处理器尝试访问被MPU定义为不允许的内存区域,将会触发一个内存保护违规异常(MemManage异常),该异常可以由软件进行处理,如终止违规的程序或进行其他的安全操作。

- **区域属性设置**:在软件中,可以通过设置MPU的寄存器来定义这些内存区域。包括区域的起始地址、大小、类型、访问权限等。

```

// 示例代码:MPU内存区域设置

MPU_TYPE R0, #0x40000010 // 设置MPU类型寄存器,启用MPU功能

MPU_CTRL R0, #0 // 清除所有MPU区域的使能位

MPU_RBAR R1, #0, #0x0000 // 区域0的基地址设置为0x00000000

MPU_RASR R1, #0x100, #0x1 // 区域大小设置为1MB,访问权限设置为可读写

MPU_RBAR R2, #1, #0x8000 // 区域1的基地址设置为0x80000000

MPU_RASR R2, #0x100, #0x2 // 区域大小设置为1MB,访问权限设置为只读

```

通过以上代码,MPU被配置为有两个区域:0到1MB的内存可读写,8到9MB的内存仅可读。

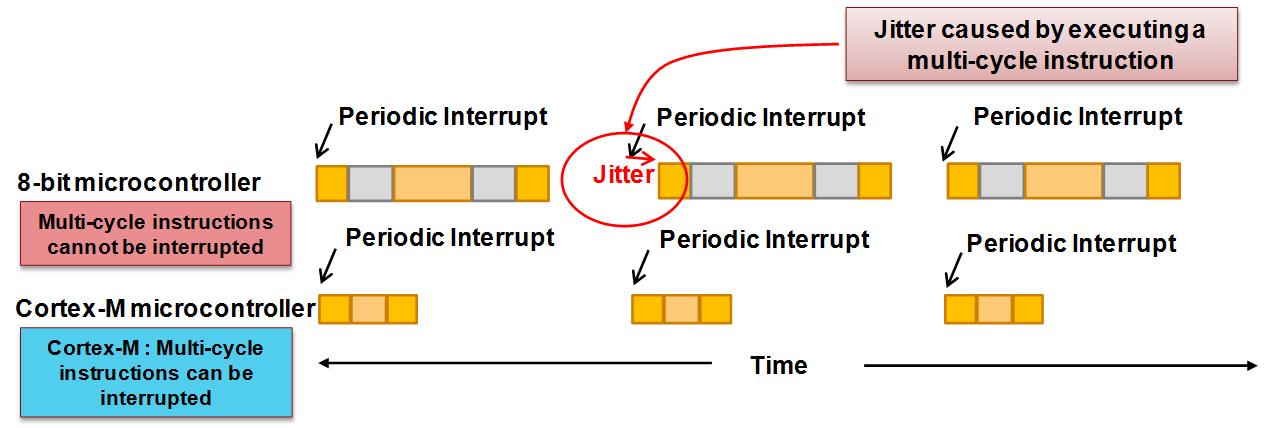

#### 2.2.2 异常和中断处理流程

异常和中断处理是任何实时操作系统或复杂应用程序的核心组成部分,它允许系统响应并处理内部或外部事件。

- **异常和中断分类**:异常可以分为同步异常(如指令错误、系统调用)和异步异常(如外部中断)。中断是指由外部事件(如硬件事件)引发的处理过程。

- **异常处理流程**:当异常发生时,处理器会自动执行以下步骤:

1. 保存当前程序状态到异常栈中。

2. 更新程序计数器(PC)到异常向量表中的相应地址。

3. 进入对应的异常处理程序执行。

4. 异常处理完成后,通过异常返回指令(如`BX LR`)回到被中断的程序流程。

```

// 示例代码:异常处理例程

Exception_Handler:

PUSH {R0-R3, LR} // 保存寄存器状态到栈中

// 处理异常的代码...

POP {R0-R3, PC} // 恢复寄存器状态并返回

```

异常处理程序需要快速且准确地处理异常情况,以最小化对正常运行程序的影响。

### 2.3 硬件抽象层(HAL)和固件标准

#### 2.3.1 HAL与系统级编程

硬件抽象层(HAL)是介于硬件和上层软件之间的一层抽象,其目的是提供一个简洁、一致的接口给系统级程序员使用。HAL屏蔽了硬件的复杂性,使得软件开发人员可以专注于业务逻辑的实现。

- **硬件访问抽象**:HAL提供了一系列标准化的接口来访问硬件资源,如GPIO、ADC、PWM等。开发者通过这些接口访问硬件,而不需要直接与硬件寄存器打交道。

- **平台无关性**:HAL层的设计考虑到了平台的无关性,即相同的HAL代码可以在不同的硬件平台(有相应支持的HAL实现)上运行而无需修改。

```

// 示例代码:GPIO访问的HAL函数

HAL_GPIO_Write

```

0

0