【系统稳定性提升之道】:多核心CPU下MT41J256M16 DDR3的表现分析

发布时间: 2024-11-29 13:24:54 阅读量: 15 订阅数: 35

Simulink仿真:基于扰动观察法的光伏MPPT改进算法 参考文献:基于扰动观察法的光伏MPPT改进算法+录制视频讲解 仿真平台:MATLAB Simulink 关键词:光伏;MPPT;扰动观察法

参考资源链接:[镁光MT41J256M16型DDR3数据手册详解](https://wenku.csdn.net/doc/6412b498be7fbd1778d40219?spm=1055.2635.3001.10343)

# 1. 多核心CPU与内存技术概述

在现代计算系统中,多核心CPU(中央处理单元)与内存技术是构建高性能计算环境的基石。随着技术的进步,CPU的核心数量不断增加,相应地,内存技术也经历了从DDR到DDR4的演变,如今DDR5技术也已经在研发中。这些技术的演进旨在提高数据处理速度,降低延迟,并为多线程应用提供更好的支持。本章将概述多核心CPU的基本概念,探讨内存技术的基础知识,并理解它们如何协同工作以实现更高效的计算。

## 1.1 多核心CPU的基本概念

多核心CPU是指在同一块硅片上集成了两个或更多的独立处理单元(核心),每个核心可以独立地处理任务。这种设计不仅提高了CPU的运算能力,也支持了更高效的并发处理,使得计算机系统能够同时运行多个程序或处理多线程任务。多核心架构的引入,是应对软件多线程化需求,以及提升并发处理性能的直接结果。

## 1.2 内存技术的基础知识

内存是计算机的主要存储组件之一,它用于暂存CPU正在处理的数据和指令。随着CPU核心数量的增加,对内存的要求也更加严苛。为了匹配多核心CPU的高性能要求,内存技术从DDR3逐步发展到DDR4,并且DDR5的研发也已经提上日程。内存速度的提升、时序的优化和能耗的降低,都是内存技术发展的重要方向。

为了更好地理解多核心CPU与内存之间的关系,我们将在接下来的章节中深入分析它们的技术细节和性能影响。

# 2. 多核心CPU架构下的性能分析

随着信息技术的不断进步,多核心CPU架构已经在现代计算机系统中占据了主导地位。这种架构通过集成多个处理核心在一个芯片上,极大地提高了计算性能并改进了能效。理解多核心CPU架构及其性能分析,对于IT行业专业人员来说,是提升系统效率和优化计算资源不可或缺的技能。本章节将深入探讨多核心CPU的工作原理、核心间通信机制,以及内存技术如何与多核心CPU协同工作,并介绍性能测试的方法论。

## 2.1 CPU核心技术简介

### 2.1.1 多核心CPU的工作原理

多核心CPU由两个或多个独立的处理器核心组成,它们可以共享内存控制器、缓存和I/O接口。这种设计让每个核心可以独立执行任务,或者协同处理复杂的计算任务,从而显著提升了处理多线程应用的能力。

核心内部的指令执行是基于经典的冯·诺依曼架构,涉及指令的提取、解码、执行和写回四个阶段。多核心的并行处理能力是在核心间通信和同步的基础上实现的,而多线程则是通过操作系统调度,将线程合理分配给不同的核心。

### 2.1.2 核心间通信机制

多核心CPU架构中的核心间通信对整体性能有着重要影响。核心间通信主要通过内部互连技术实现,例如,Intel的QuickPath Interconnect (QPI) 或 AMD的HyperTransport。这些互连技术提供了高速的数据传输通道,允许核心之间的数据快速交换。

此外,缓存一致性也是多核心通信中不可忽视的一部分。为了维持一致性,CPU使用诸如MESI(修改、独占、共享、无效)协议等缓存一致性协议。这些协议确保了数据在多个核心的缓存间的一致性,避免了数据冗余和不一致的问题。

## 2.2 DDR3内存技术解析

### 2.2.1 DDR3内存的工作原理

DDR3(Double Data Rate 3 SDRAM)是一种广泛应用于现代计算机系统的随机存取存储器(RAM)。它是一种同步动态随机存取存储器,能够在每个时钟周期的上升沿和下降沿传输数据,因此它的数据传输速率是标准SDRAM的两倍。

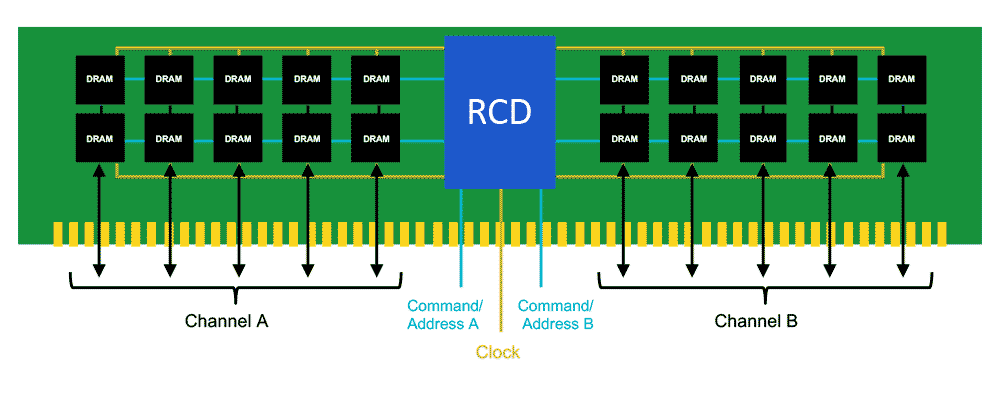

DDR3模块通过内存控制器与CPU进行通信,内存控制器负责管理内存地址、数据和控制信号的路由。当CPU请求数据时,内存控制器将地址信号传递给内存模块,并在需要时控制读写操作。

### 2.2.2 DDR3与多核心CPU的协同工作

为了充分利用多核心CPU的并行计算能力,内存必须能够快速响应核心的请求。DDR3通过提高数据传输速率和引入数据预取技术,支持更高效的并行数据访问。这意味着多核心CPU的每个核心都可以在较短的时间内获得所需的内存数据,从而减少等待时间,提高整体性能。

当多个核心同时请求内存访问时,内存控制器必须有效地调度内存访问请求,以避免数据冲突和瓶颈。内存的时序参数,如CAS延迟(Column Address Strobe latency)、tRCD(RAS to CAS Delay)、tRP(RAS Precharge Delay)等,对多核心系统的性能也有显著影响。

## 2.3 性能测试方法论

### 2.3.1 基准测试工具与方法

性能基准测试是评估计算机系统性能的常用方法。基准测试通过一系列标准化的测试程序来模拟各种计算任务,以此评估系统的处理能力。常用的基准测试工具包括Cinebench、AIDA64、SiSoft Sandra等。

在进行基准测试时,选择合适的测试项目至关重要,这取决于我们希望评估的系统方面。例如,CPU的性能可以通过渲染、解压缩或加密任务来评估,而内存性能则可以通过数据读写测试来衡量。

### 2.3.2 性能指标分析

性能测试结果的分析需要关注多个指标,包括但不限于处理速度、内存吞吐量、延迟和系统稳定性。处理速度通常以每秒完成任务的数量来衡量,而内存吞吐量则反映了数据传输的速率。

延迟是指请求和响应之间的时间间隔,它在多核心系统中尤其重要,因为高延迟会限制核心之间的通信速度,从而影响性能。系统稳定性则关注系统在长时间运行基准测试时是否会出现故障或性能下降,这对于确定系统的可靠性至关重要。

在下一章节中,我们将深入探讨MT41J256M16 DDR3内存的特性,并分析其在多核心CPU系统中的作用。这将包括内存规格的详细解读,内存与CPU核心之间的交互,以及如何进行故障诊断和系统性能优化。

# 3. MT41J256M16 DDR3内存特性分析

## 3.1 MT41J256M16 DDR3规格解读

### 3.1.1 内存颗粒的性能参数

MT41J256M16 DDR3是由美光科技生产的一款16位宽度的DDR3内存颗粒,其容量为2Gb(Gigabit),工作电压为1.35V至1.5V。这款内存颗粒提供多种速度等级,比如1066MHz和1333MHz,每秒传输速率分别为8533MT/s(百万传输/秒)和10667MT/s。其低电压设计不仅降低了功耗,也提供了良好的节能性能。

在深入了解性能参数前,需要明确内存的数据传输率、时序参数、以及容量和频率之间的关系。MT41J256M16 DDR3颗粒的CL(CAS Latency,列地址选通脉冲延迟)是内存时序的关键参数之一,CL值越小,表示内存读取数据的响应速度越快。此外,还包含其他一些时序参数如tRCD、tRP和tRAS等,这些都会影响内存整体性能。

表格 3.1 展示了MT41J256M16 DDR3内存颗粒的性能参数实例:

| 参数名 | 描述 | 示例值 |

| --- | --- | --- |

| 内存类型 | DDR

0

0