【电子工程必学课程】:CLA182先行进位电路的精髓与实际应用解析

摘要

先行进位电路作为数字逻辑设计中的基础组成部分,对处理器的运算速度和效率有着至关重要的影响。本文首先概述了先行进位电路的基础知识和理论基础,重点分析了进位逻辑的原理、先行进位算法以及电路设计原则。随后,文章深入探讨了先行进位电路的关键技术,包括逻辑门级实现、超前进位链的设计优化以及时序分析和优化策略。在实践应用方面,本文讨论了先行进位电路在处理器设计和FPGA设计中的应用,以及故障诊断与测试方法。最后,文章展望了先行进位电路的未来发展趋势,包括多级结构的设计、功耗优化技术以及新型半导体技术的影响。通过这一系列的讨论,本文旨在为设计高性能数字电路提供参考和指导。

关键字

先行进位电路;进位逻辑;超前进位链;时序分析;功耗优化;故障诊断

参考资源链接:四位先行进位电路设计:Educoder计算机组成原理课程实验第二关

1. 先行进位电路概述

先行进位电路是一种在数字逻辑设计中广泛使用的技术,特别是在高速处理器和其他数字集成电路中。其核心目的是解决传统串行进位方法在处理复杂加法运算时速度较慢的问题。先行进位电路通过并行处理,极大地提高了运算速度,对于缩短电路延迟、提升系统性能至关重要。

1.1 先行进位电路的历史背景

先行进位电路的历史可以追溯到20世纪50年代,当时计算机工程师开始寻找提高算术运算速度的方法。当时的处理器主要采用串行进位方式,加法运算的效率低下,严重制约了处理器性能的提升。先行进位电路的出现,无疑成为提升加法运算速度的一大突破。

1.2 先行进位电路的重要性

在现代电子设计中,先行进位电路的重要性不容小觑。它不仅应用在处理器的算术逻辑单元(ALU)中,而且对提高CPU的运行效率、降低功耗都有显著作用。其设计的优化,直接关系到整个系统的性能表现。先行进位电路的设计与实现,因此成为了电子工程师必须掌握的关键技能之一。

2. 先行进位电路的理论基础

2.1 进位逻辑的基础概念

2.1.1 进位的定义和类型

进位是数字加法运算中一种特殊的现象,当相加的两个数字在某一位上的和超过了该位能表示的最大数值时,就会产生一个进位。进位可以分为两类:普通进位和超前进位。

普通进位发生在个位数相加时,其结果超过9,此时需要向十位数进一位。在二进制加法中,当两个一位二进制数相加,和为"10"时也会产生进位,进位值为1。

超前进位是一种优化的进位方式,它预测了进位的发生,因而能显著加快加法器的运算速度。在二进制系统中,对于每一位,超前进位会预先计算出进位和被加数与加数的高位是否有进位输出的关系。

2.1.2 二进制加法及其进位问题

二进制加法是数字电路设计中的基础运算。它遵循与十进制加法类似的原则,只不过是在二进制系统中进行。二进制加法的进位问题在于,每一位的计算结果可能影响到高位的计算。例如,两个二进制数1010和1101相加的结果为10111,需要在二进制位间正确地传递进位。

2.2 先行进位算法的原理

2.2.1 先行进位的算法原理

先行进位(Carry Look-Ahead)算法是一种减少加法器中进位延迟的技术。它利用了进位的规律性,通过组合逻辑预先计算出每一位可能产生的进位,从而减少等待时间。

算法原理主要包括两部分:

- 生成信号(Generate)和传播信号(Propagate),这些信号用来标识每一位的加法操作是否会产生进位。

- 利用生成信号和传播信号快速计算出进位信号,使得每一位加法可以并行进行,而不是串行等待。

2.2.2 串行进位与并行进位的比较

串行进位(Ripple Carry)是最简单的加法器实现方式,其进位是逐位向高位传递的,每一位加法的完成依赖于前一位加法的结果,这就导致了较大的延迟。

与串行进位相比,先行进位是一种并行进位方式。它通过预先计算每一位的进位,允许所有位同时进行加法运算。尽管实现复杂,但先行进位能够大幅提高加法速度,尤其在处理大位宽的数值时更为明显。

2.3 先行进位电路的设计原则

2.3.1 设计的优化目标

在设计先行进位电路时,有几个优化目标需要考虑:

- 速度:减少延迟是先行进位电路的核心目标之一,设计时应尽可能减少逻辑门级数。

- 面积:电路的物理面积影响了芯片的集成度和成本,应当在保证性能的情况下尽可能地减少使用芯片面积。

- 功耗:高功耗可能导致过热和可靠性问题,电路设计应当尽量减少功耗。

2.3.2 面积、速度和功耗的权衡

在设计先行进位电路时,通常需要在面积、速度和功耗之间做出权衡。为了提升速度,可能会增加额外的逻辑门和连线,这会增加芯片面积和功耗。因此,设计者需要根据实际应用场景的特定需求来决定最合适的平衡点。

实现这一平衡的关键在于综合优化。综合工具会根据设计规范和约束来优化电路,达到既定的性能目标。设计者也可以手工优化关键路径,以进一步提升电路的性能。

先行进位电路理论基础的章节内容到此结束。接下来,我们将深入了解先行进位电路的关键技术,并分析如何实现和优化这些电路。

3. 先行进位电路的关键技术

3.1 逻辑门级的先行进位实现

3.1.1 逻辑门的基础和特性

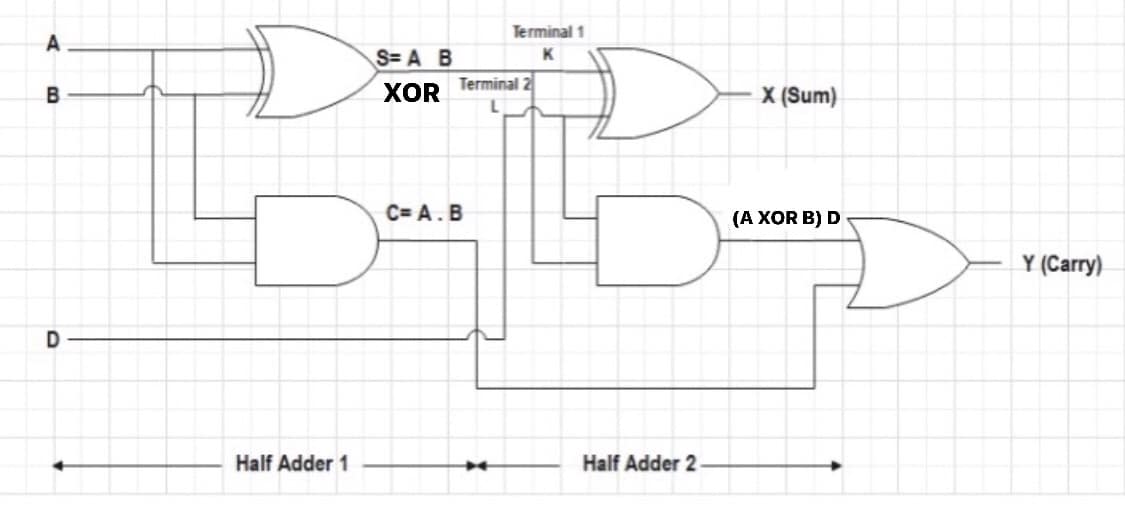

逻辑门是数字电路的基础,其组合可以构建各种复杂的功能模块。在先行进位电路中,逻辑门不仅承担简单的开关功能,更需要精确控制信号的传播时序。在电路设计中,常用的逻辑门包括与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)等。理解这些门的逻辑功能是设计高效先行进位电路的前提。

- 与门(AND):只有所有输入都为1时,输出才为1。在进位电路中,与门用于实现多个条件同时满足的逻辑。

- 或门(OR):只要有任意一个输入为1,输出即为1。在处理多个进位情况时非常有用。

- 非门(NOT):输入信号的反向输出。用于信号的反转,例如在生成反向进位信号时。

- 异或门(XOR):当两个输入不同时输出为1,相同时输出为0。异或门在生成进位信号和执行加法运算时扮演关键角色。

3.1.2 逻辑门级进位电路的设计

在先行进位电路中,通过逻辑门的组合可以构建出高级的进位逻辑。例如,4位二进制加法器的进位可以通过4个全加器(每个全加器由逻辑门构成)级联实现。

一个简单的先行进位逻辑可以用如下方式构建:

- assign c1 = a0 & b0; // 第一级进位,最低位的两个输入相与产生进位

- assign c2 = (a0 & b1) | (a1 & b0) | (a1 & b1); // 第二级进位,通过与、或、非门组合

- assign c3 = (a0 & b2) | (a1 & b2) | (a2 & b1) | (a2 & b2);