【CMOS技术的微电子应用】:应用发展与实践技巧

发布时间: 2024-12-05 06:05:21 阅读量: 46 订阅数: 37

复旦微电子考研资料-教程与笔记习题

参考资源链接:[Fundamentals of Microelectronics [Behzad Razavi]习题解答](https://wenku.csdn.net/doc/6412b499be7fbd1778d40270?spm=1055.2635.3001.10343)

# 1. CMOS技术概述

## 1.1 CMOS技术简介

CMOS(互补金属氧化物半导体)技术是现代电子学的核心技术之一,尤其在微电子领域具有举足轻重的地位。它结合了n型和p型金属氧化物半导体场效应晶体管(MOSFETs),形成互补对,以实现高效、低功耗的电路设计。CMOS技术在集成电路、传感器、微处理器及存储器等多个领域有着广泛的应用,是当今几乎所有数字电子产品的基础。

## 1.2 CMOS技术的重要性

CMOS技术之所以如此重要,关键在于它独特的功耗特性。与传统的双极型技术相比,CMOS技术在静态时消耗的电流几乎可以忽略不计,仅在开关状态切换时才有电流流过,这使得CMOS电路具有极低的功耗和良好的热性能。随着微电子技术的发展,CMOS技术的特征尺寸不断缩小,驱动了计算能力和集成度的指数级增长,同时也推动了便携式电子设备的普及。

## 1.3 CMOS技术的演化

CMOS技术自20世纪70年代初期问世以来,经历了从最初的微处理器和存储器应用到现在复杂的混合信号处理和无线通信设备的演化过程。随着晶体管尺寸的不断缩小,按照摩尔定律,芯片上的晶体管数量每18到24个月就会翻倍,性能和功能得到了显著提升。如今,CMOS技术已经进入了纳米和亚微米技术阶段,科学家们在探索新的物理极限和在这些极限下保持技术进步的方法。

# 2. CMOS技术基础

## 2.1 CMOS基本原理

### 2.1.1 CMOS电路的工作原理

互补金属氧化物半导体(CMOS)技术是微电子学中应用最广泛的集成电路(IC)制造工艺。CMOS电路之所以受到青睐,主要在于其独特的工作原理,它由P型金属氧化物半导体(PMOS)和N型金属氧化物半导体(NMOS)两种类型的晶体管构成。CMOS电路的核心优势在于其极低的静态功耗,这是因为当输入处于静态状态时,只有一对PMOS和NMOS晶体管同时导通,而导通的晶体管数量最小化,从而最大程度减少了漏电流,实现了低功耗。

在CMOS电路中,当输入为逻辑"0"时,PMOS管导通,NMOS管截止,电路输出为逻辑"1";反之,当输入为逻辑"1"时,NMOS管导通,PMOS管截止,电路输出为逻辑"0"。由于任何时刻只有一条路径导通,这种互补特性大大减少了电源到地之间的直接电流路径,使得CMOS电路相对于其他类型的电路在待机时几乎不消耗电流,只有在切换状态时才消耗能量,这为便携式电子设备提供了巨大的优势。

### 2.1.2 CMOS与其它微电子技术的比较

CMOS技术相对于其他微电子技术,如双极型晶体管(BJT)和传统的双极型互补金属氧化物半导体(BiCMOS),具有显著的优势。主要优势在于它在静态功耗上的卓越表现,以及随着特征尺寸的减小而持续提升的性能和降低成本的能力。CMOS技术的功耗随着晶体管的尺寸缩小而降低,这使得它非常适合高密度的集成电路设计。

BJT技术在高频率运行下有更好的性能,但在静态功耗方面,由于BJT在待机状态也会消耗大量电流,因此不适合现代移动电子设备的需求。BiCMOS技术通过结合CMOS的低功耗和BJT的高频性能,试图在CMOS和BJT之间取得平衡,但同时它也继承了这两种技术的缺点,如复杂性高、成本昂贵。因此,CMOS由于其简单、可扩展、低功耗和低成本的特性,成为了现代集成电路设计的首选技术。

## 2.2 CMOS工艺流程

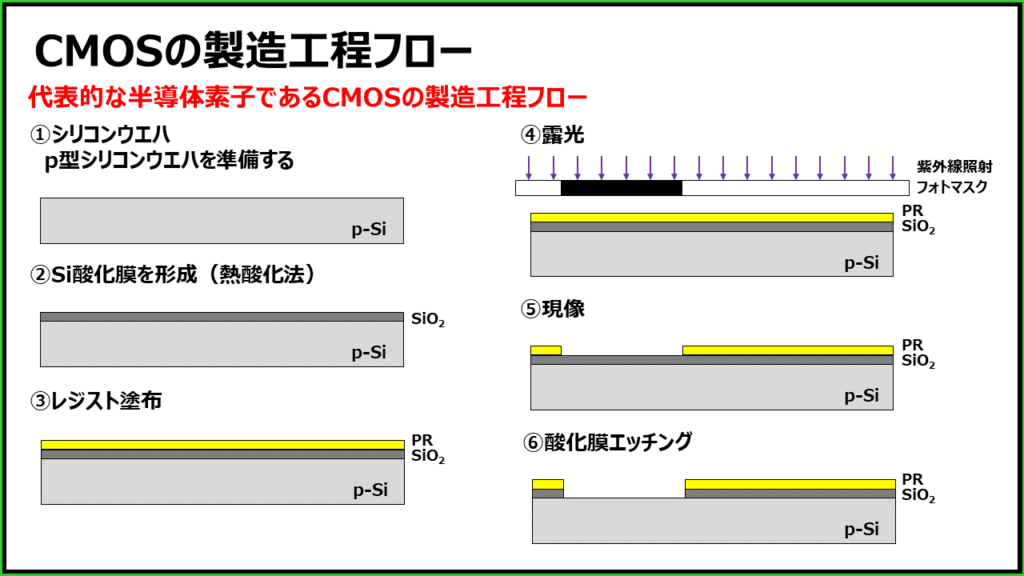

### 2.2.1 晶体管制造的基本步骤

制造CMOS晶体管的流程从准备高纯度的硅晶圆开始。这包括对晶圆进行清洗和氧化,然后在上面沉积一层多晶硅,这将作为晶体管门电极。接下来是掺杂过程,通过离子注入或扩散的方式在硅片上制造出P型和N型掺杂区域,这对应于PMOS和NMOS晶体管的源极和漏极。

接下来是光刻步骤,通过曝光和蚀刻过程定义晶体管的精确位置和尺寸。之后是栅介质的生长,以及随后的离子注入步骤来调整阈值电压。最后,进行金属层沉积、图形化和互连过程,完成晶体管的制造。这整个过程需要极端的洁净室条件,并通过精确控制温度、压力和其他参数来保证晶体管的性能和可靠性。

### 2.2.2 光刻、蚀刻和离子注入技术

光刻过程是CMOS工艺中最为关键的技术之一。在这一过程中,使用紫外光或其他类型的光源通过掩模对光敏性化学物质(光刻胶)进行曝光,形成微小的图案。图案的精度直接决定了晶体管的尺寸和集成电路的集成度。

蚀刻技术随后用于去除未被光刻胶覆盖的部分材料,为晶体管的源极和漏极形成空间。蚀刻可以是湿法或干法,干法蚀刻由于其各向异性好、精度高而成为主流技术。

离子注入是将掺杂材料的离子加速到高能量状态,然后注入到半导体晶片的指定区域以形成源极和漏极。该过程需要精确控制注入的剂量、能量和角度,以确保掺杂区域的性能符合要求。

## 2.3 CMOS电路设计要素

### 2.3.1 电源电压与阈值电压的关系

在设计CMOS电路时,电源电压和晶体管的阈值电压是密切相关的两个重要参数。电源电压决定电路可以处理的最大电压范围,它直接影响电路的性能和功耗。而阈值电压是指晶体管从关闭状态转变到导通状态所需克服的最小电压。合理的阈值电压可以确保晶体管在低电压下正常工作,同时也避免了过大的亚阈值泄漏电流。

在现代CMOS设计中,随着晶体管尺寸的缩小,电源电压有逐渐降低的趋势。这是为了维持晶体管电场强度的合理性,并减少热效应和泄漏电流。然而,降低电源电压可能会导致晶体管的开关速度变慢。因此,设计者必须仔细权衡电源电压和阈值电压的取值,以达到最佳的性能和功耗平衡。

### 2.3.2 电路设计中的功耗管理

功耗管理是CMOS电路设计的重要方面,特别是在电池供电的便携式设备中。CMOS电路的总功耗由动态功耗和静态功耗两部分组成。动态功耗与电路中的开关活动有关,主要由电容充放电引起。动态功耗可以通过降低工作电压和操作频率来减少。

静态功耗或漏电流主要由晶体管的亚阈值导通和栅极漏电流引起。设计时可通过优化晶体管的尺寸、使用高阈值晶体管、采用新的晶体管结构如FinFET来降低漏电流。在系统级,采用动态电压频率调整(DVFS)和功率门控技术可以进一步降低功耗。

通过优化设计技术和选择合适的制造工艺,CMOS电路可以在保持高性能的同时实现低功耗,满足

0

0