硬件时钟域交叉问题分析:同步时序一致性的权威解读

发布时间: 2024-12-22 10:45:17 阅读量: 6 订阅数: 9

果壳处理器研究小组(Topic基于RISCV64果核处理器的卷积神经网络加速器研究)详细文档+全部资料+优秀项目+源码.zip

# 摘要

硬件时钟域交叉问题是集成电路设计中的一个复杂问题,它涉及不同频率或相位的时钟信号之间的同步与交互。这些问题可能引起信号稳定性问题、数据丢失和时序冲突,对系统性能造成严重影响。本文综合分析了时钟域交叉问题的理论基础、诊断与分析方法、以及解决方案。通过介绍时钟域的基本概念和同步技术,本文旨在提供对时钟域交叉问题的深入理解,并探讨基于同步机制的建立、时钟域转换器的应用以及设计优化策略的解决方案。同时,本文通过案例分析,展示了这些理论和方法在实际硬件系统中的应用和效果评估。最后,本文探讨了时钟域交叉问题的研究新动向和未来发展趋势,包括新型同步技术的发展,以及面向未来设计挑战和行业标准的未来方向。

# 关键字

时钟域交叉;时钟同步;信号稳定性;数据丢失;同步机制;设计优化策略

参考资源链接:[华为单板硬件信号质量与时序测试详述](https://wenku.csdn.net/doc/63yg1tgykm?spm=1055.2635.3001.10343)

# 1. 硬件时钟域交叉问题概述

硬件设计中的时钟域交叉问题是影响系统稳定性和性能的关键因素之一。时钟域交叉是指在数字电路中,当信号从一个时钟域传递到另一个时钟域时,因为时钟频率或相位的不同步,可能导致数据采样错误、时序冲突,甚至损坏硬件的风险。随着集成电路的复杂性不断增长,时钟域交叉问题变得越发突出,对于5年以上的IT专业人员来说,理解并掌握解决这些问题的技巧和方法是必要的。接下来的章节将详细探讨时钟域交叉问题的理论基础、诊断分析、解决方案以及实际案例,为读者提供系统性的知识架构和实践经验。

# 2. 时钟域交叉问题的理论基础

时钟域交叉问题是在数字电路设计中非常重要的一个主题,它与系统的稳定性和性能有着直接的联系。理解这个问题的理论基础是至关重要的,它不仅涉及到时钟域和时钟同步的概念,还包括了时钟域交叉的分类、特征以及同步时序一致性的重要性。本章节将详细探讨上述概念及其重要性。

## 2.1 时钟域和时钟同步概念

### 2.1.1 时钟域定义及其重要性

时钟域是数字系统中由特定时钟信号控制的逻辑部分。每个时钟域拥有其独立的时钟,且时钟域内所有的同步元件都在相同的时钟边沿触发。时钟域的划分依据可以是物理位置、功能模块、或者不同的时钟频率需求。

在多时钟域系统中,时钟域的重要性不容小觑。由于各个时钟域可能运行在不同的频率,设计时必须保证信号在跨域传输时的稳定性和正确性,否则将引起数据损坏、系统崩溃等严重问题。例如,在CPU和外设通信的场景中,CPU内部可能运行在一个非常高的时钟频率下,而外设可能只需要一个较低频率的时钟信号,这就需要在两个时钟域之间建立一个可靠的信号传输机制。

### 2.1.2 时钟同步原理和方法

时钟同步是指在多时钟域系统中,使得不同时钟域中的事件能够被正确地排序和关联。这对于数据的一致性与系统整体的稳定性至关重要。时钟同步的原理主要通过在信号路径中引入一些同步机制来实现,常见的同步方法包括:

- 双触发器同步:这是一种非常普遍的同步方法,通过在接收时钟域中使用两个连续的触发器来减少亚稳态的影响。

- 元缓冲区(FIFO)队列技术:它适用于数据速率不匹配的两个时钟域之间的数据传输,可以有效避免时钟域交叉带来的问题。

## 2.2 时钟域交叉的分类和特征

### 2.2.1 单向时钟域交叉

单向时钟域交叉是时钟域交叉问题中较为简单的一种情况。在这种情况下,信号仅在一个方向上从一个时钟域传输到另一个时钟域。这种类型的交叉相对容易管理和同步,因为它只涉及一个方向的数据流。为了保证数据的正确性,需要在信号传输的路径上加入适当的同步机制。

### 2.2.2 双向时钟域交叉

双向时钟域交叉比单向时钟域交叉更为复杂,因为信号需要在两个方向上穿越时钟域。这种情况下,同步机制必须考虑到信号在两个方向上可能遇到的时序问题。双向时钟域交叉常发生在需要双向数据通信的接口设计中,如UART、SPI等通信协议。

## 2.3 同步时序一致性的重要性

### 2.3.1 时序一致性的定义

时序一致性指的是信号在不同时钟域之间传输时,其在时间上的一致性和正确性。时序一致性要求信号的采样和传输必须满足时序要求,不能出现数据竞争和竞争冒险等问题。在数字系统设计中,时序一致性是保证系统可靠性和功能正确性的重要因素。

### 2.3.2 时序一致性对系统性能的影响

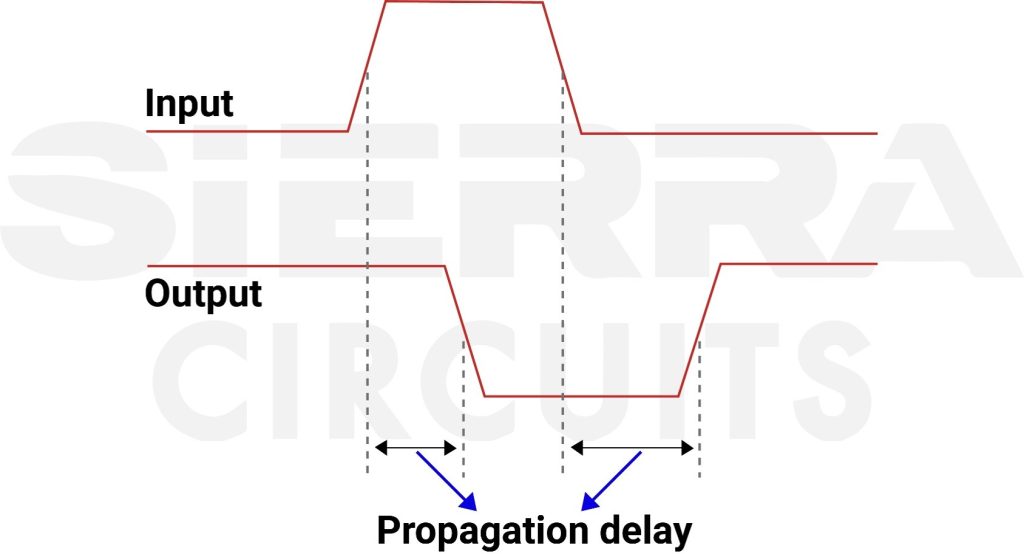

时序一致性对于系统性能的影响是深远的。如果时序不一致,那么在高速运行的系统中,将很可能导致信号抖动、数据丢失、甚至整个系统的崩溃。因此,设计时必须考虑到时序一致性,通过设计适当的同步机制来保证信号的稳定传输。此外,时序一致性的维护还涉及到时钟树的设计优化和逻辑电路的优化,这些都是保证系统性能的关键步骤。

在下一章节中,我们将详细介绍如何诊断和分析时钟域交叉问题,并讨论可用的工具和技术。

# 3. 时钟域交叉问题的诊断与分析

## 3.1 时钟域交叉问题的常见症状

### 3.1.1 信号稳定性问题

在多时钟域设计中,信号稳定性问题是一个典型的时钟域交叉问题症状。这通常是由信号在从一个时钟域传输到另一个时钟域时,由于时钟频率不匹配而引发的。信号稳定性问题可能会导致数据在不适当的时钟边沿被采样,造成数据错误或者不确定性。例如,当一个信号从一个频率较低的时钟域传输到一个频率较高的时钟域时,信号可能在高频率的时钟域中产生抖动,导致在采样时无法正确识别信号的真实电平。

在实际的硬件设计中,信号稳定性问题的检测和分析可以通过逻辑分析仪或者示波器来完成。通过观察信号的时序图,可以发现信号在不同时钟域中的稳定性和准确性。

### 3.1.2 数据丢失和时序冲突

数据丢失是时钟域交叉问题中更为严重的问题,它会导致系统功能上的缺陷。这通常是由于信号没有在正确的时钟边沿被采样,或者在时钟域转换的过程中由于竞争条件而产生的。当设计中存在不正确的信号缓冲或者信号同步时,数据丢失问题尤其容易发生。

时序冲突是指在多时钟域设计中,由于信号在不同时钟域的边界上没有得到正确的处理,从而引起数据采样的时间点冲突。冲突的结果可能是两个时钟域中都采样到了错误的数据值。

为了识别和解决这些问题,设计人员需要对信号路径进行彻底的时序分析,并使用静态时序分析工具来预测和解决可能的时序冲突。

## 3.2 时钟域交叉问题的检测方法

### 3.2.1 静态时序分析

静态时序分析(Static Timing Analysis, STA)是一种广泛使用的时钟域交叉问题检测方法。静态时序分析工具可以分析电路中所有的信号路径,包括那些跨越时钟域的路径,并且预测信号在不同时钟域边界上的时序问题。STA工具提供了一种不需要实际运行硬件就能检测时序问题的手段,这使得它可以更早地发现问题并进行解决。

STA工具通常包括以下功能:

- 时钟域分析:分析电路中的所有时钟域,并标识出可能的时钟域交叉点。

- 数据路径分析:检测跨越时钟域的信号路径,并计算路径延迟。

- 时序约束:定义电路的时序要求,例如时钟周期、建立时间、保持时间等。

- 报告:生成详细报告,指示所有违反时序要求的路径和潜在问题。

### 3.2.2 动态仿真测试

除了静态时序分析之外,动态仿真测试是另一种检测时钟域交叉问题的方法。与静态时序分析关注电路的结构和时序约束不同,动态仿真测试侧重于电路在实际运行时的行为。动态仿真通常使用仿真工具模拟电路,可以观察到信号在各个时钟域之间传递时的具体波形和时序,以便更精确地定位问题。

动态仿真测试的优点在于:

- 可以考虑电路的动态行为,包括信号在实际电路中的传播延迟。

- 可以使用测试向量来模拟特定的操作场景,检查在特定条件下电路的响应。

- 能够更直观地展示信号的时序关系,帮助设计人员理解时钟域交叉问题的产生原因。

为了有效地使用动态仿真测试,设计人员需要准备详尽的测试向量和监测点,确保覆盖所有可能的时钟域交叉场景。

## 3.3 时钟域交叉问题的分析工具

### 3.3.1 时钟域交叉分析软件工具

时钟域交叉问题分析软件工具是帮

0

0