【Zynq-7020高速PCB设计精髓】:多层电路板设计,原理图解读要点

发布时间: 2024-12-18 16:59:49 订阅数: 3

ZYNQ-ZC7020硬件原理图和PCB图

# 摘要

本文综合介绍了Zynq-7020处理器的高速PCB设计基础和实践。首先,概述了Zynq-7020的特点及高速PCB设计的基本原理。随后,深入探讨了多层电路板设计的关键要素,包括信号层和电源层设计、高速信号的布线策略以及PCB叠层结构与材料选择。第三章专注于Zynq-7020高速PCB原理图的解读,详细讲解了原理图的组成、分析方法和关键信号处理,特别是时钟网络的布局、电源与地线的规划,以及高速信号的设计。第四章讨论了高速PCB设计的实际操作流程,包括软件工具的选择、设计验证与仿真、以及制造与测试的要点。最后,第五章通过案例分析展示了Zynq-7020高速PCB设计的应用,着重解决设计过程中的关键问题,并提出了设计评估与优化的建议。本文为设计人员提供了全面的高速PCB设计知识,旨在优化Zynq-7020系统的性能和可靠性。

# 关键字

Zynq-7020;高速PCB设计;多层电路板;阻抗匹配;信号完整性;设计验证;EMC测试;案例分析

参考资源链接:[Xilinx Zynq7020开发板详细原理图详解](https://wenku.csdn.net/doc/3kwsycq1bp?spm=1055.2635.3001.10343)

# 1. Zynq-7020概述与高速PCB设计基础

## 1.1 Zynq-7020概述

Xilinx的Zynq-7000系列中,Zynq-7020是其中的一个重要成员,它将双核ARM Cortex-A9处理器和Xilinx 7系列FPGA逻辑完美集成在了一起,为开发者提供了高性能、低功耗、丰富的接口和高度灵活的设计平台。Zynq-7020具有极高的性价比,非常适合于多变和复杂的应用场景,例如工业自动化、车载娱乐系统、无线通信设备等。

## 1.2 高速PCB设计基础

高速PCB设计是一个复杂的工程,涉及到众多的理论与实践知识。设计者需要对高速信号的传输机理、PCB材料的电气特性、电路板制造工艺、信号完整性、电源完整性等有深入的理解。在Zynq-7020这样的SoC平台上,高速PCB设计尤为重要,因为这关系到系统性能的发挥和稳定性。

## 1.3 高速PCB设计要点

高速PCB设计的关键在于确保信号的准确无误传输和电源供应的稳定性。设计者需要遵循一些基本原则,例如保持高速信号走线尽可能短,对高速信号进行恰当的阻抗控制和匹配,避免信号间的串扰,以及确保电源与地线的合理布局。在下一章节,我们将详细讨论多层电路板的设计要点和高速信号的布线策略,为深入理解Zynq-7020的高速PCB设计打下基础。

# 2. 多层电路板设计基础

### 2.1 多层电路板的设计要点

#### 2.1.1 层数选择与布局

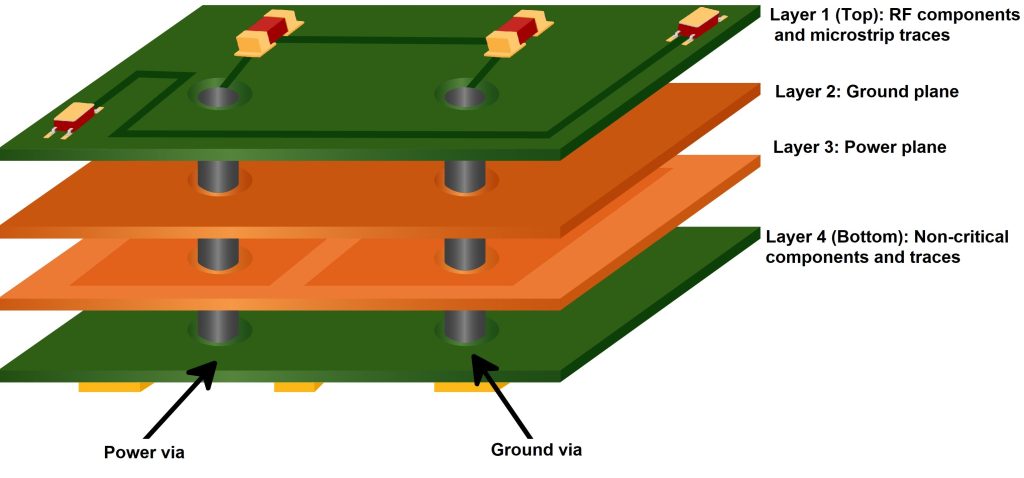

多层电路板设计中,首先需要确定的是层数以及它们的布局。每一层都有其特定的功能,例如,信号层用于传输信号,电源层和地层则为电路提供稳定的电源和参考电位。在设计时,要综合考虑信号的种类、数量、速率以及信号之间的相互干扰等因素,合理分配各层。

多层板设计的第一步是确定层数,这通常基于产品的信号完整性和电源完整性要求来决定。一般而言,层数越多,设计就越容易满足高速信号的传输要求,因为可以有更多层专门用于布置地平面和电源平面。但同时,层数增加也会带来成本和生产复杂性的提升。

在确定层数后,就需要合理布局各层。理想情况下,相邻层的信号走线应尽量垂直,以减少层间的串扰。电源层和地层应该相邻放置,以提供良好的屏蔽效果和较短的返回路径。

```mermaid

flowchart LR

A[多层电路板设计] --> B[确定层数]

B --> C[分配层功能]

C --> D[布局策略]

D --> E[层间走线安排]

E --> F[设计验证]

```

#### 2.1.2 信号层和电源层设计原则

信号层设计是多层电路板设计的核心部分,需要遵循特定的设计原则以确保信号的完整性。高速信号应该尽量短,直线走线,以减少传输损耗和串扰。此外,走线的布局应避免紧挨着不同的电压层,以减少电容耦合。

在电源层设计方面,设计者需要确保充足的电源平面对高速信号提供稳定的电源,并且布线尽量粗,减少电源线路上的阻抗。一般采用较大的铜箔面积来减少线路的电阻和电感,从而改善电源的质量。

此外,信号层与电源层之间必须有适当的隔离,以避免干扰。隔离的常用手段包括增加绝缘层厚度或使用具有高介电常数的材料。

```mermaid

graph TD

A[信号层与电源层设计] --> B[信号层设计原则]

B --> C[高速信号布线]

C --> D[避免信号干扰]

A --> E[电源层设计原则]

E --> F[稳定电源供应]

F --> G[减少阻抗]

D --> H[层间隔离]

G --> H[设计验证]

```

### 2.2 高速信号的布线策略

#### 2.2.1 阻抗控制与匹配技术

在高速电路设计中,阻抗控制是保证信号完整性的重要因素之一。不匹配的阻抗会导致信号反射,从而影响信号质量。因此,必须确保传输线的特性阻抗与信号源和接收端的阻抗相匹配。

特性阻抗的计算和控制通常依赖于走线的宽度、厚度以及周围介质的介电常数。设计者需要使用高速PCB设计软件来计算和优化走线的特性阻抗,确保在高速信号传输时保持一致。

```mermaid

flowchart LR

A[阻抗控制与匹配] --> B[计算走线特性阻抗]

B --> C[阻抗匹配设计]

```

0

0