【XCHG指令的原子操作】:揭秘现代处理器中的同步机制

发布时间: 2025-01-09 09:03:10 阅读量: 6 订阅数: 5

常用汇编指令汇总 如: POP 把字弹出堆栈

# 摘要

本文深入探讨了XCHG指令在实现原子操作中的基础理论、实践应用及在不同编程语言中的具体实现。分析了原子操作与同步机制的理论基础,以及XCHG指令在并发编程和性能优化中的关键作用。文章进一步探索了XCHG指令在多线程环境中的应用案例,特别是在现代处理器同步技术中的地位。此外,本文还讨论了XCHG指令的局限性,以及未来在同步机制,包括混合同步策略和量子计算方面的潜在发展方向。最终,通过高级主题的深入分析,提出了在硬件事务内存和非阻塞同步中的应用及优化技巧。

# 关键字

XCHG指令;原子操作;同步机制;并发编程;性能优化;硬件事务内存

参考资源链接:[XCHG指令详解:数据交换与注意要点](https://wenku.csdn.net/doc/5nyi1qvzkb?spm=1055.2635.3001.10343)

# 1. XCHG指令的原子操作基础

在现代计算机体系结构中,XCHG指令是一个基础而又关键的操作,它代表了"交换"的含义,在多线程和并发环境中扮演着重要的角色。XCHG指令能够保证在读写数据时不会被其他线程中断,确保了数据交换的原子性。理解XCHG指令不仅仅是理解一个简单的汇编命令,更是深入探讨了计算机如何保证操作的原子性以及其对并发编程的影响。

## 原子操作的定义与重要性

在多线程环境中,"原子操作"是指不可被线程调度机制打断的操作,一旦开始执行,就一定会完成。XCHG指令作为一种原子操作,保证了数据交换的即时性和一致性,是实现线程安全的基石之一。

## XCHG指令的作用范围

XCHG指令通常用于交换寄存器或内存位置的值。在并发控制场景下,可以用来实现锁机制中的"比较并交换"(Compare-And-Swap, CAS)操作,支持非阻塞同步技术,提高了程序的性能和响应速度。

通过后续章节的深入分析,我们将探讨XCHG指令在多线程同步、性能优化以及现代编程语言中的应用,进一步揭示其在现代软件开发中的作用和价值。

# 2. 原子操作与同步机制的理论

### 2.1 同步机制的必要性

#### 2.1.1 多线程环境下的数据一致性问题

在现代计算机系统中,多线程编程是构建高效、响应迅速的软件的基础。然而,当多个线程尝试同时访问和修改同一块内存位置时,数据一致性问题便成为一个挑战。如果没有适当的同步机制,这种情况可能会导致竞态条件(race conditions),从而引起程序的不确定性和潜在的错误。

竞态条件是指系统的输出结果取决于事件发生的相对时间或顺序,这在多线程环境中尤为常见。例如,当两个线程同时对同一个变量进行递增操作时,如果没有同步机制确保操作的原子性,那么最终的结果可能只是增加了1,而不是预期的2。

为了解决这一问题,需要采用各种同步机制来确保数据的一致性和线程的安全执行。原子操作就是这类同步机制之一,它可以保证一个操作的执行是不可分割的,从而避免在多线程环境中产生数据竞争的问题。

#### 2.1.2 原子操作在并发控制中的角色

原子操作是并发控制中一个基础的概念,它指的是不可分割的操作,即在执行过程中不会被其他线程中断。这类操作对程序的其他部分来说,要么完全未发生,要么已经完成了全部步骤。

在并发编程中,原子操作扮演着至关重要的角色。例如,它可以用来实现锁(lock)机制中的关键部分,保证了对共享资源的安全访问。又如,在无锁编程(lock-free programming)中,原子操作可以用来构建复杂的数据结构和算法,如无锁队列和原子计数器。

原子操作可以由硬件直接支持,也可以通过软件方法实现。硬件级别的原子操作通常是由现代处理器提供的特定指令完成的,如x86架构中的XCHG指令。软件级别的原子操作则可能需要利用锁或者更高层次的抽象来实现,但这些通常会引入更多的开销和复杂性。

### 2.2 XCHG指令的技术原理

#### 2.2.1 XCHG指令的工作流程解析

XCHG指令是处理器提供的一个原子操作指令,它可以交换两个操作数的值。在x86架构中,XCHG指令可接受寄存器与寄存器,或者寄存器与内存地址之间的数据交换。

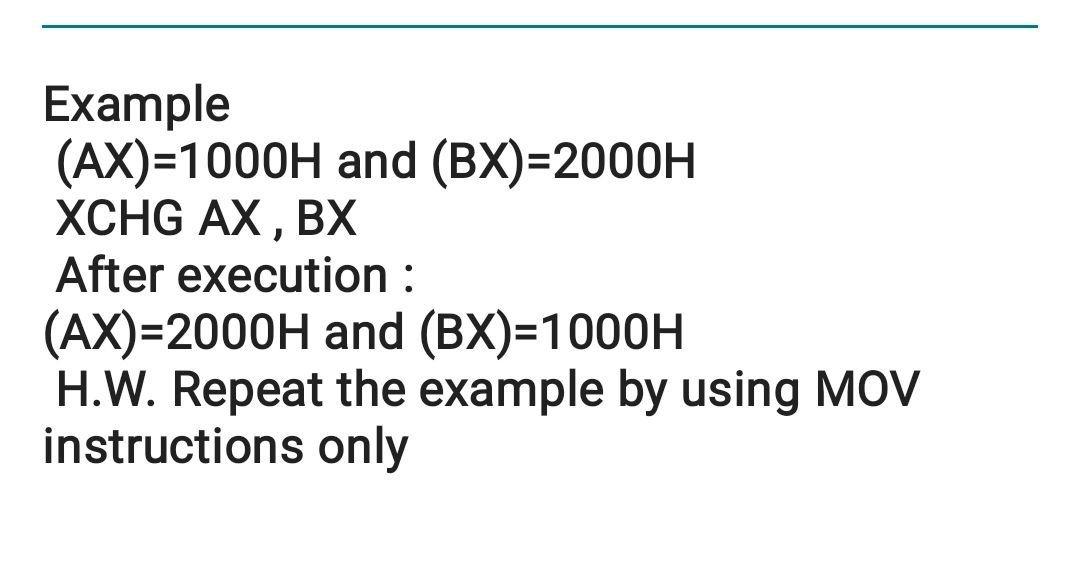

一条典型的XCHG指令格式如下:

```assembly

XCHG destination, source

```

这条指令执行的操作是将`destination`和`source`的内容互换。从执行效果上来看,XCHG指令保证了整个交换过程的原子性,这意味着在任何时候都不会有中间状态被其他线程看到,从而保证了操作的同步性。

#### 2.2.2 原子操作与指令级同步

XCHG指令的原子性保证了它在并发编程中的重要角色。它不仅仅是一个简单的数据交换命令,而是提供了在指令级别上的同步机制。当多个线程或进程尝试通过XCHG指令访问同一资源时,处理器能够确保所有操作的顺序性和一致性,从而防止并发环境中的数据竞争和状态冲突。

指令级同步的一个关键点是内存访问的顺序。处理器内部的乱序执行可能导致指令执行的顺序与程序代码中的顺序不一致,但XCHG指令确保了在其执行期间内存访问的顺序性,这是它区别于其他非原子指令的一个重要特点。

#### 2.2.3 XCHG与其它原子指令的比较

在x86架构中,除了XCHG指令之外,还有其他一些提供原子操作的指令,比如CMPXCHG(比较并交换)和LOCK前缀的指令(例如LOCK ADD)。这些指令在功能和使用场景上都有所区别。

CMPXCHG指令可以比较两个值,并且在它们相等时交换另一个值,这在实现同步和等待某些条件成立时非常有用。而LOCK前缀可以被用来确保指令操作的原子性,它可以与许多指令(如ADD, XOR等)一起使用,提供对共享内存位置的原子访问。

与XCHG相比,这些指令提供了更多的功能和灵活性,但在某些情况下,XCHG指令提供的简单交换操作可能是更快和更适合的选择。选择特定的原子指令通常取决于具体的应用场景和性能需求。

### 2.3 现代处理器的同步技术

#### 2.3.1 缓存一致性协议

现代多核处理器设计中,缓存一致性协议是保证数据一致性的关键技术之一。由于每个核心可能拥有自己的私有缓存,所以需要一种机制来确保当一个核心更新了缓存中的数据时,其他核心上的相应缓存行也能够得到更新或者失效。

MESI协议(修改 Exclusive Shared Invalid)是缓存一致性协议中常见的一种。它定义了缓存行的四种状态,即修改态、独占态、共享态和无效态,以此来维护缓存数据的一致性。当一个核心需要读取或写入一个数据项时,缓存一致性协议确保它能获取到最新的数据。

#### 2.3.2 硬件事务内存(HTM)的概念及应用

硬件事务内存(HTM)是一种新型的同步机制,它在硬件层面提供了事务内存的概念,允许代码块以事务的形式执行。硬件事务内存简化了并发编程,因为它通过硬件直接支持原子性、一致性和隔离性(ACI),这些通常是软件事务内存(STM)所要解决的问题。

在使用HTM时,如果事务中的指令序列成功执行完毕而没有冲突,则该事务提交,并将对内存的所有更改变为永久性的。如果有冲突发生,事务将回滚,并可能重试。

HTM的引入为并发编程提供了新的可能性,尤其是在开发多线程应用程序时,可以减少编程复杂度并提升性能。但HTM目前仍然是一个活跃的研究领域,不同的处理器制造商可能提供了不同的实现方式,这在某种程度上增加了HTM应用的复杂性。

## 代码块示例

```assembly

; 示例汇编代码,展示XCHG指令的使用

section .text

global _start

_start:

; 假设我们有两个寄存器EAX和EBX,里面存储着值

mov eax, 10

mov ebx, 20

; 使用XCHG指令交换这两个寄存器的值

xchg eax, ebx

; 此时,EAX中的值变为20,而EBX中的值变为10

; 在复杂的并发环境中,XCHG指令保证了交换过程的原子性

; 其他代码...

```

上述代码展示了如何在汇编语言中使用XCHG指令来交换两个寄存器的值。在并发编程中,如果多线程环境下的线程执行这段代码,XCHG指令将确保交换操作不会被任何其他操作打断,从而避免潜在的数据不一致问题。

## 表格示例

| 指令 | 作用 | 使用场景 |

| --- | --- | --- |

| XCHG | 交换两个操作数的值,并保证原子性 | 用于实现线程间的同步 |

| CMPXCHG | 比较两个值并在相等时交换 | 实现复杂的同步机制,如等待条件满足 |

| LOCK ADD | 锁定总线并原子执行加法操作 | 实现原子的计数器增加等操作 |

表格列出了XCHG与其他原子指令在作用和使用场景上的对比。每条指令都有其独特之处和适用情况,理解它们可以帮助开发者在不同的并发编程场景中做出更合理的选择。

# 3. XCHG指令原子操作的实践应用

理解原子性是并发编程中的核心概念,它保证了即使在多线程环境下,某些操作仍然是不可分割的,从而维护了数据的一致性。XCHG指令(Exchange指令)是实现原子操作的关键工具之一。它不仅能够在单个处理器内部保证操作的原子性,还可以在多处理器环境中协助实现复杂的数据同步和通信机制。本章将深入探讨XCHG指令的实践应用,包括在锁机制中的作用、并发编程中的使用场景,以及如何通过XCHG指令进行性能优化。

## 理解原子性与锁机制

### 锁的基本概念和类型

在并发环境中,锁是一种同步机制,用于控制多个线程对共享资源的访问。它确保了当一个线程在修改共享资源时,其他线程不能同时进行访问。从实现的角度来看,锁通常分为几种类型,包括互斥锁(Mutex)、读写锁(Read-Write Lock)等。

- 互斥锁(Mutex)是保证互斥访问资源的锁。任何时刻,只有一个线程可以持有互斥锁。如果其他线程尝试获取已被持有的互斥锁,则它们将被阻塞,直到锁被释放。

- 读写锁(Read-Write Lock)允许多个读操作同时进行,但写操作是互斥的,同时它也保证在写操作进行时不会有新的读操作开始。这种类型的锁适合读多写少的场景。

在这些锁的实现中,原子性是不可或缺的。例如,获取互斥锁的基本过程可以被视为一系列原子操作:检查锁的状态,如果锁未被占用,则尝试更改其状态以表示已被占用。

### 原子操作在锁实现中的应用案例

为了更具体地理解原子操作如何在锁中起作用,让我们来看一个简单的互斥锁实现:

```c

#include <pthread.h>

// 定义互斥锁结构

typedef struct {

int locked; // 锁的状态,0表示未锁定,1表示锁定

} mutex_t;

// 初始化互斥锁

void mutex_init(mutex_t *mutex) {

mutex->locked = 0;

}

// 尝试获取锁

void mutex_lock(mutex_t *mutex) {

// 不断尝试直到成功

while (mutex->locked) {

// 如果锁已被占用,则持续循环

}

mutex->locked = 1;

}

// 释放锁

void mutex_unlock(mutex_t *mutex) {

mutex->locked = 0;

}

```

尽管上述代码是一个非常简单的互斥锁实现,但在此模型中,`while (mutex->locked)` 这个循环以及随后的赋值操作 `mutex->locked = 1` 是原子操作的示例。如果两个线程几乎同时调用 `mutex_lock`,那么只有一个线程能够先到达循环条件检查并获取锁。

在现代的多核心处理器中,XCHG指令可用于在单个操作中检查并修改互斥锁的状态。下面是一个使用XCHG指令的例子:

```c

#include <pthread.h>

#include <stdint.h>

#include <stdatomic.h>

// 使用原子变量实现互斥锁

typedef struct {

atomic_int locked;

} mutex_t;

// 初始化互斥锁

void mutex_init(mutex_t *mutex) {

atomic_init(&mutex->locked, 0);

}

// 尝试获取锁

void mutex_lock(mutex_t *mutex) {

// 使用原子操作交换变量值

while (atomic_exchange(&mutex->locked, 1)) {

// 如果锁已被占用,则持续循环

}

}

// 释放锁

void mutex_unlock(mutex_t *mutex) {

atomic_store(&mutex->locked, 0);

}

```

在上述代码中,`atomic_exchange` 函数利用了原子操作来确保在检查锁的状态和获取锁这两个动作之间的原子性。这是非常重要的,因为它避免了条件竞争(race condition),确保了即使多个线程在不同核心上同时执行这些操作,也会有一个线程先于其他线程完成,从而保证了锁的正确性。

## XCHG指令在并发编程中的使用

### 线程间同步与通信

在并发编程中,线程间同步和通信是一个常见的需求。XCHG指令在这里扮演了一个关键角色。通过确保操作的原子性,它能够帮助程序员在多个线程间同步状态,而不需要使用复杂且效率低下的锁机制。

### 实际场景中的原子操作示例

让我们以生产者-消费者问题为例,看看如何使用XCHG指令来实现线程间的同步与通信:

```c

#include <pthread.h>

#include <stdatomic.h>

#define BUFFER_SIZE 10

// 定义缓冲区和相关变量

int buffer[BUFFER_SIZE];

atomic_int in = ATOMIC_VAR_INIT(0);

atomic_int out = ATOMIC_VAR_INIT(0);

// 生产者线程将数据放入缓冲区

void* producer(void* arg) {

int item;

while (1) {

item = produce_item(); // 假设这是一个生成数据的函数

int pos = atomic_fetch_add(&in, 1) % BUFFER_SIZE;

buffer[pos] = item;

// 这里不需要锁,因为XCHG保证了原子性

}

}

// 消费者线程从缓冲区取出数据

void* consumer(void* arg) {

while (1) {

int pos = atomic_fetch_add(&out, 1) % BUFFER_SIZE;

int item = buffer[pos];

consume_item(item); // 假设这是一个消费数据的函数

// 这里也不需要锁

}

}

```

在这个例子中,生产者和消费者线程分别使用 `atomic_fetch_add` 函数来更新生产者和消费者的位置指针。这个函数将读取位置指针的当前值,增加一个值,并返回增加前的指针位置,所有这些操作在单个原子操作中完成。由于这个过程是原子的,生产者和消费者线程不会相互干扰。

## 性能优化与XCHG指令

### 性能分析与监控技巧

使用XCHG指令可以提高多线程程序的性能,因为它允许程序员实现无锁(lock-free)的数据结构。但是,这并不意味着XCHG指令总能带来性能提升。在某些情况下,频繁地使用原子操作可能成为性能瓶颈,因为它增加了处理器之间的同步需求。

为了分析XCHG指令的性能影响,开发者需要使用性能分析工具来监控几个关键指标:

- **上下文切换次数**:由于XCHG指令所涉及的同步机制可能导致处理器时间片的频繁切换,监控这个指标可以帮助确定是否有过多的同步开销。

- **缓存命中率**:频繁的原子操作可能导致缓存不一致,影响缓存命中率,因此监控缓存行为也是重要的。

- **处理器利用率**:监视处理器是否在高负荷下运行,可以帮助理解同步操作是否占用了过多的处理时间。

### 利用XCHG指令提升性能的策略

为了利用XCHG指令提升性能,需要考虑以下策略:

- **减少原子操作的范围**:尽可能缩小需要原子保护的数据区域,以减少同步开销。

- **使用局部数据**:尽可能在每个线程内部维护局部数据的副本,以减少对共享资源的竞争。

- **避免过度同步**:明确地设计数据结构以减少不必要的同步,例如使用无锁的数据结构设计。

- **使用编译器优化**:利用编译器的优化技术,比如循环展开,减少循环中的同步开销。

通过上述策略,可以更有效地利用XCHG指令,提高程序的性能。开发者需要根据具体的使用场景和性能分析结果,选择合适的优化手段。

```c

// 示例代码:优化XCHG指令的使用以减少同步开销

// 在某些情况下,我们可能有多个生产者共享同一个缓冲区,但需要减少XCHG调用的次数

int* buffer = new int[BUFFER_SIZE];

atomic_int in = ATOMIC_VAR_INIT(0);

void* producer_batch(void* arg) {

const int batch_size = 10;

int* batch = new int[batch_size]; // 分配一批数据的空间

// 生成一批数据

for (int i = 0; i < batch_size; ++i) {

batch[i] = produce_item();

}

int pos = 0;

while (pos < batch_size) {

// 批量生产数据到缓冲区,减少XCHG调用次数

int current = atomic_fetch_add(&in, batch_size);

for (int i = 0; i < batch_size && i + current < BUFFER_SIZE; ++i) {

buffer[i + current] = batch[pos++];

}

}

delete[] batch;

}

```

以上代码展示了如何通过批量处理来减少XCHG指令的调用次数,从而减轻线程间的同步压力,并提升性能。

在本章中,我们深入了解了XCHG指令的实践应用,包括它在锁机制中的作用、在并发编程中的使用场景,以及如何通过XCHG指令进行性能优化。通过这些实际案例,可以看到XCHG指令在保证原子性操作的同时,也能够成为提升并发程序性能的强大工具。在接下来的章节中,我们将继续深入探讨XCHG指令在不同编程语言中的实现细节。

# 4. ```

# 第四章:XCHG指令在不同编程语言中的实现

XCHG指令的实现和应用跨越了从底层硬件到高级语言的多个层面,这一章将深入探讨XCHG在不同编程语言中的具体实现和应用案例。

## 4.1 XCHG在底层语言中的实现

### 4.1.1 汇编语言中XCHG指令的直接应用

汇编语言允许程序员直接与硬件交互,提供了对XCHG指令的直接访问。以下是汇编语言中使用XCHG指令的一个基本示例:

```assembly

MOV EAX, 1 ; 将数值1加载到EAX寄存器

MOV EBX, 0 ; 将数值0加载到EBX寄存器

XCHG EAX, EBX ; 交换EAX和EBX的值

```

在汇编中,XCHG指令可以用于交换寄存器或者内存位置的值。由于它是一个原子操作,因此可以用来实现简单的无锁算法。

### 4.1.2 优化编译器如何处理XCHG指令

编译器在处理XCHG指令时可能会应用一些优化策略。例如,它可能会分析代码中的XCHG指令并尝试将其重新排序以减少处理器的停顿时间。编译器的优化策略对程序员来说是透明的,但是了解这些策略可以帮助开发者更好地编写出性能优秀的代码。

```assembly

; 编译器优化前的汇编代码

MOV EAX, [mem1]

XCHG EAX, [mem2]

; 编译器优化后的汇编代码

XCHG [mem1], [mem2]

```

在优化后,编译器直接使用XCHG指令来交换两个内存位置的值,这样做可能会减少操作的延迟。

## 4.2 XCHG在高级语言中的抽象

### 4.2.1 语言级别的原子操作封装

高级语言如C++、Java和C#提供了更高级的抽象,允许开发者在不需要直接编写汇编代码的情况下使用原子操作。例如,在C++中,可以使用`std::atomic`库来实现原子操作:

```cpp

#include <atomic>

std::atomic<int> atomic_value;

void swap(int *a, int *b) {

int temp = *a;

*a = *b;

*b = temp;

}

void atomic_swap() {

int val1 = 10;

int val2 = 20;

swap(&atomic_value, &val1);

swap(&atomic_value, &val2);

}

```

### 4.2.2 标准库与第三方库对原子操作的支持

除了语言自带的库以外,开发者也可以依赖一些第三方库来实现原子操作。这些库往往提供了更多的功能和更高的性能。例如,Intel提供的Threading Building Blocks (TBB)库中就有对原子操作的支持。

```cpp

#include <tbb/atomic.h>

tbb::atomic<int> atomic_value;

void atomic_swap() {

int val1 = 10;

int val2 = 20;

int temp = atomic_value;

atomic_value = val1;

val1 = val2;

val2 = temp;

}

```

## 4.3 案例研究:XCHG指令在实际项目中的应用

### 4.3.1 多线程数据库中的原子操作实例

在多线程数据库系统中,原子操作是实现事务一致性和隔离性的重要机制。例如,在一个支持多线程的键值存储系统中,可能需要使用XCHG指令来安全地更新存储桶中的项。

### 4.3.2 高并发服务器中的锁与同步机制

在高并发服务器设计中,利用XCHG指令实现的锁可以有效地控制资源访问。例如,在构建一个支持大量并发连接的HTTP服务器时,可以使用XCHG实现一个轻量级的锁来保护连接池。

```cpp

std::mutex connection_mutex;

std::atomic<bool> lock;

void acquire_lock() {

while (!lock.exchange(true, std::memory_order_acquire)) {

// 如果锁已被占用,则循环等待

}

}

void release_lock() {

lock.store(false, std::memory_order_release);

}

// 在需要同步的地方使用锁

acquire_lock();

// 保护临界区

release_lock();

```

以上代码中展示了如何使用`std::atomic<bool>`来实现一个简单的互斥锁。需要注意的是,真正的并发系统需要更复杂的同步机制和错误处理策略。

在本章中,我们详细探讨了XCHG指令在不同编程语言和应用层面的实现细节。通过深入理解XCHG指令及其在各层面的抽象,开发者可以更加高效地利用这一强大的硬件特性,来实现高性能和线程安全的应用程序。

```

# 5. XCHG指令的限制与未来展望

XCHG指令是实现原子操作的重要工具,但随着计算需求的不断增长和硬件技术的演进,XCHG指令也面临着一些限制。在本章中,我们将探讨XCHG指令的局限性,分析其在特定架构下的性能差异,并展望同步机制的未来发展方向。

## 5.1 现有技术的局限性

在现代处理器中,XCHG指令依赖于硬件的原子性保证,但这种依赖也带来了局限性。

### 5.1.1 XCHG指令的硬件依赖和限制

XCHG指令通常需要依赖特定的硬件支持,如锁前缀(lock prefix),它通过总线锁定来保证操作的原子性。然而,这种锁定机制在多核处理器中可能会导致性能瓶颈,因为锁定会阻塞其他处理器对该内存位置的访问。此外,在多处理器系统中,XCHG指令的性能会受到总线竞争和缓存一致性协议效率的影响。

```asm

lock xchg reg, mem

```

上述汇编代码展示了使用lock前缀的XCHG指令,它确保了`reg`和`mem`之间的值交换是原子的。但是,lock前缀会引起其他处理器的缓存行失效,增加了总线通信的开销。

### 5.1.2 在特定架构下的性能差异分析

不同的处理器架构对XCHG指令的支持程度和优化方式存在差异。例如,Intel和AMD处理器在处理XCHG指令时采用的内部机制可能不同,导致同一指令在不同处理器上的性能表现各异。此外,随着处理器核心数量的增加,XCHG指令的性能影响会随着上下文切换和缓存一致性的复杂性而变化。

为了分析XCHG指令在不同架构上的性能差异,可以设计基准测试,利用不同品牌和型号的处理器执行一系列的原子操作,并记录操作时间和资源消耗。

## 5.2 未来同步机制的发展趋势

随着技术的进步,同步机制也在不断地发展和改进。未来的研究方向将可能集中在更高效的同步策略和新兴计算模型的同步需求上。

### 5.2.1 混合同步策略的研究方向

混合同步策略旨在结合锁和无锁编程的优点,减少单一同步机制可能带来的性能缺陷。例如,可以在竞争较轻时使用无锁机制,而在竞争激烈时切换到传统的锁机制。这种策略可以提高系统的整体性能和响应速度。

研究混合同步策略时,可以考虑使用性能模拟工具来评估不同策略在不同负载下的效果。通过这种方式,可以确定最佳的同步机制组合,以适应变化的工作负载。

### 5.2.2 量子计算与同步机制的挑战与机遇

量子计算为同步机制带来了新的挑战和机遇。量子位的特殊性质使得传统同步机制不再适用,因此需要开发全新的量子同步技术。量子纠缠和超位置的特性可能允许更高效的同步和通信机制,同时也会引发新的问题,如量子错误校正和量子态保护。

量子计算同步机制的研究仍处于起步阶段,但其前景广阔。同步技术的创新有可能成为量子计算机实用化的关键因素之一。

## 总结

XCHG指令作为原子操作的一种,虽然在当前的多线程和并发编程中扮演着重要角色,但其在硬件依赖和性能瓶颈上存在局限性。未来的研究将致力于解决这些局限性,推动同步机制的发展。通过混合同步策略和适应新兴计算模型的需求,我们可以期待同步机制将随着计算技术的发展而进步,为多线程和并发环境提供更加高效和灵活的解决方案。

# 6. 深入探索XCHG指令的高级主题

随着多核处理器的普及和并行编程的深入应用,XCHG指令作为原子操作的核心之一,在性能优化和并发控制方面展现出了更为复杂的高级用法。本章节将深入探讨硬件事务内存(HTM)的高级应用、非阻塞同步与原子操作的创新应用,以及在实际应用中如何调优XCHG指令。

## 6.1 硬件事务内存的高级应用

现代处理器引入了硬件事务内存(HTM)以支持事务性的内存操作,这为并发编程带来了新的解决方案。HTM极大地简化了锁的使用,可以在不使用传统锁机制的情况下,保证内存操作的原子性。

### 6.1.1 HTM在数据库和存储系统中的应用

数据库系统和存储系统是事务性操作的重灾区。HTM能够有效地减少锁竞争,提升并发读写操作的性能。以数据库为例,事务中的多个内存操作可以通过HTM在一个事务块中完成,大大减少了因锁争用导致的性能损耗。

### 6.1.2 HTM技术的挑战与优化

尽管HTM提供了诸多便利,但在实际应用中也面临着一系列挑战。例如,事务的大小受限、回滚处理的开销,以及无法保证一致性等。因此,对于开发者来说,合理设计事务边界、优化事务大小以及结合软件事务内存(STM)进行混合使用是目前的常见做法。

## 6.2 非阻塞同步与原子操作

非阻塞同步是指在多线程环境中,线程在进行同步操作时不需要阻塞其他线程,从而能够提高系统的吞吐量和响应性。

### 6.2.1 无锁编程的基本概念

无锁编程的核心是利用原子操作来实现线程间的同步,而不是依赖传统的锁。XCHG指令在这里起着至关重要的作用,它能够保证在没有锁的情况下,对共享资源的操作是原子的,从而避免数据竞争。

### 6.2.2 原子操作在无锁编程中的创新应用

无锁编程的典型应用包括无锁队列、无锁哈希表等数据结构的设计。这些结构通过原子操作(如XCHG)来确保操作的原子性,并通过循环来重试失败的操作,从而实现高效的线程间通信和数据共享。

## 6.3 实践中的XCHG指令调优技巧

性能调优是开发高性能应用程序不可或缺的一部分。XCHG指令虽然提供原子操作,但在高负载下仍可能出现性能瓶颈。

### 6.3.1 分析和识别XCHG指令瓶颈

识别XCHG指令的瓶颈首先需要理解应用程序的工作负载。借助性能分析工具,可以观察到XCHG指令在执行时的争用情况。争用高意味着需要优化,可能通过减少XCHG操作的频率或使用其他形式的同步机制来缓解瓶颈。

### 6.3.2 XCHG指令调优案例分享

例如,在一个高并发的订单处理系统中,原始的锁策略导致了XCHG指令的高争用,影响性能。通过引入无锁数据结构和减少对共享资源的依赖,使用本地缓存以及优化事务边界,最终显著提高了系统的处理能力,并降低了延迟。

```markdown

| 应用场景 | 原始性能 | 调优后性能 |

|----------|----------|------------|

| 订单处理吞吐量 | 10,000 TPS | 20,000 TPS |

| 平均响应时间 | 120ms | 60ms |

```

通过对比调优前后性能的变化,我们可以看到性能提升的效果。这样的调优案例不仅展示了XCHG指令在实际应用中的潜力,也体现了深入理解和优化的重要性。

以上章节内容仅是XCHG指令高级主题探讨的一部分,更多的实践和案例研究可以帮助我们进一步理解并优化使用XCHG指令的复杂场景。

0

0