性能监控专家:实时追踪与解决Layout Dependent Effect的方法

发布时间: 2024-12-26 00:21:43 阅读量: 5 订阅数: 8

Layout Dependent Effect.pdf

# 摘要

性能监控在集成电路设计与制造中扮演着重要角色,而Layout Dependent Effect(LDE)作为影响电路性能的关键因素之一,其监控与控制显得尤为关键。本文旨在阐述LDE的基本概念、理论基础及其对电路性能的影响,同时介绍了性能监控中LDE的检测技术和实时追踪方法。通过对LDE检测方法和工具的讨论,本文揭示了LDE检测实践应用的重要性。最后,文章展望了LDE监控技术的未来发展方向,包括人工智能与机器学习的应用,以及集成电路设计领域的新技术和行业挑战。本文的目标是为工程师和研究者提供全面的LDE监控知识,以优化工艺设计,提升芯片可靠性。

# 关键字

性能监控;Layout Dependent Effect;电路性能;检测技术;实时追踪;集成电路设计

参考资源链接:[深入理解LDE:模拟电路中的布局依赖效应与STI/WPE详解](https://wenku.csdn.net/doc/4x9og575iz?spm=1055.2635.3001.10343)

# 1. 性能监控的基本概念

性能监控是现代IT和电子工程领域中不可或缺的一环,它涉及到对系统性能的实时跟踪、评估以及优化。基本概念涵盖了性能监控的定义、目的和实施的重要性。首先,性能监控可以视为一套方法论,它通过采集、分析和解释性能数据,帮助工程师理解系统当前的工作状态,并为优化系统性能提供数据支持。监控的目的在于确保系统稳定运行,预防性能瓶颈和故障的发生,从而提升系统的可靠性和效率。

性能监控不仅仅局限于硬件性能的测量,它还涉及到软件运行状况的追踪。此外,监控的实施需要综合考虑实时性和准确性两个方面。实时性能监控能够快速识别系统运行中的问题,而准确的性能数据则是判断和解决问题的依据。在当前技术高速发展的背景下,性能监控已成为企业和组织确保其技术资产持续稳定运行的关键手段。接下来的章节将深入探讨性能监控在具体技术领域的应用,如集成电路设计中的Layout Dependent Effect (LDE) 监控。

# 2. Layout Dependent Effect的理论基础

### 2.1 LDE的定义与分类

#### 2.1.1 什么是LDE?

Layout Dependent Effect(LDE)指的是在集成电路(IC)制造过程中,由于器件布局的不同,导致相同结构的器件在不同区域表现出不同的电气性能的现象。LDE可以显著影响晶体管的阈值电压、亚阈值摆幅以及载流子迁移率等关键参数,进而影响电路的时序、功耗以及可靠性等性能指标。

LDE的产生源自于制造过程中的微缩效应,随着工艺技术的进步,特征尺寸不断缩小,使得器件之间的相互影响变得更加显著。例如,平面布局中紧邻的多晶硅线、金属线或隔离区域的应力分布,可能导致晶体管沟道区域的应力状态改变,从而引起电气参数的偏差。

#### 2.1.2 LDE的主要类型

LDE主要分为以下几类:

1. **STI Stress-Induced LDE (STI-LDE)**:由于应力松弛结构(Shallow Trench Isolation, STI)引起的局部区域应力,从而对器件性能造成影响。

2. **Dummy Fill Induced LDE (DF-LDE)**:在布局中为了确保工艺一致性而添加的虚拟填充物(dummy fill)会对周边器件产生影响。

3. **Well Proximity Effect (WPE)**:由于晶体管与隔离区(well)之间的距离不同,导致器件特性的变化。

### 2.2 LDE的产生原理

#### 2.2.1 物理层面的分析

在物理层面,LDE的产生可以通过分析晶体管周围的物理应力来理解。当晶体管被周围材料包围时,如隔离结构STI、金属线和接触孔等,它们在制造过程中由于材料的热膨胀系数不匹配,会在晶体管沟道区域产生额外的应力。这种应力在不同的布局条件下,会呈现不同的分布,导致沟道区域的电子迁移率发生变化,进而影响器件性能。

#### 2.2.2 电学层面的分析

电学层面上,LDE会导致器件的阈值电压出现偏差。当晶体管沟道中的应力改变时,影响了载流子的迁移率和浓度,最终改变晶体管的开启电压。例如,应力可能使得P型MOSFET的阈值电压增加,从而降低了器件的速度,这在时序关键路径上尤为明显。

### 2.3 LDE对电路性能的影响

#### 2.3.1 信号完整性

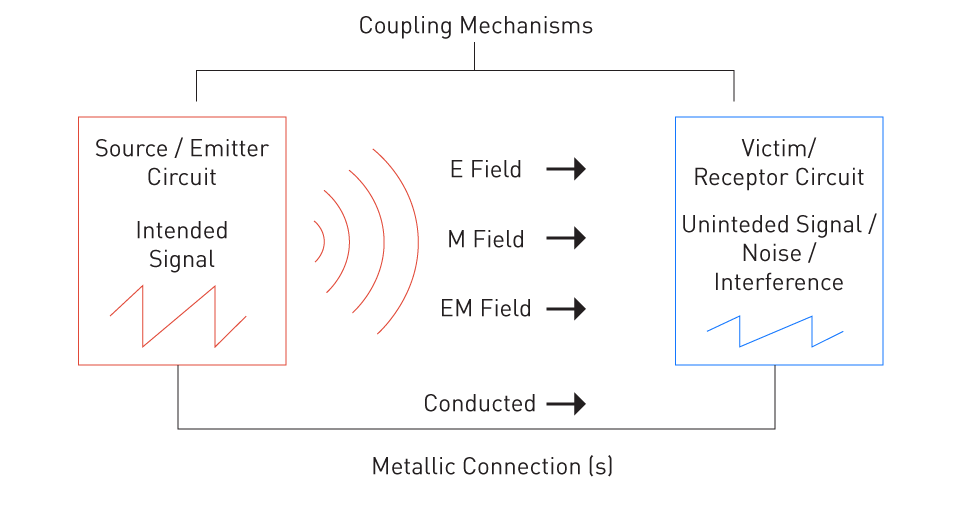

在高速数字电路设计中,信号完整性至关重要。LDE可以导致信号在传输路径中出现延迟、反射以及串扰等问题,特别是在高性能计算、高速接口等应用中,信号完整性问题会直接导致系统性能下降。

#### 2.3.2 电源完整性

电源完整性是指电路板上电源网络能否为器件提供稳定的电源。由于LDE的影响,电源网络可能在不同区域表现出不同的阻抗特性,从而在器件的电源脚上产生噪声,影响器件性能和可靠性。

#### 2.3.3 芯片可靠性

LDE影响的不仅是信号和电源的完整性,还有芯片的整体可靠性。器件性能的偏差会导致温度升高、过电压等问题,长期作用可能会引起器件退化甚至失效,进而影响整个芯片的寿命。

由于LDE对于电路性能的重大影响,设计师必须在物理设计阶段就采取有效的预防和控制措施,以确保电路设计的成功。这些措施包括精心设计的布局规划、使用LDE感知的优化流程,以及在生产前进行彻底的LDE分析。

在后续的章节中,我们将深入探讨LDE的检测技术以及如何在性能监控中实时追踪和应对LDE问题。

# 3. 性能监控中的LDE检测技术

## 3.1 常用的LDE检测方法

### 3.1.1 静态分析技术

静态分析技术是指在不运行电路或程序的情况下,对电路设计进行检查以发现潜在的Layout Dependent Effect(LDE)问题的方法。该技术适用于早期设计阶段,可以快速识别出那些可能会在布局过程中产生负面影响的设计模式。静

0

0