消费电子中的叠层封装创新:如何评估与选择最佳技术

发布时间: 2024-12-27 03:50:59 阅读量: 3 订阅数: 6

PCB技术中的电子封装技术的新进展

# 摘要

叠层封装技术作为现代电子制造的关键工艺,正受到广泛关注。本文首先对叠层封装技术的定义、发展历程及其理论基础进行概述,随后详细介绍其关键制造流程和材料选择,并探讨了性能优势与面临的挑战。本文还介绍了一系列评估叠层封装技术的方法,包括性能指标的设定、成本效益分析以及可靠性与质量控制。在选择叠层封装技术时,本文提出了一个详细的决策过程,涵盖应用需求分析、技术可行性评估以及风险管理与未来发展预测。最后,本文分析了叠层封装技术在消费电子产品中的创新应用,并对其未来发展趋势进行了展望。

# 关键字

叠层封装技术;理论基础;制造流程;性能优势;评估方法;技术创新应用

参考资源链接:[Amkor的下一代PoP技术:TMV®引领封装创新](https://wenku.csdn.net/doc/5jfffkryan?spm=1055.2635.3001.10343)

# 1. 叠层封装技术概述

## 1.1 叠层封装技术简介

叠层封装技术是一种先进的封装方法,其核心在于将多个电路板层叠并紧密封装在一起,以实现更高的组件集成度和更好的性能表现。这一技术极大地推动了电子产品的微型化和功能多样化,对提高电子设备的运算速度与存储能力贡献巨大。

## 1.2 技术背景与发展

随着消费电子产品对更高性能与更小尺寸的需求不断增加,传统的封装技术逐渐不能满足市场的需求,叠层封装技术应运而生。从最初的多芯片模块封装,到现今的系统级封装(System-in-Package, SiP),叠层封装经历了快速的技术发展和创新。

## 1.3 技术应用现状

当前,叠层封装技术广泛应用于高性能计算、移动通信、消费类电子以及汽车电子等领域。由于其能够将复杂的电路设计封装成体积更小、功能更强的模块,因此叠层封装技术被视为现代电子制造中的关键技术之一。

叠层封装技术的进步不仅推动了芯片设计和制造的革新,也为实现物联网、智能穿戴设备等新兴技术提供了可能。在后续章节中,我们将深入探讨叠层封装的理论基础、评估方法以及应用案例,揭示其在现代电子设计中的重要性和未来潜力。

# 2. 叠层封装的理论基础

## 2.1 叠层封装的定义与发展历程

### 2.1.1 叠层封装的基本概念

叠层封装(3D Packaging),是一种先进的集成电路封装技术,其核心在于将多个半导体芯片垂直堆叠,利用金属互连实现高密度封装,提供更高的性能和更小的体积。与传统的二维平面封装技术相比,叠层封装能显著提升数据传输速率,降低功耗,同时减小芯片的物理尺寸。

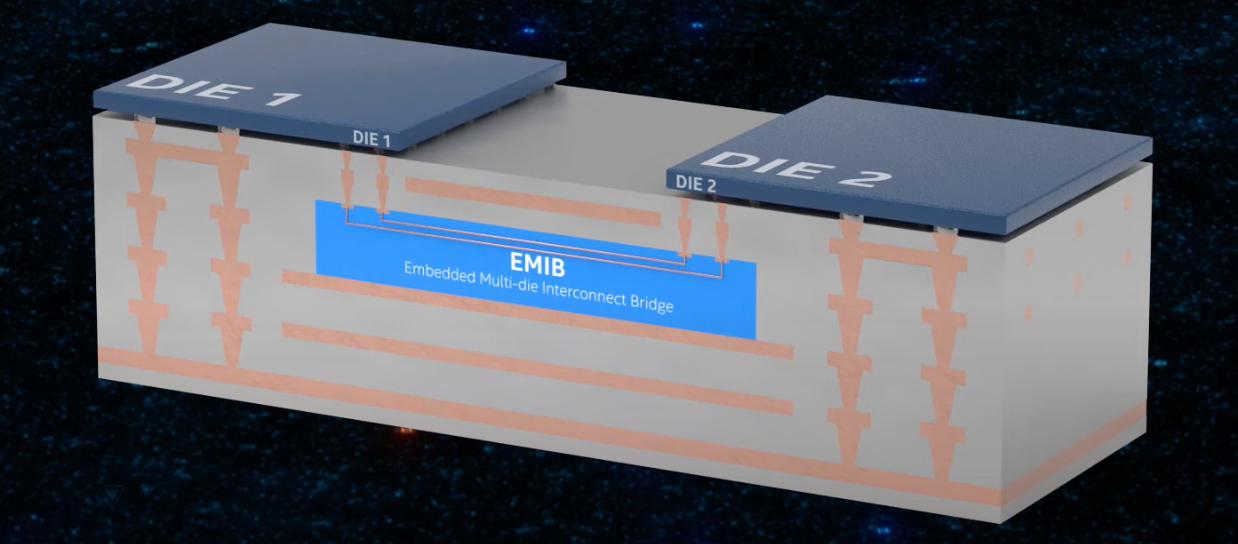

从技术角度,叠层封装包括了多种实现方式,例如硅通孔(Through-Silicon Via, TSV)技术、芯片堆叠和封装等。在TSV技术中,硅片上钻出小孔,通过这些小孔进行芯片之间的垂直互连。这不仅能实现更高的I/O密度,还能够缩短信号传输路径,提供更好的性能。

### 2.1.2 主要的技术演进和里程碑

叠层封装技术的演进始于上世纪90年代,起初主要应用于存储设备。随着技术的成熟和对高性能计算需求的增长,叠层封装逐渐扩展到逻辑设备和其他高性能应用领域。

在2000年代中期,随着芯片制造技术的不断进步,TSV技术开始得到广泛研究。2010年后,随着工艺的改进和成本的降低,叠层封装开始实现商业化。一些著名的芯片制造商如英特尔、三星和台积电开始在其产品中集成3D封装技术。这标志着叠层封装从实验室阶段正式走向市场。

## 2.2 关键制造流程和材料

### 2.2.1 制造工艺简介

叠层封装的制造工艺涉及多个复杂的步骤,主要可以分为以下阶段:晶圆制造、晶圆测试与划分、TSV制造、晶圆键合、芯片切割与封装、最终测试与检验。

首先在晶圆上制造出TSV孔,接下来在孔中填充金属,形成垂直的电气连接。随后,经过测试和切割的多个芯片被精确地堆叠和键合在一起。最后,封装完成的芯片组件还要经过一系列的测试,以确保其性能符合标准。

### 2.2.2 关键材料的作用和选择

在叠层封装中,选择合适的材料至关重要。对于TSV技术,金属填充材料的选择尤为关键。常用的材料包括铜(Cu)和钨(W),铜由于其高电导率和良好的热导率而被广泛使用。同时,绝缘层材料和粘合剂等也需要具有优异的电绝缘性能和热稳定性。

在选择材料时,工程师需权衡成本、性能以及材料间的兼容性。例如,在选择粘合剂时,不仅要考虑其粘合能力,还要考虑其在高温下的稳定性,以确保封装过程中芯片不受损害。

## 2.3 叠层封装的性能优势与挑战

### 2.3.1 性能提升的理论分析

叠层封装技术之所以受到青睐,是因为其能显著提升芯片性能。从理论上讲,通过垂直堆叠,能够缩短芯片间的互连距离,从而减少信号传输延迟。此外,这种技术可以提升I/O密度,减少整体的能耗,提供更高的处理能力和更大的存储空间。

在集成电路中,信号传输延迟是限制性能的关键因素之一。通过TSV技术,能够实现芯片内部的高速数据传输,这对于提高系统运行速度和效率至关重要。此外,堆叠技术允许芯片设计者打破传统的面积限制,实现更为紧凑的设计。

### 2.3.2 面临的技术挑战和解决方案

尽管叠层封装技术优势明显,但在其发展过程中也面临众多技术挑战。例如,TSV孔的制造过程中可能会产生应力,这会影响芯片的可靠性。此外,随着堆叠层数的增加,热量管理成为一大难题,高密度封装产生的热量如果不加以有效控制,可能会导致芯片性能下降甚至损坏。

为解决这些挑战,工程师们不断研发新材料和新技术。比如,采用具有更好热导性的材料来改善散热问题,或者使用更先进的热模拟软件预测并优化热管理。此外,改进封装设计,比如引入三维热模型,可以更有效地分析和解决热量问题。这些解决方案对于保证叠层封装技术的可靠性和稳定性至关重要。

# 3. 叠层封装技术的评估方法

### 3.1 评估标准与测试流程

叠层封装技术的评估是一项复杂而关键的任务,它涉及多个性能指标和测试程序。要确保技术的可靠性和有效性,必须首先建立关键性能指标(KPI),然后执行标准

0

0