STM32引脚布线优化指南:PCB设计中的引脚布局黄金技巧

发布时间: 2024-12-25 11:23:45 阅读量: 9 订阅数: 15

STM32设计的原理图+PCB文件资料.rar

# 摘要

本文为STM32引脚布线优化指南,详述了STM32引脚的功能特性、PCB设计中的引脚布局原则以及优化实践。针对电源与地线、信号引脚和调试测试引脚的布局优化提供了具体策略。同时,介绍了高级PCB布线技术的应用,包括信号完整性分析、热管理及遵循工业标准。案例研究与最佳实践章节提供了实际应用中的布线优化案例分析,以及布线优化的检查清单、工具与资源。本指南旨在帮助工程师在设计和生产中实施有效的布线策略,以确保电路板性能和可靠性。

# 关键字

STM32引脚;PCB设计;信号完整性;热管理;布局优化;工业标准

参考资源链接:[STM32各个引脚功能Excel表格整理](https://wenku.csdn.net/doc/6412b5ffbe7fbd1778d45242?spm=1055.2635.3001.10343)

# 1. STM32引脚布线优化指南概述

## 简介

STM32微控制器因其性能和灵活性在嵌入式系统设计中广泛使用。然而,为了充分利用STM32的性能,必须对其进行正确的布线设计。在本章中,我们将介绍引脚布线优化的重要性,以及它如何影响系统性能和稳定性。

## 布线优化的必要性

布线优化不仅影响系统的电气性能,还与信号完整性、EMC兼容性、散热和热管理密切相关。一个良好的布线策略可以确保系统长期稳定运行并减少故障的可能性。

## 本章结构

在接下来的章节中,我们将从STM32引脚的功能和特性开始,深入探讨PCB设计中引脚布局原则。最后,通过实际案例研究,展示如何应用最佳实践来优化STM32的引脚布线。

# 2. STM32引脚功能与特性

### 2.1 STM32引脚的功能分类

STM32微控制器拥有丰富的引脚,这些引脚按照功能不同,可以进行分类。了解这些功能分类是进行高效布线和优化的前提。

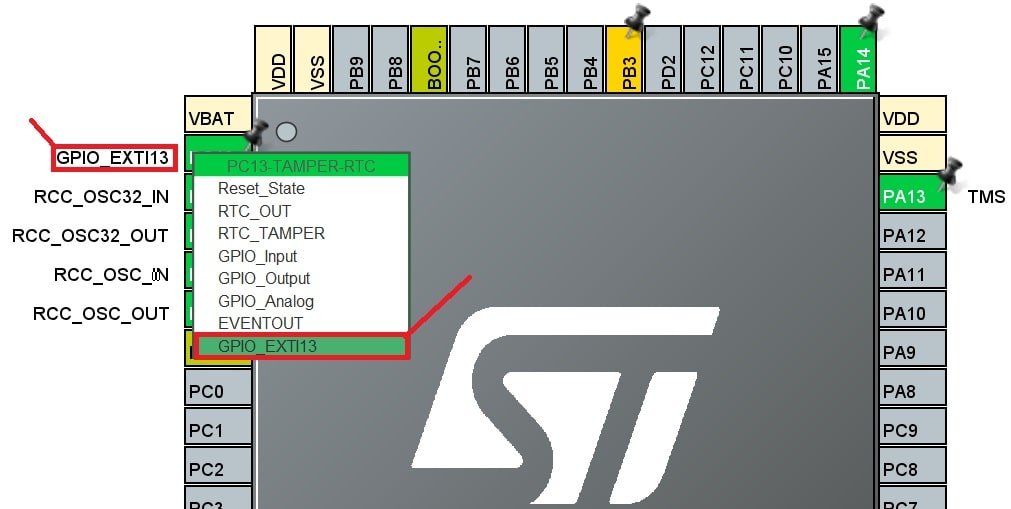

#### 2.1.1 输入/输出引脚

STM32的输入/输出引脚,通常被称为通用输入输出(GPIO)引脚,用于与外部电路连接,进行信号的输入和输出。GPIO引脚是STM32微控制器中应用最广泛的引脚类型。

```c

// GPIO初始化代码示例

void GPIO_Configuration(void) {

GPIO_InitTypeDef GPIO_InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE); // 使能GPIOA时钟

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0; // 选择要配置的GPIO引脚

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; // 推挽输出

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; // IO口速度为50MHz

GPIO_Init(GPIOA, &GPIO_InitStructure); // 根据设定参数初始化GPIOA0

}

```

在上述代码中,我们配置了一个GPIO引脚为推挽输出模式,速度为50MHz。每步的含义已经在代码注释中给出,但是在实际应用中,每一种配置都应该基于硬件设计的特定需要。

#### 2.1.2 电源与地线引脚

STM32微控制器的电源引脚用于提供微控制器所需的电源电压,而地线引脚则是与地线连接的点。电源引脚的设计要考虑到电流的供应能力和稳定性,而地线的设计则需要最小化地线回路的长度以降低干扰。

#### 2.1.3 模拟与数字引脚

模拟引脚通常用于连接模拟传感器或执行模拟信号处理。数字引脚用于处理数字信号。在布局上需要考虑模拟信号的隔离,避免数字信号的噪声干扰到模拟信号。

### 2.2 STM32引脚电气特性

对STM32引脚的电气特性有所了解,是优化设计的重要基础。引脚的电气特性包括电压电流规格、输入输出电平标准以及ESD保护等。

#### 2.2.1 电压与电流规格

STM32微控制器每个引脚的电流输出能力、输入电压范围和阈值都是根据其电气特性表来确定的。

| 引脚类型 | 最大电流输出能力 | 输入电压范围 | I/O逻辑高/低阈值 |

|----------|-----------------|--------------|------------------|

| GPIO | 8mA (标准) | 0-3.6V | Vih >= 2.0V, Vil <= 0.8V |

| ADC | 1mA (最大) | 0-3.6V | - |

表格中的数据表明,对于典型的GPIO引脚,其最大电流输出为8mA,且必须工作在0到3.6伏特的电压范围内。设计电路时,必须保证线路驱动能力与引脚规格相匹配,以避免损坏微控制器。

#### 2.2.2 输入输出电平标准

STM32微控制器遵循TTL电平标准,即输入逻辑高电平为2V以上,逻辑低电平为0.8V以下。

#### 2.2.3 ESD保护和电气应力

STM32微控制器的引脚设计考虑了静电放电(ESD)保护。设计布线时,应避免引脚承受过高的电压或电流冲击,可能需要外部的ESD保护元件。

### 2.3 引脚特性表格与代码解析

在进行布线设计时,对STM32引脚特性的深入了解是不可忽视的。利用表格和代码,可以实现对这些特性的有效管理与应用。

```markdown

| 引脚名称 | 功能描述 | 电气特性 | 备注 |

|----------|----------|----------|------|

| PA0 | GPIO | I/O标准 | 推挽输出,50MHz |

| VCC | 电源 | 3.3V | 最大供电电流80mA |

| GND | 地线 | 0V | 接地稳定参考点 |

```

在上面的表格中,我们对几个引脚的功能、电气特性进行了描述,并附上了具体的参数。在实际的PCB设计过程中,需要根据表格提供的信息对引脚进行布局和布线设计。

以上内容为第二章关于STM32引脚功能与特性部分的深入解析。在下一部分,我们将继续探讨在PCB设计中的引脚布局原则,以及如何应用这些原则实现有效的布线策略。

# 3. PCB设计中的引脚布局原则

在设计高性能PCB时,引脚布局原则是确保电路板成功的关键因素之一。良好的布局不仅关系到信号完整性、电磁兼容性(EMC),还涉及散热和布线效率。本章节将详细探讨在PCB设计中应用的引脚布局原则,以确保设计的可靠性和性能。

## 3.1 布线策略与信号完整性

### 3.1.1 信号线的布局顺序

信号线布局顺序是指在PCB设计过程中对信号路径的优先级排序,这直接影响到信号的完整性和系统的稳定运行。一般来说,应该遵循以下步骤:

1. 首先布局时钟信号线,因为它们对信号完整性影响最大。时钟线的布局应该尽量短且直接。

2. 其次是高速信号线,包括差分信号对,这些信号对的长度和走线路径应当一致,以保持信号相位的一致性。

3. 然后是模拟信号线,这类信号对噪声较为敏感,应该远离数字信号区域,并采取适当隔离措施。

4. 最后是低速和低频信号线,包括电源和地线。

在处理高速信号时,应考虑信号的返回路径,确保信号环路的面积最小化,以降低电磁干扰(EMI)和提高信号质量。

### 3.1.2 阻抗匹配与信号完整性

阻抗匹配是信号完整性的另一个重要方面,主要涉及到高速信号的传输。为了避免信号的反射和振铃,需要保证传输线的特性阻抗与负载阻抗相匹配。计算特性阻抗的公式如下:

```

Z_0 = 138 / sqrt(ε_r + 1) * log((2h + 0.8w) / w)

```

其中,`Z_0` 是特性阻抗,`ε_r` 是介质的相对介电常数,`h` 是介质层厚度,`w` 是线宽。

在实际设计中,通过调整PCB板层厚度、线宽、介电常数等参数,可以达到期望的特性阻抗值。使用阻抗计算器工具可以帮助快速计算出参数值。

0

0