【比特流文件全解读】:精通Xilinx FPGA编程与配置

发布时间: 2024-12-20 14:53:13 阅读量: 7 订阅数: 6

# 摘要

本文主要探讨了Xilinx FPGA的编程基础、比特流文件的结构与解析、编程与配置实践、高级配置技巧以及FPGA的未来展望与研究方向。首先,介绍了FPGA编程基础和比特流文件的产生、作用以及其与FPGA配置的关系。其次,详细解析了比特流文件的内容,包括配置帧、头信息与校验机制,以及用户数据区域的解读。再次,通过具体的FPGA编程与配置实践,详细阐述了编程步骤、比特流文件的下载与配置以及实际案例分析。此外,本文还探讨了FPGA高级配置技巧,包括比特流文件的优化、动态部分配置(PPC)以及比特流文件的安全性。最后,本文展望了FPGA在新兴技术中的应用,FPGA编程模型的演变以及未来的研究挑战与趋势。

# 关键字

FPGA编程;比特流文件;配置帧;动态部分配置;高级综合;可重构计算

参考资源链接:[Xilinx FPGA实现DisplayPort接口设计与开发教程](https://wenku.csdn.net/doc/4cykz40wom?spm=1055.2635.3001.10343)

# 1. Xilinx FPGA编程基础

## 1.1 FPGA的基本概念

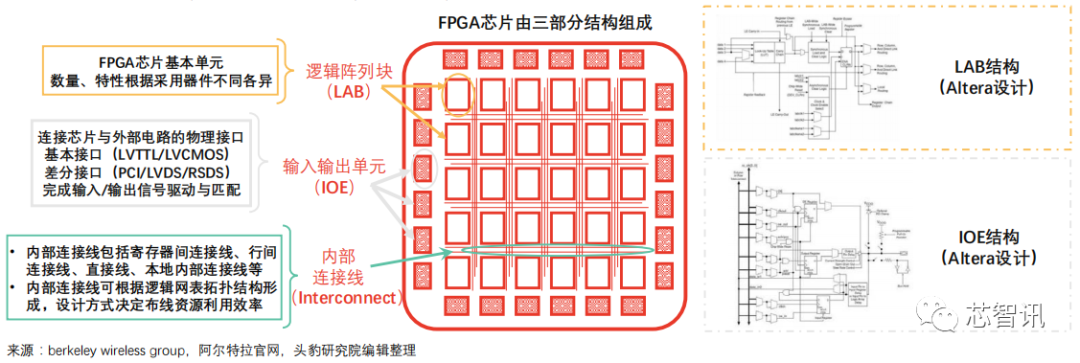

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可以通过编程实现用户自定义逻辑功能的集成电路。它由可编程逻辑单元、可编程互连和可编程输入/输出组成。与传统的ASIC(Application Specific Integrated Circuit,应用特定集成电路)相比,FPGA在研发和生产中具有更高的灵活性和更低的风险,尤其是在原型设计、小批量生产和需要快速适应市场变化的场合。

## 1.2 FPGA编程语言

FPGA的编程主要依赖于硬件描述语言(HDL),主要使用的有VHDL(VHSIC Hardware Description Language,超高速集成电路硬件描述语言)和Verilog HDL。这些语言允许设计者通过文本描述来定义数字电路的行为和结构。在Xilinx FPGA中,还引入了高层次综合(HLS)工具,如Vivado HLS,使得C、C++等高级语言编写的算法能够被转换为硬件描述语言,再映射到FPGA硬件上。

## 1.3 设计与实现流程概述

Xilinx FPGA的设计与实现流程通常包括设计输入、功能仿真、综合、实现、静态时序分析和配置下载等步骤。设计者首先通过HDL或其他设计输入工具定义电路功能,然后利用仿真工具验证设计的正确性。接下来,综合过程将HDL代码转换为FPGA内部可实现的逻辑元素。之后的实现步骤包括布局(Place)和布线(Route),这一步骤生成的比特流文件(Bitstream)用于FPGA的配置和编程。最后,设计师需要将生成的比特流文件下载到FPGA中,并进行实际硬件上的测试。

# 2. 比特流文件的结构与解析

## 2.1 比特流文件概述

### 2.1.1 比特流文件的产生与作用

比特流文件是FPGA编程中一个至关重要的环节,它是由FPGA开发工具(如Xilinx的Vivado或ISE)生成的一种二进制文件,包含了将设计实现到FPGA上的所有必要信息。这个文件中的数据表示FPGA内部逻辑元件的具体配置和连接,即逻辑元件的输入输出是否连接、连接到哪以及如何设置逻辑元件的工作模式。

比特流文件的产生主要在FPGA开发流程的最后阶段,即实现(Implementation)阶段,包括布局(Placement)与布线(Routing)。逻辑综合后的网表文件会通过实现工具进行处理,完成将设计映射到FPGA硬件资源的过程。生成的比特流文件中,每一位的数据代表着一个逻辑元件的状态,这就是比特流名字的由来。

比特流文件的作用不仅限于静态配置FPGA,它还可以用于动态配置,如动态部分配置(PPC)技术,能够实现部分重配置而无需停止整个FPGA的运行,使得FPGA在运行时仍能保持高灵活性和可编程性。

### 2.1.2 比特流文件与FPGA配置的关系

FPGA配置指的是将比特流文件中的数据下载到FPGA内部的配置寄存器中的过程,这个过程是FPGA从上电初始化到开始执行逻辑功能的必经之路。配置数据必须按正确顺序和格式写入FPGA的配置存储单元中,以确保每个逻辑元件和互连资源被正确设置。

比特流文件的结构设计得非常紧密和高效,以便快速地在FPGA上进行配置。配置时,比特流文件通常通过JTAG接口或其他专用配置接口传输到FPGA内部。一旦配置完成,FPGA便可以根据其中的逻辑和互连设置执行预定功能。

比特流文件与FPGA配置的关系,就如同计算机系统中操作系统的镜像文件与启动加载过程的关系一样,是将设计理论化为实际可操作硬件的桥梁。正确配置的比特流文件能够确保FPGA稳定地工作在预期的状态下,执行设计时指定的逻辑任务。

## 2.2 比特流文件内容解析

### 2.2.1 配置帧与帧数据结构

比特流文件可被看作是一系列配置帧的集合,每一个配置帧都是一个数据块,包含了配置FPGA的特定部分所需的信息。配置帧通常有固定的大小,并且按照一定顺序组织。每个帧包括帧头信息、实际配置数据以及校验信息,确保数据的完整性和正确性。

例如,一个典型的FPGA配置帧结构包含帧类型标识(区分是数据帧还是命令帧)、帧序列号(用于顺序控制)、以及帧数据(包含具体配置信息)。每一帧完成后通常会跟随一个校验和,用于在配置过程中检查数据的正确性。

### 2.2.2 头信息与校验机制

比特流文件的开始部分通常包含头信息,它提供了关于比特流文件的基本信息,如目标FPGA的型号、生产厂商、版本信息等。此外,头信息中也可能包括有关比特流文件生成环境的信息,如生成该比特流文件的FPGA开发工具版本、配置选项等。

校验机制是比特流文件的关键部分,以确保在配置过程中数据的完整性和准确性。通常采用CRC(循环冗余校验)作为校验方法,它能检测出数据在传输过程中发生的大多数错误。当配置完成时,FPGA内部逻辑会计算CRC值并与帧内提供的校验值进行比较,若不匹配,则说明配置过程中出现了错误,FPGA将不会进入正常工作模式。

### 2.2.3 用户数据区域的解读

用户数据区域是比特流文件中最主要的部分,它包含了实现特定逻辑功能所需的配置数据。这部分数据通常包括查找表(LUTs)的值、寄存器初始化值、以及逻辑块的配置参数等。

对于设计者来说,了解如何解读用户数据区域的内容有助于进行设计调试和优化。这通常需要对FPGA内部结构和配置方式有深入的了解。在某些高级FPGA工具中,可能会提供辅助工具或可视化界面来帮助设计者解读这部分内容。

具体来说,用户数据区域可以被进一步细分为不同的配置区块,每个区块对应FPGA中的一个特定资源区域。设计者可以识别出每个区块对应的FPGA物理资源,并根据设计逻辑推断出对应的配置值。这样的分析工作虽然复杂,但对于深入理解FPGA配置和进行故障排除是非常有帮助的。

## 2.3 比特流文件的生成工具

### 2.3.1 Vivado生成比特流的过程

Vivado是Xilinx公司推出的一款集成开发环境(IDE),用于设计、实现和验证基于Xilinx的FPGA产品。Vivado提供了从HDL代码输入到比特流文件输出的完整流程,包括逻辑综合、实现、布局、布线和生成比特流。

生成比特流的基本步骤如下:

1. HDL代码输入,包括Verilog或VHDL。

2. 通过逻辑综合将HDL代码转

0

0