组合逻辑电路的功耗分析与优化:权威指南

发布时间: 2024-12-25 01:37:38 阅读量: 29 订阅数: 15

电子技术基础第三章 组合逻辑电路的分析和设计数字部分共64

# 摘要

组合逻辑电路在现代电子系统中广泛应用,其功耗管理对系统性能及能效具有重要影响。本文首先介绍了组合逻辑电路的基础知识及功耗概念,然后深入探讨了静态功耗、动态功耗和短路功耗的来源、影响因素及其优化策略。接着,本文详细分析了传统与现代功耗分析方法和工具,并探讨了软硬件协同分析的优势。第四章提出了低功耗设计的原则和方法,并讨论了逻辑优化及物理设计对功耗的影响。第五章通过实际应用案例,如移动设备和高性能计算中的功耗管理,展示了优化策略的实际效果。最后,本文展望了新材料、新工艺以及人工智能技术在组合逻辑电路功耗优化中的未来趋势和研究方向。

# 关键字

组合逻辑电路;功耗管理;静态功耗;动态功耗;短路功耗;低功耗设计;逻辑优化;物理设计;人工智能

参考资源链接:[数字集成电路:伪NMOS逻辑设计与性能分析](https://wenku.csdn.net/doc/5bgpq0omq7?spm=1055.2635.3001.10343)

# 1. 组合逻辑电路基础与功耗概念

在数字逻辑设计中,组合逻辑电路(Combinational Logic Circuits)是一类电路,其输出仅取决于当前输入的状态,不依赖于历史输入。为了有效地设计组合逻辑电路,必须理解其基本构成与功耗概念。

## 1.1 组合逻辑电路基础

组合逻辑电路由门电路组成,这些门电路执行基本的逻辑操作,如AND、OR、NOT等。在设计时,需要考虑电路的复杂性、速度与面积效率。随着集成度的增加,门电路之间的连线成为影响电路性能和功耗的关键因素。

## 1.2 功耗概念

功耗(Power Consumption)是电子设备在运作时消耗的电能。对于组合逻辑电路而言,功耗主要由静态功耗和动态功耗两部分组成。静态功耗产生于电路在没有切换时的漏电流,而动态功耗则与电路的切换频率和负载电容有关。

```mermaid

flowchart LR

A[组合逻辑电路] --> B[静态功耗]

A --> C[动态功耗]

B -->|机理| D[漏电流]

C -->|计算公式| E[频率 x 负载电容 x (Vdd^2)]

```

功耗分析是评估电路性能的重要组成部分,因为它直接影响着电路的能效比和发热问题。理解组合逻辑电路的功耗来源,有助于设计更高效、低耗的电子系统。

# 2. 功耗来源与理论分析

功耗是电路设计和运行中的一个关键因素,尤其对于移动设备、高性能计算等领域至关重要。组合逻辑电路作为数字电路设计的基础,其功耗分析对于优化电路性能、延长电池寿命等方面具有重要意义。本章将深入探讨组合逻辑电路的功耗来源,并进行理论分析。

### 2.1 组合逻辑电路的静态功耗

#### 2.1.1 静态功耗的机理和影响因素

静态功耗主要发生在电路无开关活动时,是由于晶体管漏电流导致的。随着集成电路向更小的尺寸发展,晶体管的阈值电压不断降低,使得漏电流成为不可忽视的因素。

- **漏电流的形成**:由于晶体管的亚阈值导电、栅介质漏电和结漏电等现象,即使在关闭状态下,晶体管也会有一定的电流流动。

- **影响因素**:晶体管的尺寸、阈值电压、工作温度、电源电压等都会影响漏电流大小。

```mermaid

graph TD

A[晶体管开启] -->|低阈值电压| B[漏电流增大]

C[晶体管关闭] -->|高阈值电压| D[漏电流减小]

E[温度上升] -->|载流子增加| B

F[电源电压降低] -->|漏电流下降| D

```

#### 2.1.2 静态功耗的测量方法

测量静态功耗通常通过关闭晶体管的开关活动,观察电路的电流消耗来进行。

- **直接测量法**:使用精密电流表直接测量电路在无开关活动时的电流值。

- **间接计算法**:根据晶体管的尺寸、阈值电压等参数,使用相应的模型公式来计算预期的静态功耗。

### 2.2 组合逻辑电路的动态功耗

#### 2.2.1 动态功耗的原理和计算公式

动态功耗是电路在开关状态变化时,由于电容充放电而产生的功耗。其计算公式通常表示为:

\[ P_{dynamic} = \alpha \cdot C \cdot V_{DD}^2 \cdot f \]

其中,\( P_{dynamic} \) 是动态功耗,\( \alpha \) 是活动因子(表示电路中发生开关活动的比例),\( C \) 是负载电容,\( V_{DD} \) 是电源电压,\( f \) 是电路频率。

- **活动因子**:影响动态功耗的大小,活动因子越大,动态功耗越高。

- **电源电压**:对动态功耗有二次方的影响,降低电源电压是降低动态功耗的有效方式之一。

#### 2.2.2 动态功耗的影响因素及优化策略

影响动态功耗的因素包括活动因子、电源电压、电路频率等。优化策略包括:

- **电源电压管理**:降低电源电压可以有效减少动态功耗,但这需在保证电路性能的前提下进行。

- **频率管理**:通过降低电路的工作频率,可以减少电容的充放电次数,从而降低动态功耗。

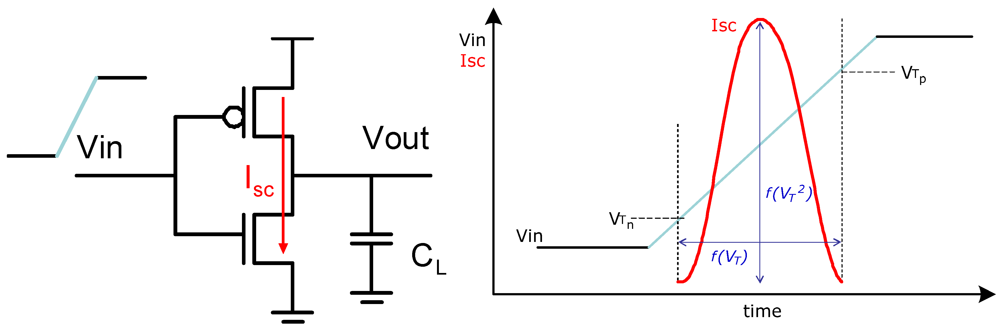

### 2.3 组合逻辑电路的短路功耗

#### 2.3.1 短路电流的产生原因

短路电流发生在组合逻辑电路的逻辑门中,当逻辑门的输入从高电平变为低电平,或者相反时,输出端的MOSFET晶体管可能会在短时间内同时导通,造成直接从电源到地的短路电流。

- **产生机理**:由CMOS逻辑门的N-MOS和P-MOS晶体管同时导通造成。

- **影响因素**:输入信号的切换速度和逻辑门的大小都对短路电流有影响。

```mermaid

flowchart LR

A[输入信号] -->|

```

0

0