【SkyWater PDK与FPGA:无缝集成秘籍】:协同工作无界限

发布时间: 2025-01-10 11:05:22 阅读量: 30 订阅数: 21

skywater-pdk:开源Craft.io设计套件,可与SkyWater Technology Foundry的130nm节点一起使用

# 摘要

随着集成电路设计复杂性的提升,SkyWater PDK与FPGA的集成成为推动电子行业创新的重要力量。本文首先介绍了SkyWater PDK及其与FPGA集成的理论和技术背景,接着详细探讨了集成工具和环境设置,以及实现无缝集成的设计流程和实践操作。通过案例分析,展示了SkyWater PDK与FPGA集成在工业应用中的实际效果和高级功能实现的可能性。最后,本文展望了SkyWater PDK与FPGA集成的发展趋势,指出了行业发展的技术趋势和面临的挑战,提出了相应的应对策略。

# 关键字

SkyWater PDK;FPGA集成;设计兼容性;IP核集成;信号处理;技术创新

参考资源链接:[探索SkyWater开源PDK:免费130nm硅工艺](https://wenku.csdn.net/doc/30yt3e1vrc?spm=1055.2635.3001.10343)

# 1. SkyWater PDK与FPGA集成概述

## 1.1 引言

在现代电子设计领域,SkyWater PDK (Process Design Kit) 和 Field-Programmable Gate Array (FPGA) 的结合使用正变得越来越普遍,特别是在需要快速原型开发和定制集成电路解决方案的场合。本章旨在为读者提供一个关于SkyWater PDK与FPGA集成的入门级概述,为后续深入探讨这一主题打下基础。

## 1.2 SkyWater PDK与FPGA集成的意义

SkyWater PDK为设计人员提供了一套完整的工具和信息,以利用SkyWater的130纳米CMOS工艺技术进行集成电路设计。结合FPGA,设计人员能够快速部署和测试数字逻辑电路,这些电路与硅芯片相比,既快速又灵活。通过这种集成,工程师不仅能够加速产品的研发周期,还能够更有效地对设计进行优化和验证。

## 1.3 SkyWater PDK与FPGA集成的挑战

尽管这种集成提供了多种优势,但同时它也带来了独特的挑战。设计人员需要克服诸如设计兼容性、时序约束、布局布线等技术难题,确保SkyWater PDK与FPGA的无缝集成。在后续章节中,我们将深入探讨这些挑战,并提供解决这些问题的策略和方法。

# 2. 理论基础与技术背景

## 2.1 SkyWater PDK技术解析

### 2.1.1 PDK的定义和作用

在半导体行业中,PDK(Process Design Kit)是设计与制造集成电路的关键工具套件。PDK为设计师提供了一套完整的数据包,用于与特定的晶圆制造工艺相兼容的设计。这些数据包包含了一系列的设计规则、元件库、以及用于布局和验证的标准单元。PDK使得设计师能够将设计意图转换为能够在特定制造工艺下实际生产的物理形态。

### 2.1.2 SkyWater PDK的特性

SkyWater PDK是一套开源的半导体工艺设计工具包,它使得设计者可以访问并利用SkyWater Technology Foundry的130纳米及90纳米工艺。SkyWater PDK的显著特性包括:

- 开源性:提供免费访问,使设计者能够查看和修改源代码,这在商业PDK中是不常见的。

- 开放合作:鼓励社区贡献,改进设计和制造流程。

- 多样化应用:适合于从教育到商业的不同规模的项目。

- 高度集成:可与主流EDA(Electronic Design Automation)工具链无缝集成,方便设计实现。

## 2.2 FPGA工作原理

### 2.2.1 FPGA的基本组成和工作流程

FPGA(Field-Programmable Gate Array)是一种可以通过编程来配置的半导体设备,拥有可重配置的逻辑块、可编程的互连和可编程的I/O块。FPGA能够实现复杂的硬件功能,广泛应用于数字信号处理、嵌入式系统、汽车、航空等行业。

FPGA的基本组成包括:

- **可配置逻辑块(CLBs)**:CLBs是FPGA的核心组成部分,可以根据需要实现各种逻辑功能。

- **输入/输出块(IOBs)**:IOBs负责与FPGA外部的设备进行电气连接。

- **可编程互连**:允许逻辑块之间以及与I/O块之间的灵活连接。

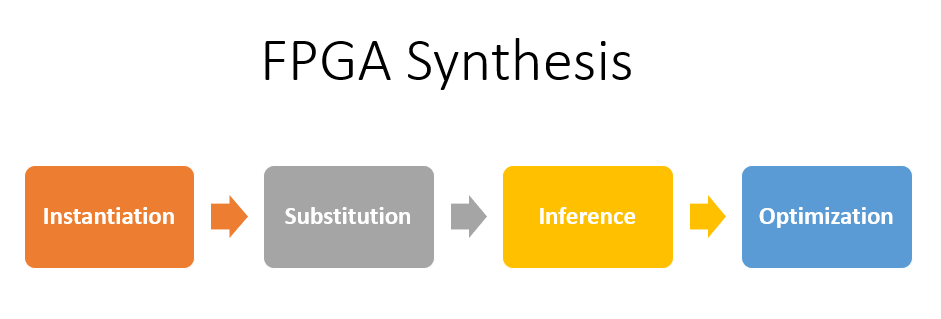

FPGA的工作流程主要分为三个阶段:

1. **设计输入**:通过硬件描述语言(HDL)如VHDL或Verilog来描述所需实现的电路功能。

2. **综合与实现**:将HDL代码综合成FPGA的逻辑元素,并在物理设备上布局与布线。

3. **配置与测试**:将生成的配置文件下载到FPGA中,完成最后的硬件测试。

### 2.2.2 FPGA与ASIC和CPU的比较

FPGA相比于传统的ASIC(Application-Specific Integrated Circuit)和CPU(Central Processing Unit)具有其独特的优势和局限性:

- **FPGA对比ASIC**:FPGA在可编程性和上市时间上占有优势,但ASIC在成本和性能上更具有优势,适合大批量生产。

- **FPGA对比CPU**:FPGA可以实现高度并行处理,适合算法密集型任务,而CPU更倾向于执行通用计算任务,性能可能不如FPGA在特定算法上的表现。

## 2.3 集成中的关键考量

### 2.3.1 设计兼容性问题

在集成SkyWater PDK与FPGA的过程中,设计兼容性是关键。SkyWater PDK提供了与FPGA设计相兼容的制造工艺,但仍然需要关注以下几点:

- **时钟域交叉**:在FPGA设计中,不同的功能模块可能运行在不同的时钟域,需要通过适当的同步机制来处理时钟域交叉,防止数据丢失或不确定性。

- **信号完整性**:高速信号在传输时可能会因为各种寄生效应而产生失真,需要通过布线策略和板级设计来保证信号完整性。

### 2.3.2 时序约束与布线策略

对于高性能FPGA设计来说,时序约束和布线策略尤为关键,因为它们直接影响到电路的性能和稳定性。

- **时序约束**:定义了电路的时序要求,如时钟频率、信号延迟等,是确保电路在规定时间内完成操作的关键。

- **布线策略**:决定了FPGA内部信号的路由方式,合理布线可以避免信号干扰和延迟,保障设计的可靠性。

为了管理这些考量,设计师需要在设计阶段就使用EDA工具对时序进行分析和约束,并在布线阶段采取有效的布线策略。

```mermaid

graph TD

A[设计开始] --> B[时序分析]

B --> C[布线策略制定]

C --> D[布线实施]

D --> E[设计验证]

E --> |通过| F[设计成功]

E --> |未通过| B[重新时序分析]

```

以上Mermaid流程图展示了在FPGA设计中时序和布线策略的循环迭代过程,它从设计开始,经历时序分析,布线策略制定,实际布线实施,设计验证,直到最终设计成功或需要重新分析。

# 3. 集成工具和环境设置

## 3.1 集成工具选择与配置

集成工具的选择和配置对于整个SkyWater PDK与FPGA集成过程至关重要。本节将会详细介绍如何根据项目需求选择合适的工具链,并给出相应的环境搭建步骤。

### 3.1.1 工具链介绍

在进行SkyWater PDK与FPGA的集成时,工具链选择是第一步。常用的工具链包括但不限于:

- **Yosys**: 用于综合逻辑设计到FPGA的门级结构。

- **nextpnr**: 作为后端工具,负责实现从综合的网表到FPGA芯片的实际配置。

- **OpenLane**: 是一个开源的综合工具,可将RTL代码综合成门级网表。

- **Gowin EDA**: SkyWater PDK支持的特定工具,能够处理SkyWater工艺设计。

选择合适的工具链是优化设计和提高集成效率的基础。每种工具都具有独特的特点和优势,我们需要根据项目的具体要求和目标来决定。

### 3.1.2 环境搭建步骤

为了搭建一个适合SkyWater PDK与FPGA集成的工作环境,我们需要遵循以下步骤:

1. **安装基础依赖**: 根据选用的工具链安装所有必须的基础软件和库。

2. **配置工具链**: 设置环境变量,确保所有工具链命令都可在命令行中直接调用。

3. **下载PDK**: 从SkyWater官方获取PDK,并按照其指导进行解压和配置。

4. **测试环境**: 运行一些基础的示例设计来确认工具链和环境搭建成功。

以下是使用Yosys和nextpnr工具链搭建环境的一个简化示例代码块:

```bash

# 安装Yosys

sudo apt-get install yosys

# 安装nextpnr

sudo apt-get install nextpnr-ice40

# 下载并配置SkyWater PDK

git clone https://github.com/google/skywater-pdk.git

cd skywater-pdk

./configure.sh

# 测试环境,通过运行一个简单的综合测试

yosys -p "synth_ice40 -blif example.blif" example.v

```

上述步骤确保了所有必要的工具和PDK都已经正确设置,可以通过运行测试用例来验证搭建的环境是否可用。

## 3.2 集成开发环境搭建

集成开发环境(IDE)的搭建是提

0

0