【Vivado 2021.1综合优化高级技巧】:逻辑利用率大提升

发布时间: 2024-12-19 23:49:37 阅读量: 3 订阅数: 5

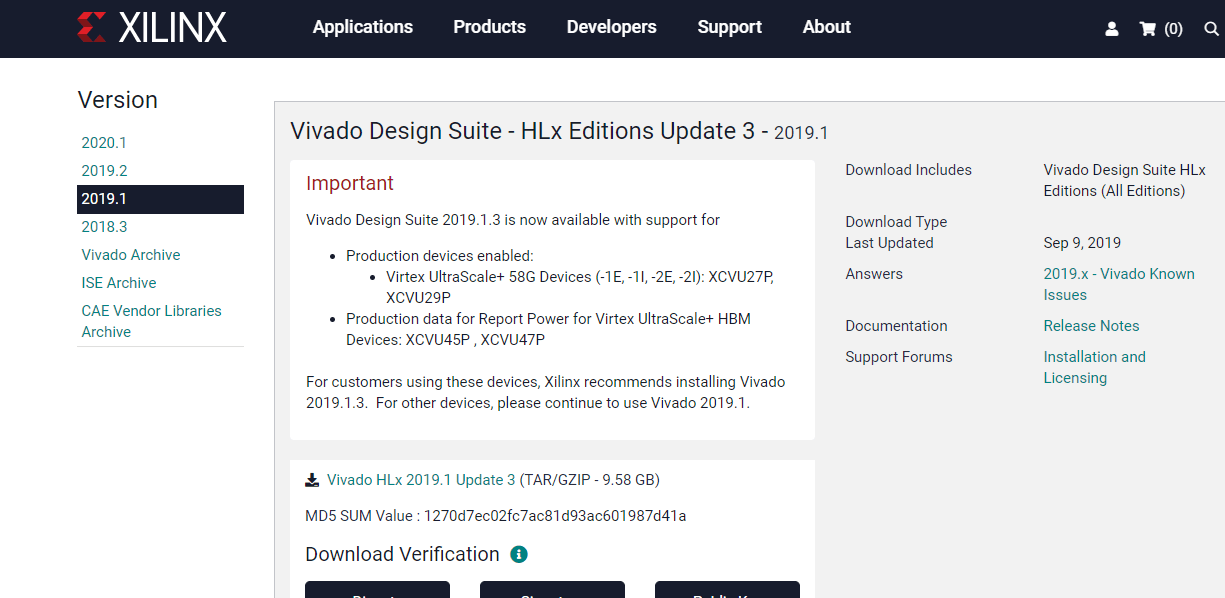

vivado2021.1安装教程.pdf

# 摘要

本论文深入探讨了Vivado综合优化的基础知识、实践技巧以及高级应用。首先,概述了逻辑利用率优化的重要性及其在FPGA设计中的作用,接着详细介绍了优化前的准备工作,包括资源消耗分析和综合约束的应用。在实践应用章节,针对性能、资源利用率和功耗提出了多种面向不同目标的优化技巧。进阶技巧章节则聚焦于高级综合命令、特殊设计场景下的优化以及案例分析。最后,介绍了Vivado分析工具的使用方法,行业内最佳实践,以及未来技术创新的方向。本文旨在为FPGA设计者提供全面的优化知识与技能,以应对复杂的设计挑战。

# 关键字

Vivado综合优化;逻辑利用率;性能优化;资源利用率;功耗管理;Tcl脚本;人工智能;FPGA设计;IP核集成;时序驱动优化

参考资源链接:[Xilinx Vivado 2021.1安装全程指南](https://wenku.csdn.net/doc/179a4hyf1b?spm=1055.2635.3001.10343)

# 1. Vivado综合优化基础概览

在本章节中,我们将对Vivado综合优化的基础知识进行概览,为后续章节深入探讨优化细节打下基础。Vivado作为Xilinx公司推出的集成设计环境,其综合优化功能对于FPGA开发者而言至关重要。综合优化不仅影响到硬件描述语言(HDL)代码转换为FPGA上实际逻辑电路的效率,还直接影响设计的性能、资源利用率、功耗等关键指标。我们将通过介绍综合优化的基本概念、常见误区以及优化流程,为您提供一个全面的理解框架。接下来,章节将逐步展开,带领您进入Vivado综合优化的精彩世界。

```markdown

- 了解综合优化的基本概念和目的。

- 掌握Vivado综合优化流程的初步了解。

- 为深入分析具体优化技巧和高级应用做好铺垫。

```

# 2. 深入理解逻辑利用率的优化

### 逻辑利用率的定义和重要性

#### 逻辑利用率在FPGA设计中的角色

在讨论FPGA设计时,逻辑利用率是一个关键指标,它指的是设计在FPGA内部逻辑资源中所占用的比例。高逻辑利用率通常意味着设计更有效地使用了FPGA资源,这可以提高资源的使用效率,降低整体成本,并可能提升设备的性能。然而,过分追求逻辑利用率的提高也可能导致设计变得过于紧凑,增加了时序风险和布局布线的复杂性。

#### 影响逻辑利用率的主要因素

逻辑利用率受到多种因素的影响。首先,算法的效率直接影响到逻辑单元的使用数量。高效的算法能够减少不必要的计算,从而降低资源消耗。其次,设计的并行性也会影响逻辑利用率;在某些情况下,增加逻辑单元以实现并行处理可以提高性能。此外,综合策略和优化设置是影响逻辑利用率的又一个重要因素。通过合适的综合参数设置,可以优化设计,达到逻辑利用率和性能之间的平衡。

### 优化前的准备:分析设计和资源消耗

#### 如何收集设计的资源消耗数据

在进行逻辑利用率优化前,首先需要了解当前设计的资源使用情况。Vivado提供了多种报告工具来帮助工程师收集数据。例如,使用"report utilization"命令可以生成关于逻辑元件、查找表、寄存器等资源的消耗报告。为了进一步细化分析,还可以使用"report timing"命令来获取时序分析结果,这对于确定是否有必要进行逻辑优化至关重要。

#### 常见的资源瓶颈分析

分析设计时,资源瓶颈是需要特别关注的问题。它们可能是由于特定的逻辑结构或过于密集的逻辑路径导致的。Vivado的分析工具,特别是FPGA资源的三维视图,能够直观地展示出哪些资源区域被过度使用。识别这些瓶颈后,工程师可以采取相应的优化措施,例如重构设计的特定部分或重新分配资源。

#### 利用报告文件进行初步优化

优化过程的第一步通常是基于生成的报告文件进行初步调整。报告文件包含了综合过程中可能被忽视的设计问题。例如,一个报告可能会指出某些模块有大量的组合逻辑,这可能会对时序产生不利影响。工程师可以通过重构这些模块或者调整综合约束来解决这些问题。此外,报告还可能建议对某些路径进行 Pipelining,以达到更好的时序性能。

### 逻辑综合的高级设置

#### 优化策略的选择和应用

在逻辑综合阶段,优化策略的选择对于提高逻辑利用率至关重要。Vivado提供了多种优化策略,包括面积优化、速度优化和功耗优化。面积优化策略倾向于减少逻辑单元的数量,以降低设计的面积占用。速度优化策略则通过增加逻辑深度来满足时序需求。选择适当的优化策略需要根据设计的具体需求来确定。

#### 综合约束的作用与技巧

综合约束在优化设计中扮演了重要角色。它们指导综合工具在布局和布线时如何处理时序要求,对最终的逻辑利用率有直接影响。合理设置综合约束可以帮助工程师找到逻辑利用率和性能之间的最佳平衡点。例如,为关键路径设置合理的时序约束,可以确保在不牺牲性能的前提下,尽可能地减少资源消耗。

#### 管脚分配与优化的关联

管脚分配(Pinout)是优化逻辑利用率的另一个关键步骤。在Vivado中,自动或手动的管脚分配都可以影响到逻辑综合。例如,当逻辑块彼此接近时,可以减少信号传输的延迟,从而可能提高性能或降低逻辑单元的使用。在某些情况下,重新分配管脚甚至可以解决时序问题,让优化工作更加高效。因此,综合阶段对管脚分配的考虑,是确保设计逻辑利用率优化的重要一环。

# 3. Vivado综合优化实践应用

Vivado综合优化不仅仅是一门科学,更是一门艺术。在掌握了基础概览和逻辑利用率优化的理论知识之后,本章将进入实际操作层面,探讨一些实践应用中的优化技巧。这些技巧将帮助设计者针对性能、资源利用率以及功耗三个关键维度进行系统优化。

## 3.1 面向性能的优化技巧

### 3.1.1 时序驱动的优化方法

在FPGA设计中,时序是确保信号正确到达其目标位置的关键。时序驱动的优化方法要求设计者关注时序报告中的各项指标,比如 Setup 时间、Hold 时间、时钟不确定性等。

一个典型的时序优化流程涉及以下几个步骤:

1. **时序约束设定**:首先,要确保所有的时序约束都已正确设置。这包括定义输入/输出延迟、生成时钟以及多周期路径的要求。

2. **时序分析**:接下来,进行时序分析查看关键路径。Vivado提供丰富的时序报告,可以根据需要调整查看方式。

3. **逻辑优化**:对关键路径上的逻辑进行优化,包括减少逻辑级数、使用更

0

0