【硬件设计要点】:确保ZYNQ QSPI FLASH启动系统稳定性的关键因素

发布时间: 2024-12-25 17:36:49 阅读量: 7 订阅数: 12

ZYNQ QSPI FLASH启动系统的方法,包括各种错误的解决,petalinux的使用,vivado的使用,详细讲解(一)

# 摘要

ZYNQ QSPI FLASH启动系统在现代嵌入式系统设计中扮演着关键角色,它涉及硬件设计、启动过程优化、系统稳定性及高级应用等方面。本文首先概述了ZYNQ QSPI FLASH启动系统的基本概念,随后深入探讨了硬件设计的基础,包括FLASH的选择、硬件连接、信号完整性和电源管理。在启动过程优化章节,时序分析、配置及引导过程以及失败诊断与修复方法被详细说明。系统稳定性的实践应用部分讨论了环境因素、系统测试和验证,以及系统维护与升级策略。文章最后一章聚焦于高级应用和案例研究,展示了冗余存储、错误检测、在线更新等高级特性在实际中的应用。整体而言,本文为工程技术人员提供了一套全面的ZYNQ QSPI FLASH启动系统的理论知识和实践指导。

# 关键字

ZYNQ;QSPI FLASH;硬件设计;启动优化;系统稳定性;高级应用

参考资源链接:[ZYNQ开发板QSPI FLASH启动全攻略:错误解决与petalinux、vivado实战](https://wenku.csdn.net/doc/6my99rrxj8?spm=1055.2635.3001.10343)

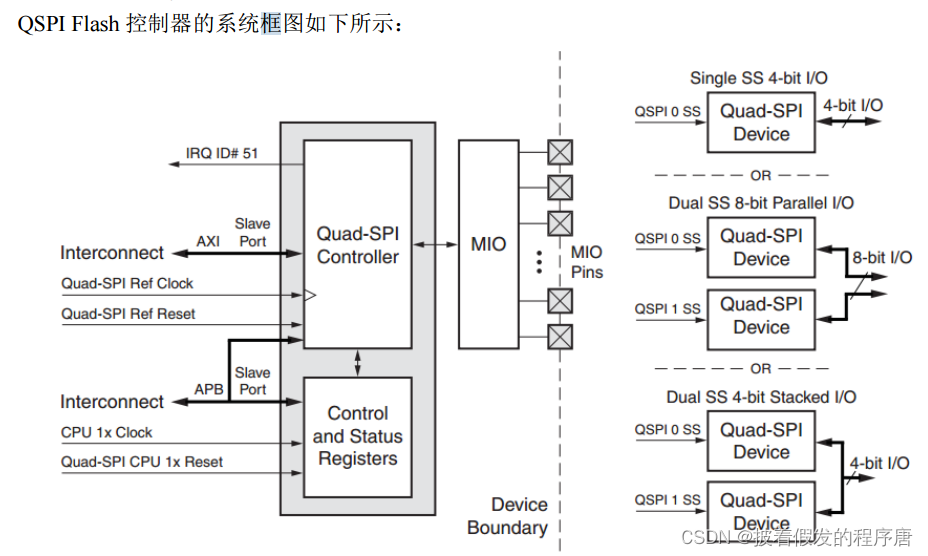

# 1. ZYNQ QSPI FLASH启动系统概述

在现代嵌入式系统设计中,ZYNQ QSPI FLASH作为非易失性存储器,扮演着至关重要的角色。它不仅负责存储系统的启动代码,也用于存放运行时所需的数据和配置文件。对于需要高速、高可靠性的系统来说,理解ZYNQ QSPI FLASH的启动系统是至关重要的。本章旨在对ZYNQ QSPI FLASH启动系统进行一个总体的概述,为读者提供一个清晰的概念框架,理解其在系统启动过程中的作用及其重要性。

## 1.1 FLASH的作用与特点

ZYNQ QSPI FLASH,作为四线串行外设接口(QSPI)闪存技术的一种,因其高速、高容量和高可靠性,被广泛应用于ZYNQ平台的系统启动中。它的特点主要包括:

- **高速读取能力**:相较于传统SPI接口,QSPI接口提供了更高的数据吞吐率,这对于提升系统启动速度有着重要意义。

- **灵活的配置选项**:QSPI FLASH支持多种模式,如单线、双线和四线模式,以及用于存储引导代码、操作系统和应用程序代码的能力。

## 1.2 系统启动流程简介

ZYNQ QSPI FLASH的系统启动流程通常遵循以下步骤:

1. **上电复位**:设备上电后,ZYNQ处理器会根据内部设定的启动优先级来加载QSPI FLASH中的数据。

2. **BootROM执行**:处理器进入BootROM模式,从QSPI FLASH中加载初始程序加载器(FSBL)。

3. **FSBL运行**:FSBL随后初始化系统硬件,并加载应用固件,如操作系统。

这一过程中,QSPI FLASH是整个启动链路的关键节点,任何对FLASH的错误配置都可能导致系统无法启动或运行不稳定。因此,一个高效的启动系统设计,必须考虑到ZYNQ处理器与QSPI FLASH的兼容性,以及如何优化启动时序和配置。

本章内容为后续章节的深入分析打下了基础,使得读者可以更好地理解硬件设计细节、启动过程的优化,以及系统稳定性和应用案例研究。

# 2. ZYNQ QSPI FLASH硬件设计基础

### 2.1 FLASH选择与兼容性

#### 2.1.1 FLASH型号的选择标准

当涉及到ZYNQ QSPI FLASH的选择时,首先必须考虑的是应用需求。这些需求可能包括存储容量、读写速度、功耗以及成本等。例如,一个高端应用可能需要更快的读写速度和更大的存储容量,而成本可能不是主要考虑因素。在此情况下,高容量、高速率的NAND FLASH可能是一个更合适的选择。

在选择标准中,需要参考的数据手册中提供的特性如:

- 最大读写速度

- 存储容量

- 接口类型(例如,双数据速率DDR模式)

- 电气特性(电压等级、工作电流)

- 支持的寿命次数(P/E cycles)

此外,也需考虑FLASH的物理尺寸和封装类型,以确保其能够适应给定的硬件设计中。

```markdown

| 特性 | 详情 |

|-------------------|--------------------------------------------------------------|

| 存储容量 | 32MB, 64MB, 128MB, 256MB, 512MB, 1GB等。 |

| 接口类型 | 单数据速率(SDR), 双数据速率(DDR) |

| 最大读写速度 | 最高104MB/s (DDR), 52MB/s (SDR) |

| 电压等级 | 1.8V或3.3V |

| 工作电流 | 待机电流、读写电流 |

| 支持的寿命次数 | 标准型(P/E cycles): 10,000, 高可靠性(HLC): 100,000 |

| 封装类型 | BGA, WSON, TSOP等 |

```

在兼容性考量中,还需要考虑FLASH与ZYNQ处理器之间的接口协议的匹配程度。ZYNQ-7000系列通常提供QSPI接口,因此,所选FLASH需要支持与之兼容的QSPI通信协议。

#### 2.1.2 与ZYNQ处理器的兼容性考量

ZYNQ处理器内置的QSPI接口能够与多种QSPI FLASH设备进行通信。但出于性能和功能性的考虑,选择的FLASH应当在时序、电压等级、引脚定义以及支持的模式上与ZYNQ处理器兼容。

例如,ZYNQ处理器支持的最大QSPI频率通常为104MHz,在选择FLASH设备时,应确保其支持至少等于或高于此频率的通信速率。对于电压等级,处理器在不同模式下可能支持3.3V或1.8V,因此要保证FLASH的VCC兼容所选模式的电压等级。

### 2.2 硬件连接与信号完整性

#### 2.2.1 硬件连接要点

在硬件连接方面,需要关注的是FLASH与ZYNQ处理器之间的物理连接,包括线路布局和信号完整性。由于QSPI接口的数据传输速率较高,布线需要遵循高速信号布线规则,比如尽量减少布线长度和拐角,避免近邻干扰,以及控制阻抗匹配等。

ZYNQ处理器与FLASH的连接通常需要以下几条关键线路:

- SCLK: 串行时钟信号

- CS#: 片选信号,控制FLASH的激活与休眠状态

- IO[3:0]: 数据输入输出线路

这些线路需要直接连接,避免交叉布线,并且可能需要使用微带线或带状线以减少信号衰减和反射。

#### 2.2.2 信号完整性分析和优化策略

信号完整性分析是指确保信号在传输路径上的质量和完整性。高速信号传输,特别是时钟信号,如果处理不当,可能会导致信号失真,产生时钟抖动等问题。为了保证信号完整性,设计者需要进行以下操作:

1. 使用阻抗匹配技术,如串联终端电阻,以减少信号反射。

2. 信号线应当远离可能产生干扰的线路,比如高速数字信号线和电源线。

3. 使用差分信号设计,特别是对于时钟信号,以提高信号的抗干扰能力。

0

0