时序驱动的硬件设计:Verilog时序检查的战略与方法

发布时间: 2024-12-17 11:36:05 阅读量: 3 订阅数: 13

基于FPGA的线阵CCD驱动时序电路设计

参考资源链接:[Verilog时序检查详解:$setup、$hold与$setuphold](https://wenku.csdn.net/doc/848qwsffrf?spm=1055.2635.3001.10343)

# 1. ```

# 第一章:时序驱动硬件设计概述

硬件设计领域中的时序驱动设计是一种以时序为核心的设计方法,它强调在整个设计流程中,时序的准确性和可靠性是确保电路能够正常工作的重要因素。时序驱动设计不仅关注于逻辑电路的正确实现,更重视信号在硬件中的传播时间,以及各信号之间的时间关系,确保它们能够在正确的时间到达相应的节点。

## 1.1 时序驱动设计的重要性

在高速数字电路设计中,时序是衡量电路性能的关键指标之一。它不仅影响电路的工作频率,而且对于电路的稳定性和可靠性有决定性的作用。随着集成电路的发展,时钟频率越来越高,时序设计的复杂性也日益增加。设计者必须能够准确地预测并优化电路中的时序路径,确保电路在特定的时钟频率下能够稳定运行。

## 1.2 时序驱动设计的基本概念

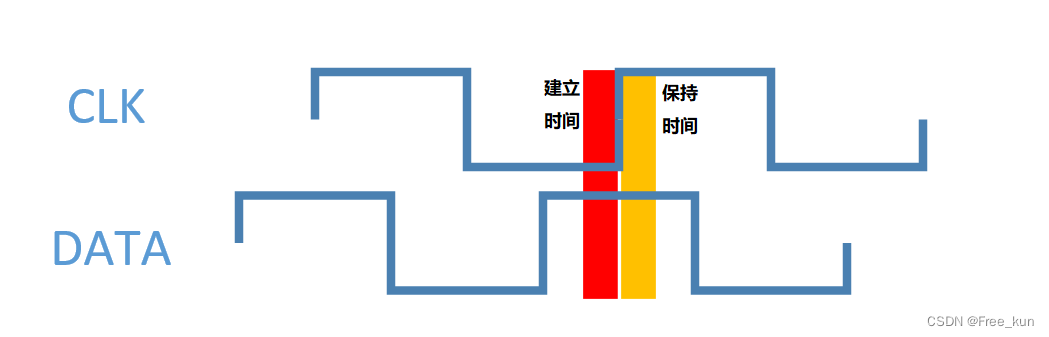

时序驱动设计的核心在于确保数据和控制信号能够在预定的时间内到达目标电路单元,从而满足系统时序的要求。这涉及到对时钟信号、数据路径、存储元件和信号之间的关系进行精确的计算和控制。设计者需要理解和应用各种时序概念,如设置时间(setup time)、保持时间(hold time)、传播延迟(propagation delay)和时钟偏差(clock skew)等,这些都是保证电路正确工作的基本要素。

时序驱动硬件设计的目的是通过综合考虑电路的时序要求,以一种系统化和结构化的方式指导硬件设计和验证过程,从而提高设计效率和电路性能。

```

# 2. Verilog时序基础

### 2.1 时序逻辑与时钟信号

#### 2.1.1 时序逻辑的概念和特点

时序逻辑是数字电路设计中的一种重要逻辑类型,其输出不仅取决于当前的输入,还取决于之前输入的历史状态。在Verilog硬件描述语言中,时序逻辑通常通过引入时钟信号来实现,以确保电路能够记住过去的信息并在下个时钟周期做出响应。

时序逻辑的典型特点包括:

- 状态变化与时间有关,由时钟信号触发。

- 存储元素如触发器或寄存器用于存储历史状态。

- 可以实现计数器、状态机和存储器等复杂的逻辑功能。

例如,一个简单的上升沿触发的D型触发器可以由以下Verilog代码表示:

```verilog

module d_ff (

input wire clk, // 时钟信号

input wire rst_n, // 异步复位信号,低电平有效

input wire d, // 数据输入

output reg q // 数据输出

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

q <= 1'b0; // 异步复位,输出置零

end else begin

q <= d; // 上升沿到来时,输出跟输入

end

end

endmodule

```

在此代码中,输出`q`的值将在每个时钟上升沿到来时更新为输入`d`的值。如果复位信号`rst_n`为低,则输出`q`将被强制置零,无论时钟信号如何变化。

#### 2.1.2 时钟信号的作用与要求

时钟信号是数字系统中的“心跳”,为电路提供同步的时间基准。它对时序逻辑的设计至关重要,因为它定义了数据可以有效采样和存储的准确时刻。时钟信号的稳定性和精确性直接影响电路的性能和可靠性。

在设计时钟信号时,需考虑以下几个要点:

- **时钟频率**:决定了电路处理速度的上限。

- **时钟偏斜(Skew)**:各个部分的时钟到达时间差异,过大的偏斜可能导致数据同步问题。

- **时钟偏移(Jitter)**:时钟周期的微小变化,需要控制在一个很小的范围内以保证电路的稳定性。

- **时钟源质量**:纯净且稳定的时钟源是保障电路稳定运行的前提。

设计时钟网络时,通常需要使用专门的时钟树综合(Clock Tree Synthesis, CTS)工具,以确保时钟信号在整个芯片上的均匀分布,并符合以上要求。

### 2.2 触发器与寄存器

#### 2.2.1 触发器的类型和工作原理

触发器是构成时序逻辑的基本单元,分为以下几种类型:

- D型触发器(数据触发器)

- T型触发器(T触发器)

- JK型触发器

- SR型触发器(集电极/源极复位触发器)

每个类型的触发器有其独特的逻辑行为,但它们共有的特点是可以存储信息。例如,D型触发器在时钟上升沿到来时,将输入数据D的值传输到输出Q。

下面是一段描述D触发器行为的Verilog代码:

```verilog

always @(posedge clk) begin

Q <= D; // 在每个时钟上升沿时,D的值赋给Q

end

```

#### 2.2.2 寄存器的结构和配置方法

寄存器是由多个触发器组成的存储结构,可以存储多位数据。寄存器的配置方法取决于其应用的具体需求,可以是串行配置、并行配置或者混合配置。在FPGA或ASIC中,寄存器可用来实现数据的缓存、寄存器文件、计数器等。

寄存器的Verilog代码实现通常使用数组的形式表示:

```verilog

module register (

input wire clk, // 时钟信号

input wire rst_n, // 异步复位信号

input wire [N-1:0] data, // 输入数据

output reg [N-1:0] out // 输出数据

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

out <= 0; // 异步复位

end else begin

out <= data; // 并行加载数据

end

end

endmodule

```

在此代码中,寄存器模块可以并行地加载新的数据到输出`out`,或者在复位信号激活时将输出置为零。

### 2.3 时序约束与优化

#### 2.3.1 时序约束的必要性

时序约束是在数字系统设计中用来确保数据在正确的时间内到达,并在预定的时间内稳定的技术。不正确的时序约束可能导致数据不稳定、时序违例等问题,严重影响电路的性能和可靠性。在复杂的现代设计中,确保所有信号都能满足时序要求变得尤为重要。

时序约束包括但不限于以下几个方面:

- 时钟定义(create_clock)

- 输入和输出延迟(set_input_delay/set_output_delay)

- 时钟偏斜(set_clock不确定性时序约束(set_max_delay/set_min_delay)

使用时序约束可以为时序分析和优化工具提供必要的信息,有助于提高设计的稳定性和性能。

#### 2.3.2 常见时序优化技术

时序优化技术的目的是确保所有信号路径满足时序要求,包括最小化路径延迟和最大化设计性能。一些常见的时序优化技术包括:

- 时钟树优化(CTS)

- 路径延迟平衡

- 逻辑重定时

- 多周期路径约束

- 预布局和后布局优化

下面是一个使用时钟树优化(CTS)的简单案例:

```verilog

// 假设有一个50MHz的时钟源CLK,使用create_clock定义时钟约束

create_clock -name CLK -period 20 -waveform {0 10} [get_ports CLK]

```

在这段Tcl脚本中,定义了一个周期为20纳秒(即50MHz)的时钟信号。这样的时钟约束对于时序分析工具来说至关重要,因为它们为工具提供了时钟信号的基准信息。

# 3. Verilog时序检查机制

## 3.1 时序仿真与测试

### 3.1.1 仿真测试的重要性

在数字电路设计中,仿真测试是确保设计满足功能和性能要求的关键步骤。特别是在时序设计领域,仿真测试更是验证时序准确性和功能正确性不可或缺的环节。它允许设计者在实际硅片制造之前,发现并修正潜在的设计错误,避免了昂贵的返工成本和时间延误。

时序仿真通常涉及对设计施加各种时钟频率、输入信号模式以及操作条件,模拟实际操作情况。通过这种方式,设计者可以观察电路在不同操作条件下的响应,确保所有时序参数都符合预定规格。这包括设置和保持时间的检查、路径延迟的计算和分析、以及在多种操作条件下电路稳定性和性能的验证。

### 3.1.2 测试环境搭建与案例分析

搭建一个有效的时序仿真测试环境,首先需要准备一个高质量的测试平台。这通常包含一个或多个时序约束文件、详尽的测试向量集,以及用于运行仿真和收集结果的工具。例如,对于Verilog设计,可以使用如ModelSim或VCS这样的仿真工具进行测试。

在案例分析中,我们可以考虑一个简单的双触发器链路(DFF链),这是时序分析中常见的元素。设计者需要定义一个测试台架(testbench),创建输入信号的变化,并观察DFF链路的输出,以确保在不同的时钟

0

0