数字电路新手入门:JK触发器工作原理及Multisim仿真操作(详细指南)

发布时间: 2024-12-23 11:38:53 阅读量: 5 订阅数: 6

# 摘要

本文深入探讨了数字电路中的JK触发器,从基础知识到高级应用,包括其工作原理、特性、以及在数字系统设计中的应用。首先,本文介绍了触发器的分类和JK触发器的基本工作原理及其内部逻辑。接着,详细阐述了Multisim仿真软件的界面和操作环境,并通过仿真实践,展示如何在Multisim中构建和测试JK触发器电路。进一步地,本文分析了JK触发器的时序特性,并讨论了其在数字系统设计中的重要性。最后,通过项目案例分析和常见问题解答,本文旨在帮助读者更好地理解和应用JK触发器,加强读者对数字电路设计的理解和实践能力。

# 关键字

数字电路;JK触发器;Multisim;时序分析;故障排除;数字系统设计

参考资源链接:[Multisim仿真实验:JK触发器的功能与操作](https://wenku.csdn.net/doc/8ai10l1hr5?spm=1055.2635.3001.10343)

# 1. 数字电路与触发器基础

在探索数字电路设计的奥秘时,触发器是一个不可或缺的元素。触发器是一种双稳态的数字电路组件,能够在输入信号的作用下改变自身的状态,并能够保持该状态直至下一个触发信号的到来。触发器是构成各种计数器、寄存器、存储器以及更复杂数字系统的基础组件。

## 1.1 触发器的分类与功能

触发器的分类多种多样,它们根据功能和设计原理被分为不同的类型,比如RS触发器、D触发器、T触发器和JK触发器等。不同的触发器在数字逻辑电路中担任着不同的角色,例如D触发器主要用于数据延迟,而JK触发器因其优越的特性被广泛应用于时序逻辑电路的设计之中。

## 1.2 触发器的基本工作原理

触发器的基本工作原理是根据输入信号的组合来控制其输出状态的变化。这些输入信号可以是时钟脉冲(CLK)、置位(SET)、复位(RESET)以及数据输入(D或J/K)。例如,当一个上升沿的时钟信号到达D触发器时,触发器的输出会变为输入数据D的值。触发器设计的巧妙之处在于它能够存储信息,这对于复杂逻辑操作和数据处理至关重要。

本章向读者介绍了触发器的类别及其基本工作原理,为后续深入了解JK触发器的特性和Multisim仿真实践打下坚实的基础。

# 2. JK触发器的工作原理

### 2.1 触发器的分类与功能

触发器是数字电路中的一种基本存储单元,广泛应用于时序逻辑电路。按照逻辑功能的不同,触发器主要分为以下几种类型:

- RS触发器(Reset-Set)

- D触发器(Data)

- T触发器(Toggle)

- JK触发器(命名自发明者Jack Kilby)

其中,JK触发器是RS触发器的一种改进型,因其在状态转换过程中的全面性和稳定性,成为了应用最广泛的触发器之一。

#### 2.1.1 介绍不同的触发器类型

RS触发器是最基础的触发器类型,它有两个输入端,分别是置位(Set)和复位(Reset)。RS触发器能够记住状态,但是当两个输入同时为高电平时,会进入不确定状态,这限制了它的应用。

D触发器增加了一个数据输入端,使得触发器可以存储一个比特的数据。D触发器解决了RS触发器的不确定状态问题,但需要一个时钟信号来控制数据的稳定存储。

T触发器具有一个输入端,每当输入端的信号为高电平时,触发器的状态就会翻转。T触发器可以用来构建计数器。

JK触发器是RS触发器的改良版,通过增加反馈,解决了输入同时为高时触发器进入不稳定状态的问题,具有更高的应用价值。

#### 2.1.2 触发器的基本工作原理

所有触发器都是依靠时钟信号(Clock)来触发状态转换的。它们接收输入信号,并在时钟信号的上升沿或下降沿改变状态。触发器的状态变化可以用来存储信息,例如上一个状态是0,则下一个状态变为1,反之亦然。这种变化可以用来驱动其他电路,或者在时序逻辑电路中保持中间值。

### 2.2 JK触发器的内部逻辑

#### 2.2.1 JK触发器的逻辑图和真值表

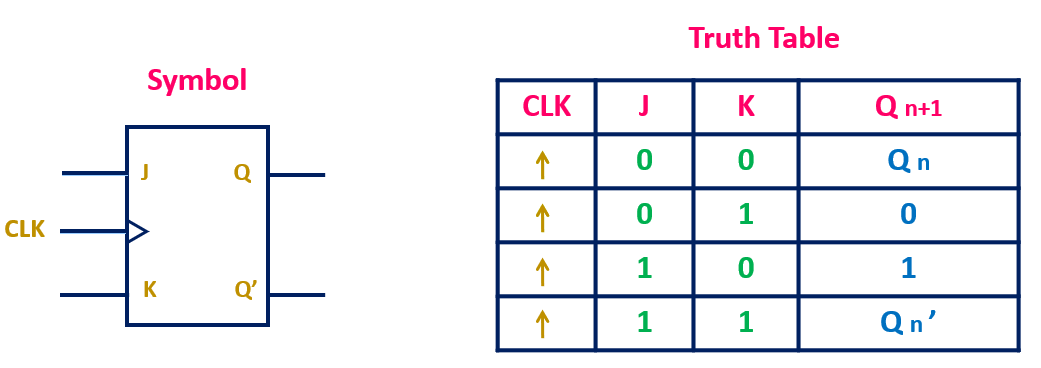

JK触发器的逻辑图包含一个基本的RS触发器和一些额外的逻辑门,通常包括两个与非门或异或门。JK触发器具有两个输入端J和K,以及一个时钟输入端CLK。真值表是描述不同输入状态下触发器输出行为的表。

以下是JK触发器的简化逻辑图及其真值表:

```

J ───┐

├─┐

K ───┘ │

├─|─> Q(输出)

CLK ─────┘

```

JK触发器的真值表如下:

| J | K | Q(当前状态) | Q+(下一个状态) |

|---|---|--------------|-----------------|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

#### 2.2.2 不同输入状态下的触发器行为

- 当J=K=0时,不论当前状态如何,触发器保持原状态不变。

- 当J=0且K=1时,触发器将被复位,输出为0。

- 当J=1且K=0时,触发器将被置位,输出为1。

- 当J=K=1时,触发器状态发生翻转。如果当前输出为0,则下一个状态为1;如果当前输出为1,则下一个状态为0。

### 2.3 JK触发器的特性

#### 2.3.1 状态表和特性方程

JK触发器的状态表和特性方程是分析其工作原理的重要工具。特性方程通常用Q+表示下一个状态,Q表示当前状态,J和K表示触发器的输入。

JK触发器的特性方程为:

```

Q+ = J NAND (Q NAND CLK) NOR K NAND (Q NAND CLK)

```

这个方程可以简化为:

```

Q+ = (J AND NOT Q) OR (NOT K AND Q)

```

使用这个方程,我们可以进一步理解在不同输入下JK触发器的输出变化。

#### 2.3.2 异步置位和清零特性

除了由时钟信号触发的同步操作外,JK触发器还具有异步置位(Set)和清零(Reset)的功能。这些操作允许我们在没有时钟信号的情况下改变触发器的状态。

异步置位(PRE)通常是低电平有效,当PRE=0时,无论其他输入为何值,输出Q总是为1。异步清零(CLR)也是低电平有效,当CLR=0时,无论其他输入为何值,输出Q总是为0。

### 代码块示例

```verilog

// Verilog代码实现JK触发器

module JKFlipFlop (

input J,

input K,

input CLK,

input PRE, // 异步置位

input CLR, // 异步清零

output reg Q

);

always @(posedge CLK or negedge PRE or negedge CLR) begin

if (!PRE) Q <= 1'b1; // 异步置位

else if (!CLR) Q <= 1'b0; // 异步清零

else begin

case ({J, K})

```

0

0