数据传输效率提升秘籍:MIPI CSI-2性能优化指南

发布时间: 2024-12-16 05:58:47 阅读量: 4 订阅数: 6

mipi_CSI-2_specification_v1_mipi_CSI2资料_mipicsi2_mipi_MIPIcsi_mi

参考资源链接:[mipi-CSI-2-标准规格书.pdf](https://wenku.csdn.net/doc/64701608d12cbe7ec3f6856a?spm=1055.2635.3001.10343)

# 1. MIPI CSI-2技术概述

## 1.1 技术背景与应用领域

MIPI CSI-2(Mobile Industry Processor Interface Camera Serial Interface 2)是由MIPI联盟开发的一种高速串行接口标准,广泛应用于移动设备和消费类电子产品中。它支持图像传感器和处理器之间的高速数据传输,保证了高质量图像数据的实时传输,从而为用户提供了流畅且高质量的多媒体体验。

## 1.2 核心优势

MIPI CSI-2的核心优势在于其高速度和低功耗的设计。它采用了差分信号传输技术,有效降低了电磁干扰,保证了数据传输的可靠性。同时,其协议设计简洁高效,使得实现硬件设计的成本相对较低,且易于集成和维护。

## 1.3 发展历程与版本

MIPI CSI-2技术自推出以来,经历了多个版本的迭代,每个新版本都针对性能和功能进行了优化。随着移动设备功能的不断增加和图像数据量的急剧增长,MIPI CSI-2也在持续演进,以满足更高带宽和更复杂应用场景的需求。

# 2. ```

# 第二章:理论基础与性能指标

## 2.1 CSI-2协议的基本原理

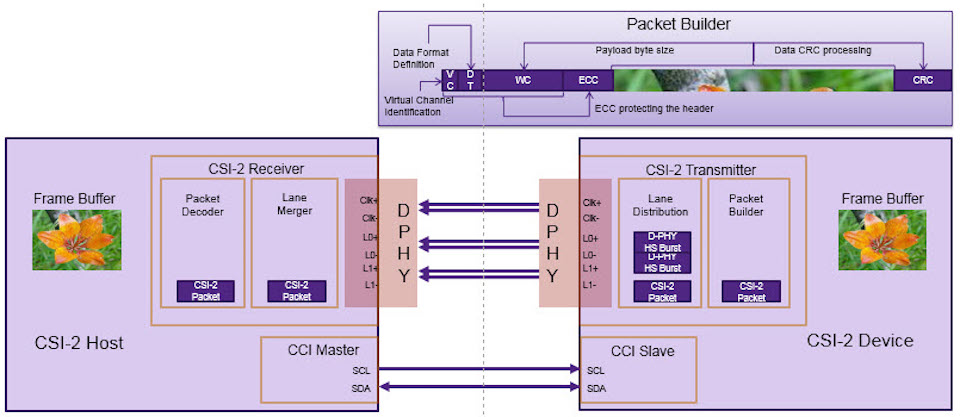

### 2.1.1 CSI-2接口的工作机制

MIPI CSI-2(Camera Serial Interface 2)是一种用于移动设备和图像传感器之间高速串行通信的接口。该协议定义了传感器和处理器之间的电气、协议和软件接口。CSI-2协议通过高速差分信号线进行数据传输,支持高达2 Gbps/通道的传输速率。工作时,数据以“lanes”(通道)的形式进行分组,每个lane由一对差分线组成。

为了理解CSI-2接口的工作机制,需要关注以下几个关键点:

- **数据包格式**:CSI-2协议中定义了两种类型的数据包——短数据包和长数据包,其中长数据包可以携带大量的像素数据。

- **数据打包与传输**:像素数据在传输前会被打包,包括数据包头(包括数据包长度和类型)以及实际的图像数据。

- **时序控制**:传输过程中的时序控制至关重要,确保数据在传感器和处理器之间同步。

### 2.1.2 关键性能指标介绍

在评估CSI-2接口的性能时,有几个关键指标需要特别关注:

- **带宽(Bandwidth)**:带宽是指在特定时间内可以传输的数据量。对于CSI-2接口,带宽主要取决于lane的数量和每lane的传输速率。

- **吞吐量(Throughput)**:吞吐量是指实际传输的数据量,会受到协议开销、数据包大小、数据压缩等因素的影响。

- **帧率(Frame Rate)**:帧率是指每秒可以传输多少帧图像,它直接影响视频流畅度。

理解这些性能指标对于优化系统级性能至关重要。

## 2.2 系统级性能评估

### 2.2.1 带宽和吞吐量的计算

评估CSI-2接口性能时,工程师需进行带宽和吞吐量的计算。带宽的计算公式相对简单,即lane数乘以单lane速率。但是,实际的吞吐量会受到协议层开销的影响,通常少于理论最大带宽。工程师会利用以下公式进行计算:

```

实际吞吐量 = (有效数据/数据包) * (数据包数/传输单元) * (传输单元数/时间单元)

```

### 2.2.2 帧率和数据压缩的影响

帧率是衡量视频质量的关键指标,它与图像传感器的捕获能力和CSI-2接口的传输能力密切相关。数据压缩技术(如JPEG、H.264等)的应用可以提高帧率,但同时也会带来额外的处理器负荷和可能的图像质量下降。

在实际应用中,对于带宽和帧率的权衡是系统设计的关键。工程师需要在保持较高帧率的同时,尽可能减少对图像质量的损害。

## 2.3 理论上的性能优化策略

### 2.3.1 码率控制与数据打包

码率控制是性能优化中的一项关键策略。合理的码率控制能确保数据传输的效率和稳定性。例如,通过调整数据打包策略,可以减少协议开销,提高吞吐量。工程师会根据应用需求调整数据包的大小,以平衡延迟和吞吐量。

### 2.3.2 多通道并行数据传输的优势

多通道并行数据传输是提升CSI-2接口性能的有效手段之一。通过同时使用多个lane,可以显著提升接口的总带宽。例如,使用4个lane,如果每个lane的传输速率是1 Gbps,则总带宽可达4 Gbps。

多通道并行传输要求硬件设计支持相应的通道数,同时软件层面上要实现通道间的有效协调和管理。尽管如此,多通道并行传输能有效减少传输时间,提高系统的整体性能。

在了解了理论基础和性能指标后,接下来章节会深入探讨在实践中的具体性能优化技巧。

```

# 3. 实践中的性能优化技巧

## 3.1 硬件设计的最佳实践

### 3.1.1 PCB布局与信号完整性

在硬件设计中,PCB布局对于保证信号完整性至关重要。信号完整性问题可能会导致数据传输错误和性能瓶颈,尤其是在高速接口中。优化信号完整性主要包括以下几个方面:

1. 保持信号走线短和直:在设计高速接口时,应尽量使走线短和直,以减少信号传输时间和电磁干扰。

2. 使用多层PCB:对于高速设计,至少使用4层板或更多层板以帮助实现信号回流,降低电磁干扰。

3. 控制阻抗匹配:确保走线阻抗与连接的元件阻抗相匹配,可以减少信号反射和传输损耗。

4. 避免信号交叉:在设计时尽量避免高速信号与其他信号走线交叉,以减少串扰。

5. 正确使用去耦电容:在IC周围放置去耦电容有助于滤除电源噪声,保证信号稳定。

在实际操作中,设计者需要综合运用这些技巧,以期达到最佳的硬件性能表现。

### 3.1.2 高速接口的终端匹配方案

高速接口的终端匹配是确保信号在接收端正确被读取的关键。不正确的终端匹配会导致信号失真和反射,对系统性能产生负面影响。终端匹配方案通常有以下几种:

1. 并联终端电阻:在信号路径末端并联一个与线路特性阻抗相匹配的电阻,可以减少信号反射。

2. AC耦合电容:使用AC耦合电容可以在不同电压等级的设备间传输信号,同时阻止直流分量引起的信号偏差。

3. 终端电压匹配:确保发送和接收设备间的电压水平一致,使用适当的终端电压可以避免逻辑电平不匹配的问题。

在设计和实现终端匹配时,工程师需要根据接口标准、信号速率和硬件规格来选择合适的匹配技术。

## 3.2 软件协议栈的优化

### 3.2.1 驱动层的优化技术

驱动层是连接硬件和操作系统的桥梁,优化驱动层可以提高数据传输效率和系统响应速度。以下是一些常见的驱动层优化技术:

1. 缓冲管理:合理地管理缓冲区大小和数量可以减少内存的无效占用和提升数据处理的灵活性。

2. 中断处理:减少中断服务例程的处理时间,可以降低对CPU的占用率,提高系统的响应速度。

3. 预取数据:驱动层可以预取即将使用的数据到缓存中,减少读取延迟。

4. 多线程处理:在多核处理器中,使用多线程技术可以同时处理多个数据传输任务,提高带宽利用率。

代码示例:

```c

// 示例代码:使用多线程进行数据传输的驱动层优化技术

void* thread_func(void* arg) {

// 处理数据传输任务

handle_data_transfer(arg);

return NULL;

}

int main() {

pthread_t thread_id;

```

0

0