HIP内核编程指南:实现高效的GPU算法

发布时间: 2025-01-06 07:17:21 阅读量: 10 订阅数: 18

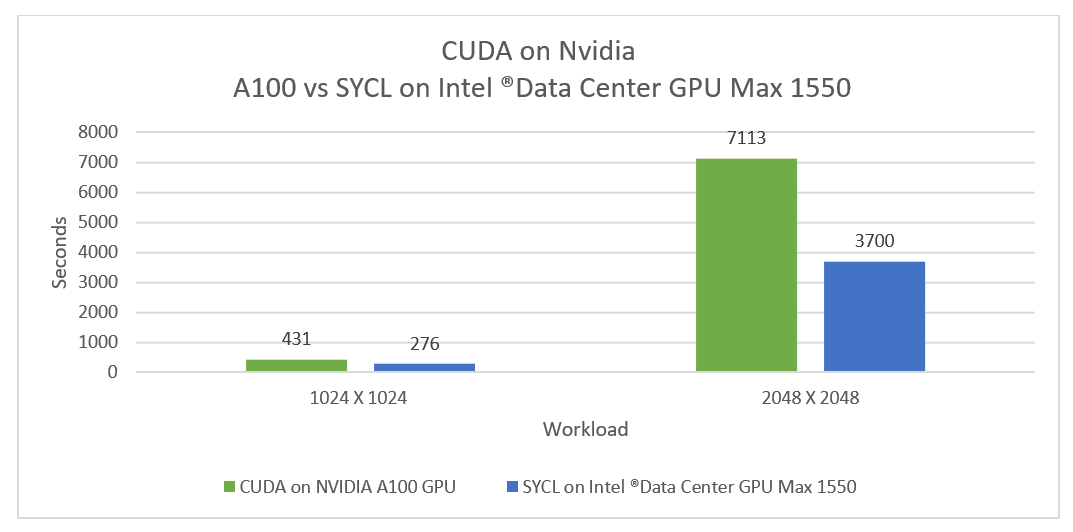

mixbench:一个GPU基准测试工具,用于评估混合操作强度内核(CUDA,OpenCL,HIP,SYCL)上的GPU

# 摘要

本文系统地介绍了GPU编程基础及其使用HIP(Heterogeneous-Computing Interface for Portability)的实践与优化。首先概述了HIP的基础知识,然后深入探讨了HIP的核心概念、内存管理、核函数编写优化、数据传输与同步、错误处理等关键技术细节。接下来,文章聚焦于HIP内核算法优化策略,包括内存访问模式的优化、并行算法设计改进以及性能剖析工具的使用。在实践应用方面,本文讨论了HIP与CUDA的互操作性、跨平台GPU应用程序构建以及HIP在深度学习和高性能计算中的应用。最后,展望了HIP的高级内存特性、生态系统的发展和未来技术方向。本文旨在为GPU开发者提供全面的HIP编程指导和优化策略,以及展望HIP技术的发展潜力和应用前景。

# 关键字

GPU编程;HIP;内存管理;核函数优化;并行算法;性能剖析;CUDA互操作性;深度学习;高性能计算;硬件异构性

参考资源链接:[AMD GPU编程入门:HIP框架详解](https://wenku.csdn.net/doc/3gdhyted3x?spm=1055.2635.3001.10343)

# 1. GPU编程基础与HIP概述

## GPU编程基础

在过去的十年中,图形处理单元(GPU)已经成为一种强大的工具,用于解决从图形渲染到科学计算的各种问题。由于它们的并行处理能力,GPU被广泛用于加速计算任务,特别是那些可以并行执行的算法。传统上,GPU编程主要通过使用NVIDIA的CUDA平台来实现。但是,随着对跨平台并行计算解决方案的需求增加,AMD推出了HIP(Heterogeneous-Compute Interface for Portability)作为一种新的编程接口。

HIP允许开发者编写一次代码,并在支持的GPU上运行,无论是AMD的GPU还是NVIDIA的GPU,同时减轻了硬件厂商特定优化的负担。HIP旨在提供与CUDA类似的用户体验,同时引入了标准化的可移植性层。与CUDA相比,HIP的源代码兼容性使它能够被编译为不同的后端架构,从而实现了更好的跨平台兼容性。

HIP概述

HIP由一系列工具和库组成,它将CUDA的语法和API转换为更通用的形式,这使得相同的代码能够在不同的硬件架构上运行。与CUDA不同,HIP的代码可以被编译为NVCC(NVIDIA CUDA编译器)或HCC(AMD的HIP编译器)。在开发过程中,开发者可以专注于代码的编写,而不必担心目标平台的差异,这在一定程度上简化了代码维护和升级的工作。

HIP也鼓励开发者使用标准的C++特性来编写代码。通过采用C++11或更高版本的特性和编程模式,开发者可以写出更加高效、易于理解和维护的代码。此外,HIP提供了一套丰富的库,例如rocPRIM和rocBLAS,为开发者提供了基本的数值计算功能,从而能够专注于更高级别的算法实现。

总的来说,第一章为读者提供了GPU编程和HIP的基础知识,为理解后续章节中更加深入的技术细节打下了基础。通过理解HIP的初阶概念,开发者可以更好地认识到它在跨平台并行编程中的优势。

# 2. 理解HIP核心概念

在第二章中,我们将深入了解HIP的核心概念,包括编程模型、数据传输与同步机制以及错误处理等关键组成部分。本章旨在为读者提供一个全面且深入的视角,帮助他们理解如何在HIP平台上开发高效、可靠的GPU应用程序。

## 2.1 HIP编程模型

HIP编程模型是设计用来简化GPU编程的抽象层,它允许开发者在不需要深入了解特定GPU架构的情况下编写代码。HIP的核心理念是保持与CUDA的兼容性,同时提供一种机制来支持其他架构,如AMD的GPU。

### 2.1.1 内存管理与访问模式

内存管理是GPU编程中的一个核心问题,直接影响到程序的性能。HIP提供了灵活的内存管理接口,让开发者可以针对不同的内存类型执行操作。

HIP将内存分为以下几种类型:

- 全局内存(Global Memory):所有线程都可以访问的内存区域。

- 共享内存(Shared Memory):线程束内所有线程共享的内存区域。

- 常量内存(Constant Memory):所有线程读取同一数据时,硬件实现高效的广播。

- 私有内存(Private Memory):每个线程访问的私有数据。

**代码示例:**

```cpp

__global__ void memory_example(float *d_in, float *d_out, int size) {

int idx = threadIdx.x + blockDim.x * blockIdx.x;

if (idx < size) {

float temp = d_in[idx];

// 使用共享内存进行数据缓存

extern __shared__ float shared_mem[];

shared_mem[threadIdx.x] = temp;

__syncthreads();

// 此处可以执行一些对shared_mem的同步操作

// ...

d_out[idx] = shared_mem[threadIdx.x];

}

}

```

在本示例中,我们定义了一个内核函数`memory_example`,它通过共享内存来缓存全局内存中的数据。使用`__syncthreads()`函数确保所有线程在继续执行前同步了共享内存的内容。

**逻辑分析和参数说明:**

- `__global__`表示此函数是一个内核函数,在设备上运行。

- `float *d_in, float *d_out, int size`是传递给内核函数的参数,分别代表输入、输出数据和数组大小。

- `threadIdx.x`和`blockIdx.x`是HIP内核中使用的内置变量,代表当前线程的索引和当前块的索引。

- `blockDim.x`表示每个线程块包含的线程数。

- `extern __shared__ float shared_mem[]`声明了一块共享内存,其大小是在启动内核时指定的。

### 2.1.2 核函数(Kernel)的编写与优化

核函数(Kernel)是GPU上执行的核心计算函数,编写高效的核函数对于优化GPU程序至关重要。HIP提供了编写核函数的一套语法,其与CUDA编程模型兼容。

**编写核函数时需要注意的优化策略:**

- 尽量减少全局内存访问的延迟,通过共享内存、常量内存缓存常用数据。

- 调整线程束(Warp)的使用,优化分支指令以避免线程束分化(Branch Divergence)。

- 利用线程束同步指令`__syncthreads()`来控制线程执行流程,以提高数据处理的一致性。

**代码示例:**

```cpp

__global__ void reduce_sum(float *in, float *out, int size) {

extern __shared__ float temp[]; // 分配共享内存

int tid = threadIdx.x;

int i = blockIdx.x * blockDim.x + threadIdx.x;

// 将数据加载到共享内存中

temp[tid] = (i < size) ? in[i] : 0.0f;

__syncthreads();

// 进行归约操作

for (unsigned int s = 1; s < blockDim.x; s *= 2) {

if ((tid % (2*s)) == 0) {

temp[tid] += temp[tid + s];

}

__syncthreads();

}

// 当只有一个线程时,将最终结果写入到输出数组

if (tid == 0) out[blockIdx.x] = temp[tid];

}

```

0

0