【MAX 10 FPGA模数转换器系统集成秘籍】:打造无缝连接的外部设备交互

MAX 10 FPGA模数转换器用户指南

摘要

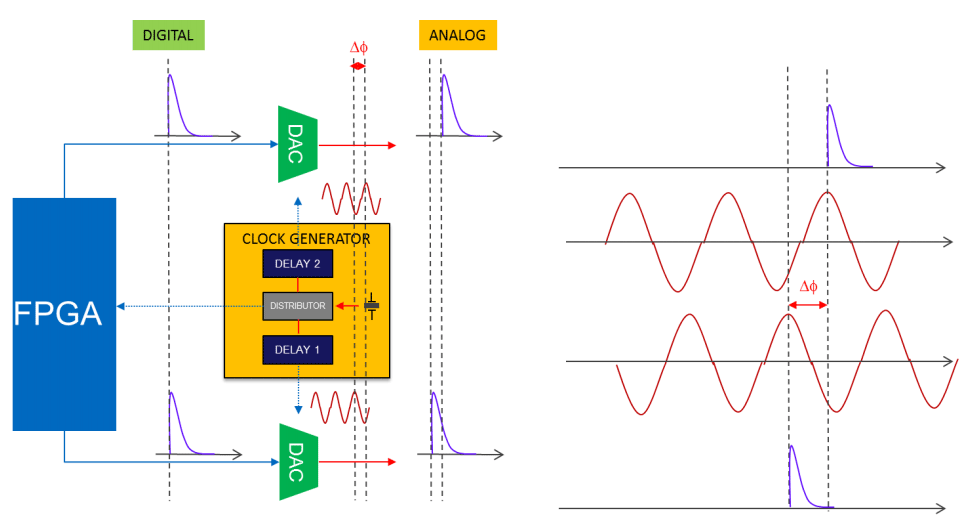

本文详细介绍了MAX 10 FPGA在模数转换器应用中的关键技术和实施方法。首先,文章提供了FPGA模数转换器的基础知识和硬件设计基础,包括FPGA架构、硬件描述语言(HDL)和模拟信号处理技术。其次,探讨了数字信号处理的实现,MAX 10 FPGA内建资源的使用,以及系统集成和优化策略。接着,文章分析了与外部设备交互的通信协议和接口设计,并通过实际案例阐述了应用。最后,讨论了MAX 10 FPGA系统安全与可靠性的关键考量,以及开发工具和调试技术。本文旨在为开发者提供全面的技术指导和案例分析,以促进MAX 10 FPGA在各种应用中的有效利用。

关键字

FPGA;模数转换器;硬件设计;数字信号处理;通信协议;系统安全;调试技术

参考资源链接:Intel MAX 10 FPGA ADC设计与实现指南

1. MAX 10 FPGA模数转换器基础知识

随着数字技术的不断进步,FPGA(现场可编程门阵列)已成为高性能数据处理和信号处理系统的关键组件。其中,模数转换器(ADC)是现代数字系统不可或缺的一部分,负责将模拟信号转换成数字信号以供FPGA处理。在本章中,我们将了解MAX 10 FPGA的基础知识,特别是它如何集成ADC功能以及这项技术的基础应用。

1.1 FPGA的工作原理和架构

FPGA是一种可编程的半导体设备,它由可配置的逻辑块(如查找表、触发器、乘法器等)组成,通过可编程互连来实现复杂的逻辑功能。与传统的ASIC芯片相比,FPGA的优势在于它的可重配置性,这使得设计者可以根据需求快速迭代和更新系统设计。在MAX 10 FPGA的架构中,集成有专用的ADC模块,这可以大幅简化设计复杂度,并减少外部组件的数量。

1.2 模拟信号的采集和预处理

在信号进入FPGA进行数字处理之前,模拟信号需要经过采集和预处理。采集通常涉及到模数转换器(ADC),将连续的模拟信号转换为数字信号。预处理包括滤波和放大,目的是去除不需要的信号成分(如噪声),同时增强有用信号的幅度,确保其在ADC的动态范围内。

1.3 模数转换器(ADC)接口标准

ADC接口标准多种多样,常见的包括串行接口如SPI(Serial Peripheral Interface)和I2C(Inter-Integrated Circuit),以及并行接口。在MAX 10 FPGA中,ADC接口的集成旨在提高系统的集成度和减少系统的整体功耗。例如,MAX 10 FPGA内部的ADC模块可以配置为与FPGA逻辑单元直接连接,从而实现更高效的信号处理。

总结而言,第一章为读者介绍了FPGA在模数转换器领域的基础知识,强调了MAX 10 FPGA与ADC技术的结合,为后续章节的技术细节和实际应用打下基础。

2. 硬件设计与模拟信号处理

2.1 FPGA硬件设计基础

2.1.1 FPGA的工作原理和架构

FPGA(Field-Programmable Gate Array)是一种可以通过编程来配置的集成电路。它们由可编程逻辑块阵列、可配置输入/输出模块和可编程的互连组成。通过使用硬件描述语言(HDL),设计师能够定义这些逻辑块的特定功能,以及它们之间如何相互连接。FPGA的工作原理是基于查找表(LUTs),每个LUT可以实现一个简单的逻辑函数,通过组合LUTs可以构建更为复杂的逻辑电路。

FPGA架构的核心组件包括:

- 逻辑单元(LEs):最基本的构建块,通过配置可以实现各种逻辑运算。

- 可配置的互连:用于连接逻辑单元,可以按照设计需求进行配置。

- 输入输出单元(IOBs):使FPGA能够与其他系统组件通信。

- 嵌入式存储器和乘法器:用于存储数据和执行快速乘法操作。

FPGA相比于其它集成电路,如ASIC或CPLD,提供了更高的灵活性和可重配置性,使得它们适用于需要频繁迭代和快速原型设计的场合。

2.1.2 硬件描述语言(HDL)简介

硬件描述语言(HDL)允许工程师通过文本代码来描述硬件电路。最常用的两种HDL语言是VHDL和Verilog。VHDL起源于欧洲,它在语法上类似于Ada,而Verilog则起源于美国,受C语言影响较大。

HDL代码需要经过综合过程,这个过程会将HDL代码转换成实际的硬件电路。HDL代码通常分为两种风格:

- 数据流风格:通过描述信号如何流经不同的逻辑门来定义电路。

- 行为风格:类似于高级编程语言,通过描述电路应当执行的操作来定义电路。

- module half_adder(a, b, sum, carry);

- input a, b;

- output sum, carry;

- assign sum = a ^ b; // XOR for sum

- assign carry = a & b; // AND for carry

- endmodule

在上述Verilog代码示例中,我们定义了一个半加器模块。该模块有两个输入a和b,输出为求和信号sum和进位信号carry。其中assign语句用于行为风格描述。

2.2 模拟信号的采集和预处理

2.2.1 信号采集的硬件组件

为了将模拟信号转换为数字信号,需要一套硬件组件来完成这个过程,这个过程称为模数转换(ADC)。常见的模拟信号采集硬件组件包括:

- 传感器:检测物理量(如温度、压力、光强等)并转换为电信号。

- 模拟前端:包含放大器、滤波器等,用于对信号进行初步的放大和滤波处理。

- 模数转换器(ADC):将模拟信号转换为数字信号,是信号采集的关键部件。

2.2.2 信号的滤波和放大技术

在将信号送入ADC之前,通常需要先进行滤波和放大处理:

- 滤波:滤除不需要的信号成分,如噪声和干扰,常用的滤波器包括低通、高通、带通和带阻滤波器。

- 放大:根据ADC的输入范围调整信号的幅度,确保信号以最佳的电平范围输入到ADC中。

- // 示例代码:使用Verilog实现一个简单的数字低通滤波器

- module low_pass_filter(input clk, input signed [15:0] signal_in, output signed [15:0] signal_out);

- reg signed [15:0] shift_reg[3:0];

- integer i;

- always @(posedge clk) begin

- for (i = 3; i > 0; i = i - 1) begin

- shift_reg[i] <= shift_reg[i - 1];

- end

- shift_reg[0] <= signal_in;

- // 简单的累加平均滤波算法

- signal_out <= (shift_reg[0] + shift_reg[1] + shift_reg[2] + shift_reg[3]) / 4;

- end

- endmodule

在上述代码中,我们构建了一个简单的数字低通滤波器,它将四个连续样本的平均值作为输出。

2.3 FPGA与模拟信号的接口

2.3.1 模拟到数字转换(ADC)接口标准

FPGA与ADC的接口需要遵循特定的标准,以便两者能够正确地进行数据交换。常见的标准包括:

- SPI(Serial Peripheral Interface):一种常用的串行通信协议,适合高速和低速设备通信。

- I2C(Inter-Integrated Circuit):一种多主多从通信协议,用于连接低速外围设备。

- LVDS(Low Voltage Differential Signaling):一种低电压差分信号技术,适用于高速数据传输。

2.3.2 FPGA内部信号处理逻辑设计

在信号采集后,FPGA将执行内部信号处理逻辑设计,这通常包括:

- 信号的进一步滤波和放大:通过数字滤波器来优化信号质量。

- 信号的重构和解析:对采集的数据进行分析和转换,以满足特定的应用需求。

- // 示例代码:数字滤波器和信号解析的Verilog代码片段

- reg signed [15:0] filtered_signal; // 存储滤波后的信号

- always @(posedge clk) begin

- filtered_signal <= low_pass_filter(signal_in); // 低通滤波后的信号

- // 信号解析逻辑

- if (filtered_signal > THRESHOLD) begin

- signal_out <= 1;

- end else begin

- signal_out <= 0;

- end

- end

此Verilog代码片段实现了一个数字滤波器和一个简单的信号解析逻辑。如果滤波后的信号超过了设定的阈值,输出信号则被设置为高电平。

3. 数字信号处理与MAX 10集成

在现代电子系统设计中,数字信号处理(DSP)技术扮演着至关重要的角色,特别是在FPGA领域。本章节将深入探讨如何在MAX 10 FPGA平台上实现有效的数字信号处理,并介绍系统集成以及优化的策略。