【EDA与FPGA深度结合】:技术理解与实践技巧揭秘

发布时间: 2025-01-10 04:15:39 阅读量: 3 订阅数: 4

复古怀旧教室桌椅素材同学聚会毕业纪念册模板.pptx

# 摘要

本论文旨在探讨电子设计自动化(EDA)工具在现场可编程门阵列(FPGA)开发中的重要作用。文章首先概述了EDA和FPGA的基本概念,随后详细分析了EDA工具在FPGA设计流程中的各个阶段所扮演的角色,包括设计输入、仿真、综合、映射、布局布线以及验证技术。第三章深入探讨了EDA工具在实践应用中的先进技术,如高级语言综合(HLS)、信号完整性与功耗分析、IP核的集成与重用。第四章则专注于性能调优,包括时序约束管理、资源优化和布局布线、以及热管理与电源设计。最后,第五章展望了EDA与FPGA技术的未来发展趋势,强调了人工智能、云计算在EDA中的应用,以及FPGA技术在容错计算、自适应系统、异构集成与多核架构上的创新。本文提出了EDA工具与FPGA结合对于系统级设计和高性能计算领域的长远影响。

# 关键字

EDA;FPGA;设计流程;性能调优;高级语言综合;信号完整性;功耗分析;IP核集成;人工智能;云计算;容错计算;自适应系统;异构集成;多核架构

参考资源链接:[VHDL版《EDA技术实用教程》习题解析与FPGA在ASIC设计中的应用](https://wenku.csdn.net/doc/6412b6d2be7fbd1778d481af?spm=1055.2635.3001.10343)

# 1. EDA与FPGA概述

## 1.1 EDA与FPGA的概念

EDA,即电子设计自动化(Electronic Design Automation),是使用计算机辅助设计软件来设计电子系统,尤其在集成电路和印刷电路板设计领域中不可或缺。FPGA,现场可编程门阵列(Field-Programmable Gate Array),是一种可以通过编程来配置的半导体设备,提供了可重新配置的硬件逻辑。

## 1.2 EDA与FPGA之间的关系

EDA工具为FPGA的开发提供了完整的软件支持环境,涵盖了从设计输入、仿真、综合、实现、到验证的整个开发流程。它使设计师能够高效地对FPGA进行编程和优化,从而实现复杂的功能。

## 1.3 EDA在FPGA开发中的重要性

EDA工具的使用大大缩短了产品从设计到市场的时间,减少了成本,同时提高了设计的可靠性和性能。设计人员可以利用EDA工具实现复杂的硬件功能,进行仿真验证,并优化FPGA设计,确保设计满足时序、资源利用率等多方面要求。

# 2. EDA工具在FPGA开发中的作用

### 2.1 EDA工具基础

#### 2.1.1 EDA工具的定义与分类

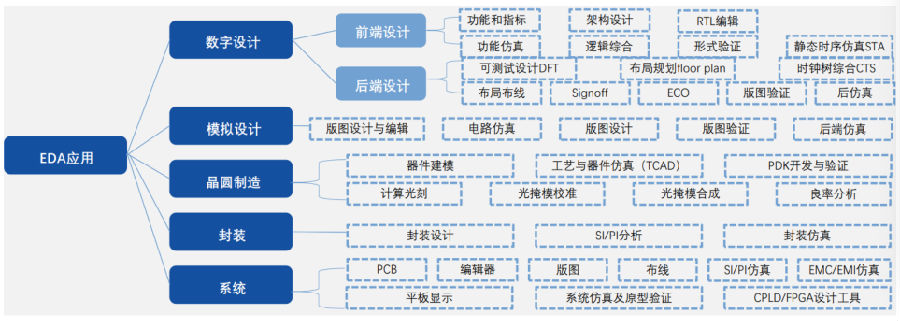

EDA(Electronic Design Automation)工具,是指利用计算机软件来辅助完成电子系统设计的工具。它们包括从设计输入、电路仿真、逻辑综合到最终硬件描述语言(HDL)代码的生成等一系列过程。EDA工具的应用使得电子设计从手工绘制和验证走向自动化、智能化。

EDA工具根据不同的设计阶段和目标可以分为几个主要类别:

- 前端设计工具:包括了逻辑设计和仿真工具,如VHDL或Verilog编写和仿真。

- 综合工具:将HDL代码转换为门级网表的工具,重要的有Xilinx的Vivado,以及Intel的Quartus。

- 布局布线工具:用于确定FPGA内部资源的具体位置,并生成最终的配置文件。

- 后端验证工具:包括静态时序分析、功耗分析等。

- 专用EDA工具:如PCB布局工具、信号完整性分析工具等。

#### 2.1.2 EDA工具与FPGA开发流程

FPGA开发流程通常包含多个步骤,EDA工具贯穿于整个开发流程中。以下是基本的开发流程:

1. 设计输入:使用硬件描述语言(HDL)编写设计。

2. 功能仿真:在编译之前验证逻辑设计的正确性。

3. 逻辑综合:将HDL代码转换为门级网表。

4. 布局布线(Place & Route):确定逻辑元件的物理位置并进行连接。

5. 时序分析与优化:确保设计满足时序要求。

6. 设计验证:使用FPGA进行原型测试,确保设计满足所有功能与性能要求。

7. 配置与调试:将设计下载到FPGA并进行调试。

### 2.2 FPGA设计流程详解

#### 2.2.1 设计输入与仿真

设计输入阶段是FPGA开发的起点。工程师通常使用硬件描述语言(HDL),如VHDL或Verilog来编写设计。这些语言支持高度模块化的代码结构,使得设计易于理解和维护。

功能仿真是在实际硬件配置之前验证逻辑设计正确性的一个重要步骤。仿真工具通常允许模拟不同的硬件环境和条件,如不同的输入信号,以检查设计是否按预期工作。仿真过程可以分为两个主要部分:单元测试和集成测试。单元测试关注单个模块的功能,而集成测试则关注各个模块如何协同工作。

```

// 示例代码:Verilog模块

module adder(

input [3:0] a,

input [3:0] b,

output [4:0] sum

);

assign sum = a + b;

endmodule

// 仿真测试环境

module testbench;

reg [3:0] a;

reg [3:0] b;

wire [4:0] sum;

adder uut(

.a(a),

.b(b),

.sum(sum)

);

initial begin

a = 4'b0000;

b = 4'b0000;

#10;

a = 4'b0010;

b = 4'b0100;

#10;

a = 4'b1111;

b = 4'b0001;

#10;

$finish;

end

endmodule

```

#### 2.2.2 综合、映射与布局布线

综合(Synthesis)阶段将HDL代码转换成门级表示,这是设计流程中的关键一步。综合工具将逻辑描述映射到FPGA的目标架构上。这一过程涉及逻辑优化、技术映射、缓冲插入等操作。

布局布线(Place & Route)是将综合后的逻辑元素放置到FPGA的物理资源中,并为它们之间建立连接。这一过程对性能、时序和资源利用率具有重要影响。布局布线过程需考虑逻辑元素之间的信号传递延迟,以满足时序要求。

```

// 综合工具(如Vivado)使用的关键命令

synth_design -top <top_module> -part <FPGA_part_number> -include和地区布局布线选项

```

#### 2.2.3 时序分析与优化

时序分析是验证电路设计是否满足时钟频率要求的过程。综合和布局布线后的设计需要进行时序分析,以确保所有的时序要求,比如建立时间(setup time)和保持时间(hold time)都被满足。一旦发现时序违例,需要对设计进行优化。常见的优化技术包括调整寄存器位置、插入缓冲器、改变逻

0

0