Cadence Allegro原点重设:设计检查与质量控制要点

发布时间: 2024-12-01 18:58:17 阅读量: 6 订阅数: 19

参考资源链接:[Cadence Allegro软件中重新设置原点的详细步骤](https://wenku.csdn.net/doc/646c2b6a543f844488cf6538?spm=1055.2635.3001.10343)

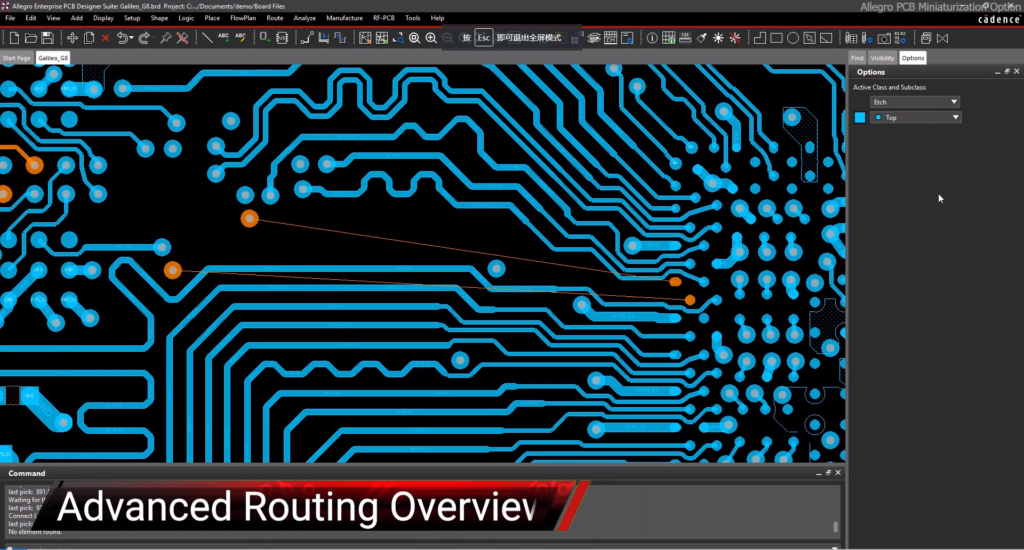

# 1. Cadence Allegro原点重设概述

在使用Cadence Allegro进行PCB设计时,原点重设是确保设计准确性与效率的一个重要步骤。原点,也被称作零点或基准点,是确定坐标系统位置的参考点。掌握原点重设技术,对于提升PCB设计的精确度、简化设计流程以及提高工作效率至关重要。接下来,我们将深入探讨原点重设的理论基础,详细说明其在Cadence Allegro中的操作步骤,并通过案例分析来展示其应用效果,为提高PCB设计质量提供参考。本章节会为读者提供原点重设的基本概念、重要性和操作步骤,以铺垫后续章节更深入的讨论。

# 2. Cadence Allegro设计检查理论基础

## 2.1 设计检查的重要性

### 2.1.1 设计错误的影响

在电子设计自动化(EDA)领域中,设计错误可能会导致项目的失败,从微小的功能障碍到大规模的市场召回。错误的根源可能来自多个方面,包括不准确的设计输入、不恰当的设计规范以及人为的错误。这些错误不仅会影响产品的性能和可靠性,还会增加产品从设计到市场的周期时间,显著提高成本。

电子产品的设计检查,特别是针对印刷电路板(PCB)的设计,是确保产品质量和设计满足规范要求的关键步骤。设计检查包括对设计规则检查(DRC)、电气规则检查(ERC)、以及制造检查(MRC)等的全面分析,这些检查能够帮助设计师识别和修复可能影响最终产品性能的设计缺陷。

### 2.1.2 设计检查的分类与目的

设计检查主要分为以下三类:

1. **设计规则检查(DRC)**:检查PCB设计是否符合预设的制造和布局规则。DRC关注的是物理布局的准确性,如元件间距、走线宽度和钻孔尺寸等。

2. **电气规则检查(ERC)**:验证设计中的电气连接是否符合预定的电气要求。ERC检查电源和地线的连接、元件的电气参数配置是否正确等。

3. **制造检查(MRC)**:确保设计能够适应生产过程。MRC关注制造相关的细节,比如元件的方向、引脚的弯曲度以及焊盘的间距等。

设计检查的目的是确保电路板设计的质量,预防在制造过程中出现意外错误,减少后期的修改成本和时间,从而缩短产品的上市时间,提高产品的可靠性,避免可能的市场风险。

## 2.2 设计规则检查(DRC)深入解析

### 2.2.1 DRC的基本概念

设计规则检查(DRC)是电子设计中用于确保电路板设计符合特定制造和布局要求的过程。DRC检查PCB设计文件,识别违反规则的区域,并提供反馈,以便设计师可以快速修正问题。DRC是自动化执行的,能够显著提高设计效率和准确性,减少设计中的错误。

DRC的规则覆盖广泛,从简单的间距要求到复杂的互连要求,涵盖了设计的多个方面。一旦发现违反规则的情况,DRC系统会生成一个错误列表供设计师参考。这些错误可以是错误的布线、不合理的元件布局或者不符合标准的焊盘设计等等。

### 2.2.2 DRC规则的设置和应用

在使用Cadence Allegro进行PCB设计时,设计者需要首先设置DRC规则。DRC规则定义了布线间距、过孔尺寸、元件间距等设计参数。这些参数是基于PCB制造工厂的能力以及设计规范的要求来制定的。

设置DRC规则通常包括以下几个步骤:

1. **定义制造要求**:设计师根据合作的PCB制造商提供的技术文件,定义制造的最小间距等参数。

2. **创建设计规则文件**:利用Cadence Allegro提供的设计规则编辑器来创建规则文件,设计师可以设置具体的DRC规则。

3. **应用规则到设计**:将制定好的规则文件应用到当前的PCB设计项目中,进行规则检查。

应用DRC规则后,设计师可以利用Allegro提供的工具进行自动检查。任何违反规则的项目都会被列出,并提供详细的信息和位置,以帮助设计师定位和解决问题。

### 2.2.3 DRC常见的错误类型及案例分析

DRC错误的类型多种多样,但可以大致归类为以下几个常见类型:

1. **布线问题**:如线间距太小,可能造成短路,或者布线路径不符合特定的规则要求。

2. **焊盘和过孔问题**:焊盘或过孔尺寸不正确,或者与周围其他对象的间距太小。

3. **元件布局问题**:元件的放置位置违反了设计规范,比如元件过于接近板边或者相互之间距离不够。

4. **层间对齐问题**:在多层PCB设计中,不同层之间的导电图形未正确对齐。

案例分析中,一个常见的DRC错误是在设计中未遵循最小导线宽度要求。比如,某个信号线因为设计考虑被设置得太窄,这可能会导致电流承载能力不足,或者在生产过程中因为蚀刻不均匀而断路。解决这个问题通常需要设计师放大导线宽度,或者更换高电流承载能力的线路。

## 2.3 电气规则检查(ERC)的理论与应用

### 2.3.1 ERC的基础知识

电气规则检查(ERC)是确保电路板设计的电气连接符合预定规则的过程。ERC检查电气设计的完整性,包括元件之间的连接是否正确,以及是否有违反电气规则的不良连接。这一步骤尤其重要,因为电气问题会直接影响电路的功能和产品的可靠性。

ERC涉及的规则包括检查未连接的引脚、电气元件的功率和电压限制、短路和断路等。在Cadence Allegro中,ERC检查是通过一个复杂的算法执行的,它会根据设计规范来验证每个电气连接。

###

0

0