SystemVerilog习题高级篇:深化理解与系统化学习方法

发布时间: 2024-11-29 01:25:38 阅读量: 23 订阅数: 24

STM32之光敏电阻模拟路灯自动开关灯代码固件

参考资源链接:[SystemVerilog验证:绿皮书第三版课后习题解答](https://wenku.csdn.net/doc/644b7ea5ea0840391e5597b3?spm=1055.2635.3001.10343)

# 1. SystemVerilog习题高级篇概述

SystemVerilog作为硬件描述语言的集大成者,已经成为现代数字电路设计与验证的核心技术之一。本章旨在为读者提供对SystemVerilog高级习题的概览,强调从基础概念到实战应用的转变,以及如何在实际的验证项目中有效地运用SystemVerilog语言特性。

SystemVerilog不仅提供了丰富的设计结构和语法,而且在面向对象编程、时序控制、随机化和约束等方面进行了大幅度的扩展和提升,使得验证工程师能够构造更为复杂和高效的测试环境。本章将简要介绍SystemVerilog习题的高级应用,包括面向对象编程、接口与时钟机制、以及随机化和约束等核心主题,为读者深入学习后续章节打下坚实的基础。

# 2. SystemVerilog高级概念解析

## 2.1 类和对象在SystemVerilog中的应用

### 2.1.1 面向对象编程基础回顾

面向对象编程(OOP)是一种强调通过对象来设计程序的编程范式,对象是类的实例,而类是对象的蓝图。在OOP中,数据和函数被封装在对象内部,这使得程序更加模块化,易于维护和重用。封装、继承和多态是OOP的三个核心概念。

封装是将数据(属性)和代码(方法)捆绑在一起,形成一个独立的单元。在SystemVerilog中,类允许封装,以实现数据和操作的结合。

继承提供了一种方式,以便一个类可以继承另一个类的属性和方法。这样可以创建一个通用的基类,并派生出更具体的子类。

多态性允许使用父类类型的引用指向子类的对象,从而允许以统一的方式操作不同的对象类型。SystemVerilog中不直接支持多态,但在UVM(Universal Verification Methodology)中广泛使用了类似多态的行为。

### 2.1.2 SystemVerilog中类和对象的特性

SystemVerilog扩展了Verilog的能力,通过引入类和对象的概念,为设计和验证提供更强大的功能。SystemVerilog的类提供了封装和继承,但不支持全局变量和全局函数,以此来增强模块化。

类可以包含数据成员(变量)和成员函数(方法),可以有构造函数和析构函数来初始化和清理对象。此外,SystemVerilog中的类支持静态成员和常量定义。

SystemVerilog类还支持复制构造函数和赋值操作符的重载,使得对象间的复制和赋值更加灵活。

### 2.1.3 实例与继承在验证环境中的实践

在验证环境中,类和对象的实例化以及继承通常用于创建灵活的、可重用的组件。例如,在UVM验证环境的构建中,可以创建一个基类来定义共用的属性和方法,然后通过继承来创建特定的测试组件。

继承允许我们通过创建子类来增加或修改父类的行为。这在创建不同的测试案例时非常有用,因为它们可以共享一些相同的验证逻辑,但是也可以有自己特定的配置和行为。

此外,UVM中使用到的工厂模式,正是继承的典型应用,它允许在运行时动态地创建测试组件的实例,从而在不修改代码的情况下,实现灵活的测试配置。

## 2.2 SystemVerilog的高级接口和时钟机制

### 2.2.1 接口的高级用法与建模

在SystemVerilog中,接口是一个可复用的模块,可以包含信号、任务、函数、连续赋值语句和参数。高级接口通常用于简化模块间的通信,并可以在接口中实现复杂的协议。

高级接口可以封装协议逻辑,使得测试环境更加模块化,例如,可以在一个接口模块中实现AXI总线协议的细节,然后在需要该协议的测试模块中简单地引用该接口。

### 2.2.2 时钟域交叉分析与解决方案

时钟域交叉(CDC)是指在不同时钟域之间传递信号时出现的问题。CDC问题可能导致数据丢失、数据损坏或竞争条件,是数字设计中的常见问题。

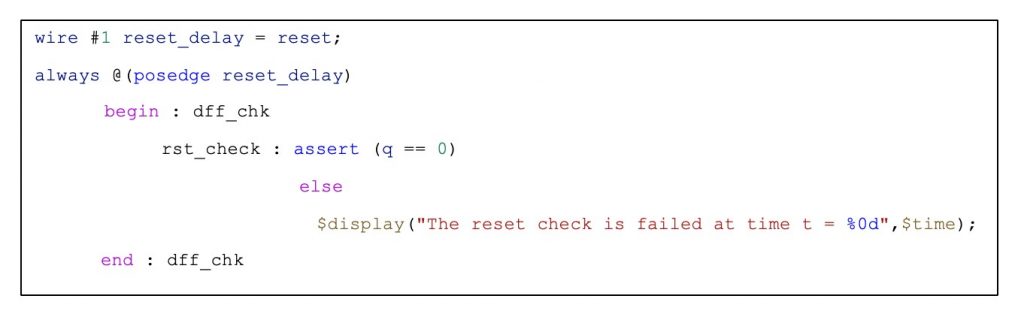

在SystemVerilog中,可以使用高级接口和内置的时钟域交叉检测机制来分析和解决CDC问题。在验证阶段,可以使用断言来检测违反时钟域规则的信号变化。

### 2.2.3 系统时钟和虚拟时钟的管理

系统时钟是硬件设计中的实际时钟信号,而虚拟时钟则是为了模拟真实时钟信号的行为,通常在仿真环境中使用。在SystemVerilog中,可以使用内置的时钟生成机制和时钟切换语句来管理这些时钟。

虚拟时钟可以在测试环境里模拟时钟的延迟、抖动和偏斜等特性,从而更真实地模拟硬件的行为。这有助于发现设计中可能由于时钟问题而引发的错误。

## 2.3 SystemVerilog的随机化和约束技术

### 2.3.1 随机数生成与类型

SystemVerilog提供了强大的随机化支持,允许生成随机的整数、实数、布尔值、数组等类型的随机值。这在生成测试用例时非常有用,特别是对复杂的数据结构和协议进行验证时。

系统随机数生成器可以生成指定范围内的随机值,而且可以通过约束来进一步指导随机化过程,以确保生成的值满足特定的条件。

### 2.3.2 约束的定义和应用

约束是SystemVerilog的一个高级特性,允许用户定义一组规则,用于指导随机数生成器选择值。约束使得生成的随机数据更加贴近实际使用场景。

约束可以是简单的范围限制,也可以是复杂的条件表达式,它们可以对单个变量定义,也可以定义在对象上,对多个相关变量一起约束。

### 2.3.3 随机化在测试用例中的实践

在SystemVerilog的测试用例中,随机化可以极大地提高测试覆盖率,因为随机化的数据可以覆盖设计中更多的边界条件和异常情况。

实现随机化的测试用例通常涉及到设置合适的约束,以确保生成的数据是有效的,并且能够覆盖到设计的各个方面。通过精心设计的约束,可以保证测试的效率和质量。

```systemverilog

class packet;

rand bit[7:0] data;

rand bit[3:0] addr;

constraint valid_addr { addr < 10; }

endclass

module testbench;

initial begin

packet p = new();

for (int i = 0; i < 10; i++) begin

assert(p.randomize()) else $display("Randomization failed");

$display("Data = %0d, Address = %0d", p.data, p.addr);

end

end

endmodule

```

在上述代码中,`packet` 类定义了两个随机成员变量 `data` 和 `addr`,以及一个约束 `valid_addr` 限制 `addr` 的范围。在 `testbench` 模块中,通过循环随机化 `packet` 对象并打印其成员值,实现了随机化在测试用例中的应用。如果随机化失败,则会输出错误信息,表明约束可能过于严格或存在矛盾。

# 3. SystemVerilog实战技巧提升

SystemVerilog是一门强大的硬件描述语言,它在集成电路设计和验证领域中扮演了至关重要的角色。掌握了SystemVerilog不仅可以提升设计的效率,还能提高验证的准确性和覆盖率。第三章将从实战角度出发,探讨如何通过SystemVerilog提升测试平台的构建效率,使用断言和覆盖率分析来优化验证过程,以及验证环境的优化与调试技巧。

## 3.1 高效的SystemVerilog测试平台构建

构建一个高效的SystemVerilog测试平台需要考虑多个方面,包括模块化设计、使用钩子(Hooks)和分层结构,以及事务级建模(TLM)的灵活运用。

### 3.1.1 测试平台的模块化设计

模块化设计可以将复杂的问题分解为更易管理的小部分。在SystemVerilog测试平台中,模块化意味着将测试平台分为多个子模块,每个模块负责验证过程中的一个特定方面。例如,可以创建一个负责生成激励的模块,一个负责监控DUT(Design Under Test)输出的模块,以及一个用于记录和分析测试结果的模块。

模块化设计的好处在于:

- 提高代码的可维护性和可重用性

- 易于定位问题和进行调

0

0