【高级RISC-V指令开发】:实战案例与技巧全解析

发布时间: 2025-01-08 17:40:50 阅读量: 4 订阅数: 5

ARM嵌入式系统开发:软件设计与优化

# 摘要

本文全面介绍了RISC-V指令集架构,涵盖了基础指令开发、高级指令开发实战、并行性分析以及在不同领域的应用。RISC-V指令集架构以其开源、模块化的特点,在学术研究和商业应用中受到广泛关注。文章首先概述了RISC-V的基础概念与组成,继而深入探讨了基础指令集的开发和汇编语言,为读者提供深入理解的基础。在此基础上,介绍了高级指令的开发方法、性能优化技巧以及并行处理的概念,强调了RISC-V在提高系统性能和效率方面的潜力。特别地,本文还分析了RISC-V在安全加密、物联网、边缘计算、人工智能和机器学习等领域的应用,以及行业发展趋势、技术挑战、机遇和社区商业支持,展望了RISC-V指令集的未来前景。

# 关键字

RISC-V指令集;基础指令开发;并行性分析;高级指令实战;技术标准化;跨学科创新

参考资源链接:[RISC-V自定义指令在LLVM中的玄铁C910实现与扩展](https://wenku.csdn.net/doc/4p7zn5y4bo?spm=1055.2635.3001.10343)

# 1. RISC-V指令集架构概述

## 1.1 RISC-V的起源与理念

RISC-V是一种开源指令集架构(ISA),最初由加州大学伯克利分校的研究团队发起。它代表了“第五代精简指令集计算机”(Reduced Instruction Set Computer, RISC),是RISC系列指令集的最新成员。RISC-V设计的核心理念是简单、模块化和可扩展性。这使得它能够适应从小型嵌入式系统到超级计算机等各种不同的应用场景。

## 1.2 RISC-V的优势

RISC-V指令集的最大优势在于其开源和免费的特性,这为硬件设计者提供了极高的自由度。与传统的专有指令集不同,任何组织和个人都可以在遵循相应的许可协议的前提下,使用、扩展甚至定制RISC-V指令集。此外,RISC-V的模块化设计允许实现者仅选择所需的指令集组件,从而实现更轻量级的设计。

## 1.3 RISC-V指令集的构成

RISC-V指令集由基本整数指令集(RV32I, RV64I, RV128I)和各种可选的扩展指令集组成,这些扩展指令集支持浮点运算、原子操作、压缩指令等。这些指令集模块化的设计让RISC-V成为一个高度灵活且易于适应不同计算需求的平台。

```mermaid

graph TD;

A[RISC-V指令集] --> B[基础整数指令集]

B -->|包含| C[RV32I]

B -->|包含| D[RV64I]

B -->|包含| E[RV128I]

A --> F[可选扩展指令集]

F -->|包含| G[浮点指令集(FDIV/FSQRT)]

F -->|包含| H[原子指令集]

F -->|包含| I[压缩指令集]

```

RISC-V指令集的灵活性和扩展性使其在学术界和工业界都受到了广泛关注,预示着它在未来计算领域将扮演越来越重要的角色。

# 2. RISC-V基础指令开发

## 2.1 RISC-V指令集的组成

### 2.1.1 基本指令介绍

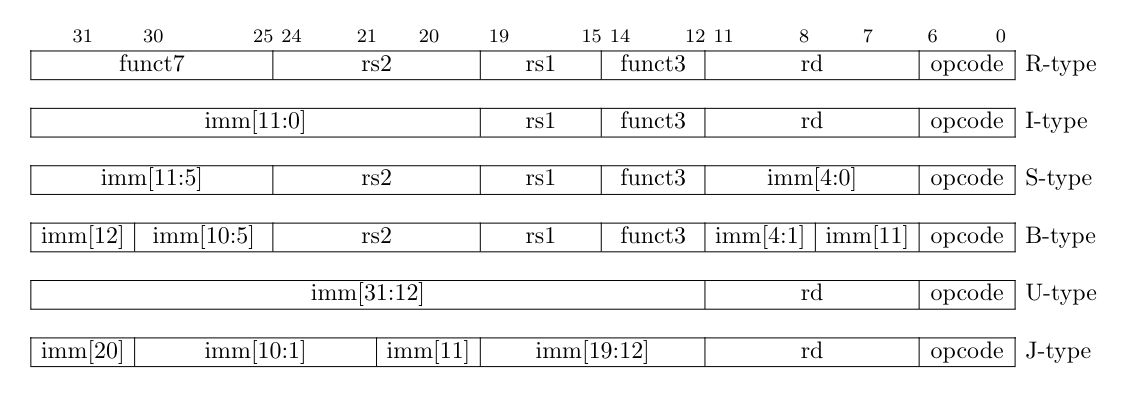

RISC-V指令集架构的核心理念是简单且易于实现,因此它包含了一组精简的基础指令。基础指令集包括对整数和布尔运算的支持,这是构建更复杂操作的基石。RISC-V指令集中有三大类基本指令:R型(寄存器-寄存器操作)、I型(立即数-寄存器操作)和J型(跳转操作)。

以R型指令为例,它通常包括操作码(opcode)、两个寄存器操作数(rs1和rs2),以及一个目的寄存器(rd)。这样的设计简化了处理器内部的数据路径,并使得指令的译码和执行过程更为高效。下面是一个简单的R型指令的例子:

```asm

add rd, rs1, rs2 # 将寄存器rs1和rs2中的数值相加,结果存入rd寄存器

```

RISC-V还设计了I型指令来处理立即数与寄存器之间的操作,这对于需要常数操作的场景非常有用,例如加载立即数到寄存器或者对寄存器值进行简单的算术运算。

### 2.1.2 控制流指令分析

控制流指令用于改变程序执行的顺序,是构成程序逻辑的另一个重要组成部分。在RISC-V中,控制流指令主要涉及跳转(J型)和分支(B型)操作。跳转指令用于无条件的跳转到程序的另一个位置,通常用于函数调用、循环的开始等场景。分支指令则用于条件跳转,它会根据一个条件判断的结果决定是否跳转,比如if-else结构、循环的继续和结束等。

例如,条件分支指令`beq`会比较两个寄存器中的值,如果相等则跳转到指定的位置:

```asm

beq rs1, rs2, label # 如果rs1和rs2的值相等,则跳转到标签label处

```

RISC-V指令集中还包含了一系列的系统级指令,用于提供操作系统和程序之间的接口。这类指令允许程序执行特权级别的操作,如读取和修改状态寄存器等。

## 2.2 RISC-V汇编语言基础

### 2.2.1 汇编语法规则

RISC-V的汇编语言遵循一定的语法规则,确保了代码的可读性和易于编写。首先,一条基本的RISC-V汇编指令通常具有如下的形式:

```asm

[标签:] 操作码 助记符 参数[, 参数]...

```

这里的标签是可选的,它为指令提供了名称,使得跳转指令可以引用它。操作码描述了要执行的基本操作,助记符是操作码的象征性表示,参数则进一步定义了操作的具体内容。

一条指令可能拥有零个或多个参数,这些参数通常包括寄存器名、常数(立即数)以及跳转目标的标签。值得注意的是,RISC-V汇编语言中的所有数据,无论大小,都必须以十六进制或者十进制的形式明确给出。

### 2.2.2 寄存器和内存操作

在RISC-V汇编语言中,对寄存器和内存的操作是基础且频繁的操作。寄存器的名称遵循`x0`到`x31`的命名规则,其中`x0`是硬编码为0的寄存器,其他则可以进行各种运算。

对内存的操作,主要通过加载(load)和存储(store)指令来完成。加载指令将内存中的数据载入寄存器,而存储指令则是将寄存器中的数据写入内存。例如,加载一个字(word,通常为4字节)到寄存器`x1`的操作如下:

```asm

lw x1, offset(base)

```

这里,`offset`是相对于基址寄存器`base`的偏移量,`lw`指令表示加载字大小的数据。

存储操作类似,只不过使用`sw`指令(store word):

```asm

sw x1, offset(base)

```

这里,将寄存器`x1`中的数据存储到由`base`寄存器加上`offset`偏移量所指定的内存位置。

## 2.3 开发环境与工具链

### 2.3.1 工具链安装与配置

为了能够开发RISC-V程序,首先需要搭建一套完整的开发环境和工具链。RISC-V的工具链通常包括编译器(如GCC)、汇编器、链接器以及调试器等。这些工具的安装和配置对于初次接触RISC-V的开发者来说可能会稍显复杂,但一旦设置完成,就可以高效地进行程序的编写、编译、链接和调试。

以基于Linux环境的RISC-V工具链安装为例,可以通过以下步骤进行:

1. 安装必要的依赖工具和库。

2. 下载RISC-V工具链源码。

3. 编译并安装RISC-V工具链。

以下是具体的命令序列:

```bash

sudo apt-get install autoconf automake autotools-dev curl libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev libexpat-dev

git clone https://github.com/riscv/riscv-gnu-toolchain

cd riscv-gnu-toolchain

./configure --prefix=/opt/riscv --with-arch=rv32imac --with-abi

```

0

0