深入掌握Quartus II:5个关键步骤带你走完整个FPGA设计流程

发布时间: 2024-12-21 19:32:23 阅读量: 7 订阅数: 11

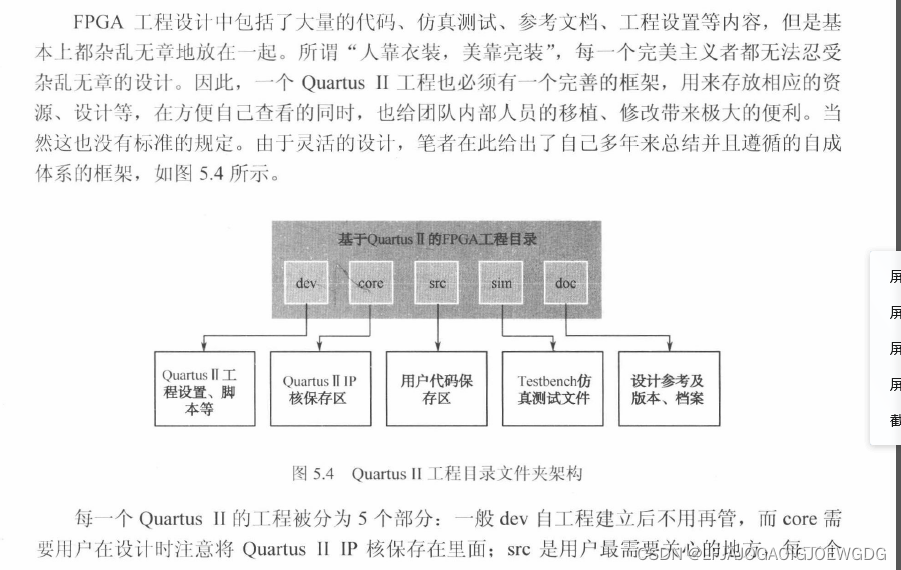

基于QuartusII+FPGA 进行计算机组成原理课程设计实验【100013091】

# 摘要

本文详细介绍了Quartus II软件在FPGA设计中的应用及其重要性。首先,文章概览了Quartus II的功能和在FPGA设计流程中的作用。随后,具体阐述了如何在Quartus II中进行项目设置、逻辑设计、仿真以及综合与布局布线等关键步骤,强调了设计文件管理和时序分析优化的必要性。最后,通过实例展示了Quartus II在实际项目中的应用,并提供了一些问题解决的策略。本文不仅为初学者提供了一个全面的入门指南,同时也为经验丰富的设计工程师提供了一些高级技巧和最佳实践。

# 关键字

Quartus II;FPGA设计;项目管理;逻辑设计;仿真;综合;布局布线;时序优化

参考资源链接:[QuartusII 版本说明](https://wenku.csdn.net/doc/647fdc3d543f8444883c5ae3?spm=1055.2635.3001.10343)

# 1. Quartus II简介及其在FPGA设计中的作用

Quartus II是由Altera公司开发的一款行业领先的FPGA设计软件,提供了从设计输入、综合、优化到最终配置下载的完整解决方案。作为一款功能强大的工具,Quartus II在复杂度不断提升的FPGA设计中起到了核心作用,无论是对于初学者还是资深工程师,它都是不可或缺的设计工具。

## 1.1 FPGA设计流程概述

在进入深入讨论Quartus II之前,让我们先简单回顾FPGA的设计流程。FPGA的设计通常包括以下几个主要步骤:

- **设计输入:** 在这一阶段,设计者通过HDL(硬件描述语言)如Verilog或VHDL编写代码来描述所需的硬件功能。

- **仿真验证:** 设计的代码需要通过仿真工具进行验证,以确保在硬件实现之前功能正确。

- **综合:** 将HDL代码综合成FPGA内部的逻辑元件表示,生成适合特定FPGA结构的网表文件。

- **布局布线:** 综合后的逻辑元件被放置在FPGA芯片上,并通过布线完成元件之间的连接。

- **时序分析与优化:** 这是确保设计满足时序要求的关键步骤。

- **配置与下载:** 最后,设计被加载到FPGA芯片中并进行实际测试。

## 1.2 Quartus II的作用

Quartus II在上述设计流程中扮演着至关重要的角色。其主要功能和作用包括但不限于以下几点:

- **项目管理:** Quartus II提供了项目管理工具,方便设计者组织和管理他们的设计文件、源代码以及资源。

- **综合与仿真:** 它内置综合引擎,能够将HDL代码转换为FPGA的逻辑元件。同时,Quartus II支持功能和时序仿真,帮助开发者在实际硬件之前验证设计。

- **布局布线:** Quartus II能够自动处理布局布线过程,并根据设计需求和FPGA结构优化布线。

- **时序优化:** 它的分析工具可以帮助开发者理解设计的时序问题,并提供优化建议。

- **配置与调试:** 支持生成FPGA配置文件,并提供硬件调试工具。

随着FPGA技术的不断发展,Quartus II也在不断地更新和改进,以满足日益增长的设计复杂度和更高的性能要求。通过熟练掌握Quartus II,工程师可以更高效地设计和实现复杂FPGA项目。

# 2. Quartus II项目设置与初始配置

## 2.1 创建Quartus II项目

### 2.1.1 设计文件的组织结构

在开始任何项目之前,有条理的组织设计文件是至关重要的。在Quartus II中,项目文件通常包含以下几个部分:

- **源文件**:这是设计师所编写的Verilog或VHDL代码,以及它们可能依赖的任何库文件或模块。

- **项目文件**:Quartus II使用一个项目文件来保存项目的所有设置和信息。它通常有.qpf扩展名。

- **符号文件**:.sdc扩展名的文件用于定义时序约束,指导布局布线过程。

- **输出文件**:这些是在编译过程中由Quartus II生成的报告和二进制文件,如编程文件和网表文件。

**项目目录结构示例**:

```

ProjectName/

|-- source/

| |-- modules/

| | |-- module1.v

| | |-- module2.vhd

| | `-- ...

| `-- top_module.sv

|-- QuartusProjectFiles/

| |-- ProjectName.qpf

| `-- ProjectName.sdc

`-- output_files/

`-- ProjectName.rpt

```

### 2.1.2 项目设置的详细步骤

创建Quartus II项目的详细步骤如下:

1. **启动Quartus II软件**。

2. **选择 "File" > "New Project Wizard"** 打开项目向导。

3. **指定项目名称和位置**。选择一个合适的位置来保存项目文件。

4. **添加源文件**。如果已有一些设计文件,可以在此步骤中添加它们。

5. **选择目标设备**。根据需要选择一个FPGA芯片型号。

6. **指定仿真文件**。如果需要,可以选择仿真工具和仿真文件。

7. **完成**。向导会自动生成项目文件,这包括.qpf和.qsf文件。

## 2.2 设定FPGA芯片参数

### 2.2.1 选择合适的FPGA芯片型号

选择正确的FPGA芯片型号是项目成功的关键因素之一。在Quartus II中选择芯片型号时,需要考虑以下几点:

- **引脚兼容性**:确保所选芯片与设计板兼容。

- **性能需求**:根据项目对速度和资源的需求来选择芯片。

- **成本**:根据项目的预算选择性价比最高的芯片。

**芯片选择流程**:

1. 打开Quartus II软件。

2. 选择 "Assignments" > "Device" 来打开设备设置对话框。

3. 在 "Family" 下拉菜单中选择合适的芯片系列。

4. 在 "Device" 下拉菜单中选择具体的芯片型号。

### 2.2.2 配置引脚和时钟设置

在Quartus II中,可以通过引脚规划器(Pin Planner)来配置引脚和时钟设置。

**配置步骤**:

1. 打开引脚规划器:选择 "Assignments" > "Pin Planner"。

2. 配置引脚I/O标准、位置和其他属性。

3. 为时钟信号分配专用引脚,并设置时钟频率。

**示例代码**:

```tcl

# 在.qsf中设置引脚位置的TCL命令

set_location_assignment PIN_<location> -to <signal_name>

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to <signal_name>

```

## 2.3 设计文件的管理

### 2.3.1 版本控制与项目备份

设计文件的版本控制和备份是项目管理的关键组成部分。Quartus II支持与常见的版本控制系统集成,例如SVN或Git。

**集成步骤**:

1. 在Quartus II中选择 "Tools" > "Options"。

2. 在 "Version Control" 部分配置版本控制设置。

此外,定期备份项目是一个好习惯。Quartus II允许通过简单的文件复制来备份整个项目目录。

### 2.3.2 库文件与模板的使用

在Quartus II中,库文件和模板可以用来加快设计的创建和管理。库文件通常包含常用模块或函数,可以被多个项目共享。

**使用模板**:

1. 在创建新项目时选择 "Use existing project as a template" 选项。

2. 从模板中选择适合当前项目的预设参数和文件。

**示例代码**:

```tcl

# 使用TCL命令创建一个新项目并从模板创建

create_project MyProject ./MyProject -template MyTemplate.qpt

```

通过这些步骤,设计者可以高效地管理项目文件,保证设计流程的顺畅和效率。在下一章节,我们将深入探讨Quartus II中的逻辑设计和仿真过程,这是保证设计正确性的关键步骤。

# 3. Quartus II中的逻辑设计与仿真

随着数字逻辑设计复杂性的增加,使用先进的工具进行设计仿真变得至关重要。在本章节中,我们将深入探讨Quartus II中逻辑设计与仿真的核心环节,包括设计输入、功能仿真与验证以及时序仿真与优化。理解并掌握这些知识,将有助于设计者更高效地完成设计任务,缩短产品上市时间,并减少在硬件实现中遇到的问题。

## 3.1 HDL编写与设计输入

### 3.1.1 Verilog与VHDL的编写规范

硬件描述语言(HDL)是进行数字系统设计的重要工具。在Quartus II中,Verilog和VHDL是最常用的两种HDL。编写符合规范的HDL代码,不仅能提升代码的可读性和可维护性,还能提高仿真和综合的效率。

Verilog和VHDL都有各自的编码习惯和规范。以Verilog为例,良好编程习惯包括:

- 使用一致的缩进和格式化标准。

- 将模块分解为小的、可管理的块。

- 使用描述性名称来标识信号、模块和端口。

- 在模块顶部声明所有端口和参数。

- 尽量避免使用延时语句(如 `#`)进行仿真,而应使用阻塞和非阻塞赋值语句。

```verilog

module adder (

input [3:0] a,

input [3:0] b,

output reg [4:0] sum

);

always @ (a or b) begin

sum = a + b; // 非阻塞赋值

end

endmodule

```

上述代码展示了如何定义一个4位加法器的Verilog模块。代码注释指出使用了非阻塞赋值操作,这对于仿真和综合都至关重要。

### 3.1.2 设计模块的划分与接口定义

在进行复杂的FPGA设计时,将设计划分为多个模块,并定义清晰的接口,不仅可以提升代码的复用性,还利于团队协作。一个模块化的设计允许各个模块独立开发和测试,降低了整体设计的复杂度。

模块接口定义了模块如何与其他部分交互,包括输入输出端口。良好的接口定义应当尽量简洁明了,易于理解和使用。

```verilog

module top_level (

input wire clk,

input wire rst_n,

input wire [7:0] data_in,

output reg [15:0] data_out,

output reg ready

);

// 模块声明和定义

// ...

endmodule

```

上述代码展示了一个顶层模块的接口定义,包括一个时钟输入、复位信号和数据输入输出。这为后续的逻辑实现和接口连接奠定了基础。

## 3.2 功能仿真与验证

### 3.2.1 编写测试平台进行仿真

功能仿真是在综合之前验证HDL代码逻辑正确性的关键步骤。测试平台(testbench)是一个不包含输入输出端口的特殊模块,它用于生成模拟信号并观察设计输出的响应。

在Quartus II中,测试平台通常会使用Verilog或VHDL编写。其主要工作是创建测试激励(test stimuli),即输入信号序列,并验证输出是否符合预期。

```verilog

`timescale 1ns / 1ps

module testbench;

// 信号声明

reg clk;

reg reset;

reg [7:0] data_in;

wire [15:0] data_out;

// 实例化设计模块

top_level uut (

.clk(clk),

.rst_n(reset),

.data_in(data_in),

.data_out(data_out)

);

// 生成时钟信号

initial begin

clk = 0;

forever #10 clk = ~clk; // 产生50MHz的时钟信号

end

// 生成测试激励

initial begin

// 初始化

reset = 0;

data_in = 0;

#20;

reset = 1;

#20;

// 应用测试数据

data_in = 8'hAA; // 应用输入数据

#20;

data_in = 8'h55;

#20;

// 更多测试数据...

// 完成测试

$finish;

end

endmodule

```

上述测试平台的Verilog代码展示了如何生成时钟信号、复位信号和输入数据。它还包含了一个结束测试的条件。测试平台的目的是为了验证顶层模块 `top_level` 的功能。

### 3.2.2 仿真结果的分析与调试

仿真完成后,需要对结果进行分析,以确定设计是否满足功能需求。如果发现错误或不符合预期的行为,就需要对设计代码进行调试。

仿真结果的分析通常使用波形查看器进行。Quartus II提供了内置的波形查看器,能够直观地展示设计的输入输出波形。

如果需要调试,可以在测试平台中添加额外的语句来打印变量的值,或者使用波形查看器的标记功能来跟踪特定时刻的数据状态。通过逐步修改代码并重新仿真,最终使得设计满足预期功能。

## 3.3 时序仿真与优化

### 3.3.1 理解时序分析工具

时序分析是确保设计在FPGA上运行可靠性的关键环节。Quartus II提供的时序分析工具帮助设计者识别和解决时序问题,包括设置时间(setup time)和保持时间(hold time)违规。

理解并掌握这些时序分析工具,如TimeQuest时序分析器,对于任何希望在FPGA上实现高性能设计的工程师来说都是必须的。TimeQuest能够提供详尽的时序报告和时序图,帮助设计者识别潜在问题。

### 3.3.2 应对时序约束和优化策略

在面临时序问题时,设计者可以使用Quartus II提供的优化策略,例如添加管道寄存器(pipelining)、调整布局和布线设置、或直接修改HDL代码。在添加管道级数时,需注意不要过度增加,以免增加设计的延迟和面积。

修改HDL代码时,需要考虑影响时序的逻辑结构,例如避免长路径和复杂的组合逻辑。设计者需要根据时序分析结果逐步调整设计,直到满足所有时序约束。

```verilog

// 一个使用管道寄存器的示例代码

module pipeline_adder (

input clk,

input [3:0] a,

input [3:0] b,

output reg [4:0] sum

);

reg [3:0] a_reg, b_reg;

reg [4:0] sum_reg1, sum_reg2;

always @ (posedge clk) begin

a_reg <= a; // 第一级管道寄存器

b_reg <= b;

sum_reg1 <= a_reg + b_reg; // 第一级加法器

sum_reg2 <= sum_reg1; // 第二级管道寄存器

sum <= sum_reg2; // 输出

end

endmodule

```

上述代码引入了两级管道寄存器,以减少因组合逻辑引起的时序问题。每个阶段的数据传输都与时钟边沿同步,有效缓解了时序压力。

通过掌握Quartus II中的逻辑设计与仿真,设计者能够在设计阶段更早地发现和解决问题,从而提高设计质量,缩短开发周期。在接下来的章节中,我们将继续探讨Quartus II中的综合与布局布线,以及在实际项目中的应用,深入理解整个FPGA设计流程。

# 4. Quartus II中的综合与布局布线

## 4.1 综合过程概述

### 4.1.1 逻辑综合的目标与挑战

逻辑综合是将硬件描述语言(HDL)编写的高级逻辑设计转换为门级网表的过程,该网表与特定的FPGA或ASIC设备兼容。在Quartus II中,逻辑综合的目标不仅是将设计准确地映射到硬件资源,还涉及优化以满足时序、面积和功耗等方面的要求。为了实现这些目标,综合过程中存在多个挑战,包括:

- **设计复杂性**:现代FPGA可以包含数百万个逻辑元件,管理这样的规模要求综合工具具有高度的智能化。

- **时序约束**:设计必须满足严格的时序要求,综合工具必须确保满足这些要求,而不会过度增加硬件资源使用。

- **资源限制**:综合过程中需考虑到目标FPGA的资源限制,优化逻辑以减少资源使用,同时保持性能。

- **功耗**:在便携式或功耗敏感的应用中,减少功耗是综合过程的一个重要考虑因素。

### 4.1.2 综合工具的选择与配置

Quartus II 提供了多种综合工具,包括 Altera 自家的综合解决方案以及支持第三方综合工具,如 Synopsys 的 Design Compiler 或 Mentor Graphics 的 Precision RTL Plus。选择合适的综合工具对于成功实现设计至关重要。以下是配置综合工具的步骤:

- **选择综合工具**:根据项目需求和FPGA器件特性选择最合适的综合工具。

- **定义综合策略**:明确优化目标,例如,优化是否针对时序、面积或功耗。

- **设置综合参数**:根据设计复杂性和资源限制调整综合参数,如优化级别、逻辑合成尝试次数和资源分配。

- **编译设置**:通过Quartus II 的编译设置窗口配置综合工具选项。

```mermaid

graph TD

A[开始综合] --> B[选择综合工具]

B --> C[定义综合策略]

C --> D[设置综合参数]

D --> E[进行编译]

E --> F[综合结果分析]

```

## 4.2 布局布线的原理与技巧

### 4.2.1 布局布线的重要性与影响因素

布局布线(Place & Route,P&R)是将综合生成的网表映射到FPGA的物理硬件资源上的过程。P&R对于设计的时序性能和资源使用效率有着决定性的影响。布局和布线的重要性体现在以下几个方面:

- **时序性能**:P&R过程决定了信号在FPGA内传输的路径长度和阻抗,直接影响信号的传输时间和时序性能。

- **资源利用率**:有效的布局可以减少资源浪费,同时避免资源冲突。

- **热分布**:在功耗较高的设计中,P&R还需要考虑热分布,避免局部过热。

布局布线的影响因素包括:

- **逻辑单元的分布**:逻辑单元的分布需要平衡,避免拥挤。

- **I/O位置和时钟网络**:对I/O引脚的布局和时钟树的布线非常关键,它们决定了信号的完整性和时钟的准确性。

- **信号完整性**:在布线过程中要考虑信号的串扰和反射等问题。

### 4.2.2 解决布局布线中的常见问题

在布局布线过程中,工程师可能会遇到一系列问题,比如时序违规、资源分配不均或布线拥堵。解决这些问题的技巧包括:

- **使用Quartus II分析工具**:使用 Timing Analyzer 检查时序,使用 Chip Planner 观察布局状态。

- **手动调整**:在必要时,工程师可以通过图形界面手动调整布局,或为关键路径指定布线资源。

- **优化设置**:重新调整综合和布局布线的优化设置,例如,减少综合的优化程度来获取更多的布局布线资源。

## 4.3 设计的时序闭合与优化

### 4.3.1 时序闭合的策略与方法

时序闭合(Timing Closure)是指设计在满足时序要求的前提下,经过综合和布局布线后达到稳定状态。时序闭合是设计流程中的一个关键步骤,涉及以下策略与方法:

- **优化目标设定**:基于设计要求,设定合理的时序和面积优化目标。

- **执行时序驱动综合**:使用时序驱动的综合选项,确保综合阶段就考虑到时序约束。

- **综合后优化**:通过时序分析工具的反馈,进行综合后优化,解决时序违规问题。

### 4.3.2 后综合仿真与分析

完成综合和布局布线后,进行后综合仿真(也称时序仿真)是检验设计是否达到时序要求的重要步骤。后综合仿真不仅包括功能的验证,还包含对时序的验证。分析时序报告并调整设计来满足时序要求的步骤如下:

- **运行时序仿真**:使用ModelSim等仿真工具进行后综合仿真。

- **检查时序报告**:重点检查建立时间和保持时间违规,以及路径延迟。

- **调整和优化**:根据时序报告的提示对设计逻辑或布局布线进行调整,然后重新进行仿真和分析。

```mermaid

flowchart LR

A[综合完成后] --> B[运行时序仿真]

B --> C[生成时序报告]

C --> D[检查建立时间和保持时间]

D --> E[调整设计]

E --> B

```

通过以上步骤,我们可以确保设计满足时序要求并且可以在目标FPGA上稳定运行。时序闭合是迭代过程,可能需要反复的综合、布局布线、仿真和优化来达成目标。

# 5. Quartus II在实际项目中的应用与问题解决

## 5.1 下载与配置FPGA

### 5.1.1 下载链的建立与配置

在Quartus II中配置FPGA下载链是为了确保设计能够成功地被下载到目标FPGA芯片上。这涉及到使用适当的编程硬件接口以及配置软件。配置过程如下:

1. **选择编程器**:首先,根据项目需求选择合适的编程器,常见的有USB-Blaster、USB-Blaster II等。

2. **连接硬件**:确保编程器正确连接到开发板的JTAG接口上。

3. **软件配置**:在Quartus II软件中,选择"Tools" > "Programmer"进入编程器界面。

4. **创建下载链配置文件**:点击"Auto Detect"自动检测硬件配置,或手动添加相应的设备和配置文件。

### 5.1.2 FPGA配置文件的生成与下载

一旦下载链配置完成,接下来便是生成配置文件并下载到FPGA中:

1. **生成配置文件**:确保你的设计已经成功编译,然后在编译输出文件夹中找到扩展名为`.sof`的SRAM对象文件或`.pof`的编程对象文件,这将被用于下载到FPGA。

2. **启动下载器**:回到Programmer界面,点击"Add File"选择相应的配置文件。

3. **执行下载**:点击"Start"按钮,等待下载进度完成,这时FPGA将被配置。

## 5.2 硬件测试与调试

### 5.2.1 硬件调试环境的搭建

硬件测试和调试是确保FPGA功能按预期工作的关键步骤。准备你的硬件调试环境通常包括以下步骤:

1. **准备开发板**:确保FPGA开发板通电并且所有必要的模块都已经安装。

2. **连接逻辑分析仪**:逻辑分析仪是调试过程中的重要工具,用于观察和分析信号。连接好逻辑分析仪,并配置通道和采样率。

3. **设置测试信号**:可以通过外接信号或开发板上的测试按钮和开关来设置测试信号,为调试做准备。

### 5.2.2 信号的测量与分析

在硬件测试和调试中,信号的测量和分析是不可或缺的:

1. **使用Quartus II软件分析**:通过Quartus II提供的分析工具,如SignalTap逻辑分析器,可以捕获实际运行中的信号数据。

2. **手动测量信号**:使用示波器或逻辑分析仪手动测量信号电平,时序等,分析是否有错误。

3. **对比预期与实际结果**:将实际捕获的信号与仿真结果或者设计规范进行对比,找出差异。

## 5.3 实际项目中的问题诊断与优化

### 5.3.1 常见问题的诊断方法

在项目实践中,可能会遇到各种问题,如信号冲突、时序问题、资源利用率高等。诊断这些问题的方法通常包括:

1. **使用Quartus II工具**:Quartus II集成了许多诊断工具,比如Resource Property Editor、Chip Planner、以及SignalTap II等。

2. **查看编译报告和警告信息**:仔细检查编译时产生的报告和警告信息,通常能够给出问题所在。

3. **逻辑和时序仿真**:执行仿真来验证逻辑是否正确以及是否满足时序约束。

### 5.3.2 系统性能的优化案例分析

优化FPGA设计通常涉及到多个方面,下面是一个案例来说明优化的过程:

1. **资源优化**:如果设计消耗的资源过多,可能需要通过代码优化来减少资源使用,比如减少组合逻辑的深度,优化状态机设计。

2. **时序优化**:时序问题可以通过修改设计或约束来解决,比如调整寄存器的放置(placement)和路由(routing),添加适当的时序约束。

3. **功耗优化**:对于功耗敏感的应用,可以利用Quartus II的PowerPlay Power Analyzer工具来分析和降低功耗。

通过这些步骤,设计师可以有效地解决实际项目中的问题,优化FPGA设计,以达到更好的性能和效率。

0

0