【内存管理优化】:嵌入式系统中Axi Quad SPI内存使用的高效策略

摘要

本文深入探讨了嵌入式系统中Axi Quad SPI内存的基础知识、工作原理、性能参数、接口考量以及内存管理优化理论与实践。首先,我们介绍了Axi Quad SPI内存的技术规范及其在硬件和软件层面的接口设计。接着,我们探讨了内存管理的基本概念、高效内存管理的理论方法以及内存碎片化问题。在优化实践方面,我们分析了实时操作系统中的内存管理以及嵌入式系统内存性能测试。最后,通过高性能嵌入式系统的案例分析,我们研究了内存管理的常见问题与解决方案,并展望了未来内存管理技术的发展趋势。

关键字

嵌入式系统;Axi Quad SPI内存;内存管理优化;性能参数;实时操作系统;内存碎片化

参考资源链接:Xilinx AXI Quad SPI 用户指南

1. 嵌入式系统与Axi Quad SPI内存基础

嵌入式系统是现代电子技术的基石,它们通常用于处理特定的输入数据并产生相应的输出。在这些系统中,Axi Quad SPI(Advanced eXtensible Interface Quad Serial Peripheral Interface)内存起着至关重要的作用,它提供了一种快速、高效的数据传输方式。Axi Quad SPI内存与传统的SPI内存相比,能够通过四条数据线同时进行数据的读写操作,大幅提升了数据传输速率。这种高性能的特性使得它在对存储速度和响应时间要求极高的嵌入式系统应用中脱颖而出。尽管它带来了性能上的提升,但也要求设计者对Axi Quad SPI的技术规范和性能参数有深入的了解,以便正确地集成到嵌入式系统中。在接下来的章节中,我们将逐步深入探讨Axi Quad SPI内存的技术细节、工作原理以及如何在嵌入式系统中进行优化。

2. Axi Quad SPI内存工作原理及特性

2.1 Axi Quad SPI内存的技术规范

2.1.1 传输协议概述

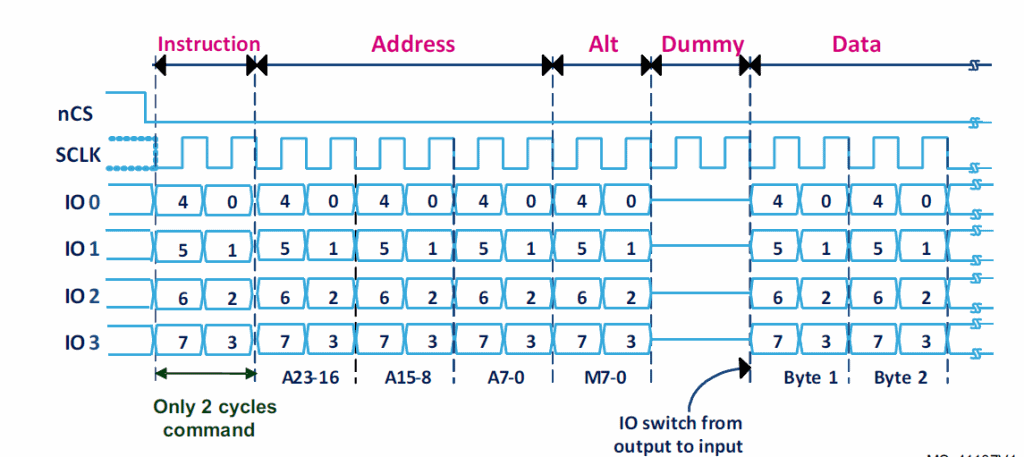

Axi Quad SPI(QSPI)是一种高速串行接口,广泛用于嵌入式系统中。它支持多种传输模式,包括单线和四线模式,以满足不同的性能和引脚数量需求。QSPI可以在一个时钟周期内同时发送和接收数据,其性能远超传统的SPI接口。

从技术层面,QSPI的传输协议构建于标准SPI协议之上,通过增加数据引脚数量来实现更宽的总线宽度和更高的数据吞吐量。在四线模式下,QSPI具有一个单独的数据输出引脚(MISO)和一个单独的数据输入引脚(MOSI),这意味着可以同时进行读取和写入操作,显著提高了传输效率。

2.1.2 时钟速率和接口特性

时钟速率是影响QSPI性能的关键因素之一。QSPI能够在很高的频率下运行,具体速度取决于设备的具体实现和系统时钟频率的限制。时钟速率决定了数据传输的速率,理论上,四线模式下QSPI的传输速率是单线SPI的四倍,因为其数据总线宽度是后者的四倍。

QSPI接口具备以下特点:

- 多IO操作:支持四线模式,可以同时进行读写操作。

- 灵活的协议:支持标准SPI命令集,并允许自定义扩展命令。

- 页面编程与擦除:允许在不发送地址的情况下,连续写入数据到内存,这进一步提升了性能。

- 低功耗:QSPI设计时考虑了低功耗需求,适用于便携式和移动设备。

2.2 内存性能参数解析

2.2.1 存取时间与带宽

内存的存取时间指的是从内存接收到读写命令到数据实际传输完成所需的时间。这个指标对于评估内存性能至关重要,因为存取时间越短,系统的响应速度就越快。

内存带宽则描述了在单位时间内能够传输的数据量。QSPI的高带宽使其成为需要大量数据吞吐的嵌入式应用的理想选择。带宽的高低通常依赖于QSPI控制器的实现效率和时钟频率。

2.2.2 内存的可靠性与耐久性

可靠性与耐久性是评估QSPI内存性能的另一重要指标。可靠性主要指的是内存能够在各种条件下正常工作,并保持数据完整性。而耐久性涉及到内存的寿命,特别是在频繁进行擦写操作时,能够保证数据保留的次数。

为了保障QSPI内存的可靠性,生产厂商通常会采取ECC(错误检查与纠正)技术来检测和纠正潜在的数据错误。耐久性方面,则通过写入循环次数(Write Cycles)来衡量,这个参数决定了内存能够承受的擦写操作的总次数,是设计高性能应用时必须考虑的因素。

2.3 硬件与软件层面的接口考量

2.3.1 控制器接口设计

设计QSPI控制器接口时,必须考虑硬件和软件协同工作的需求。控制器硬件应当支持QSPI协议的全部功能,包括时钟控制、数据读写、命令传输以及必要的信号线管理。

软件层面,驱动程序需要能够正确配置和管理QSPI接口,以支持不同类型的内存和操作模式。此外,接口设计需要考虑未来升级的灵活性,以适应可能出现的新技术和协议。

2.3.2 驱动程序与内存兼容性

为了确保QSPI内存的正确操作,驱动程序必须与QSPI内存兼容。这意味着驱动程序应识别内存的特性,并相应地进行配置。例如,它应该能够设定正确的时钟速率、接口模式、数据大小等参数。

此外,驱动程序还需要提供一套用于读写操作的标准API,使得上层应用能够无缝地使用QSPI内存。驱动程序还必须考虑到不同操作系统的内存管理差异,确保其能够在多环境下稳定运行。